# Method of Verification for Manufacturing in Sub-Wavelength Design \*

Wang Guoxiong<sup>†</sup> and Yan Xiaolang

(Institute of VLSI Design, Zhejiang University, Hangzhou 310027, China)

**Abstract:** We describe a post resolution-enhancement-technique verification method for use in manufacturing data flow. The goal of the method is to verify whether designs function as intended, or more precisely, whether the printed images are consistent with the design intent. The process modeling is described for the model-based verification method. The performance of the method is demonstrated by experiment.

Key words: verification for manufacturing; resolution enhancement technique; optical proximity correction

**EEACC:** 2550G

**CLC number:** TN 305. 7 **Document code:** A **Article ID:** 0253-4177 (2006) 05-0819-05

#### 1 Introduction

As the feature sizes of integrated circuits are shrinking to sub-100nm scales, various resolution enhancement techniques (RETs) for automatically compensating for masks are indispensable in very submicron (VDSM) IC design and manufacture. The ever increasing complexity of RETs is bringing about a dramatic increase in final layout complexity and mask production cost. Most of the time, however, the matter of post-RET goes unaddressed. This is mainly because conventional physical verification tools cannot verify post-RET designs since the new mask designs usually violate conventional IC layout design rules and because the tools do not take the photolithography step into consideration. This situation calls for a new verification method for manufacturing to ensure the correctness of post-RET layouts[1~4].

In this paper, we describe a verification method for manufacturing in detail. It employs a fast lithography simulation engine to map the modified mask to the final patterns produced on the wafer. Process modeling and some accelerated algorithms implemented in this method are illuminated in detail. The simulation results are compared with ex-

perimental data to validate the method. The results show that the proposed method is an effective and practical way to verify post-RET designs.

# 2 Method of verification for manufacturing

#### 2.1 Verification flow

Sub-wavelength manufacturing requires that optical correction errors do not violate the integrity of design. This may for instance determine whether an RET is necessary or check the usefulness and correctness of RET modifications. The merging of DRC layout engines with this kind of process simulation is creating many new applications in areas of design for manufacturing (DFM), including CD control analysis, yield loss study, and circuit performance estimation. The control files and process simulation techniques may be used to identify areas of a circuit layout that are difficult or impossible to manufacture properly.

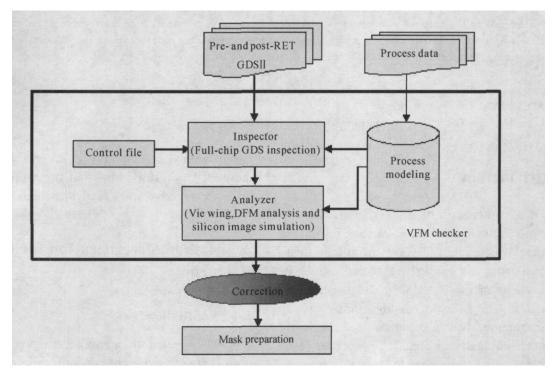

The verification for manufacturing (VFM) checker is shown in Fig. 1. The lithographic process models ,which determine the simulation accuracy, are the most important elements of the VFM checker. The objective of process modeling is

<sup>\*</sup>Project supported by the National Natural Science Foundation of China (No. 90207002) and the High Technology Research and Development Program of China (No. 2002AA1Z1460)

<sup>†</sup> Corresponding author. Email:wanggx @vlsi.zju.edu.cn Received 11 June 2005, revised manuscript received 24 January 2006

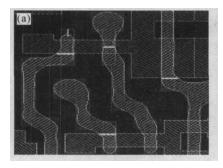

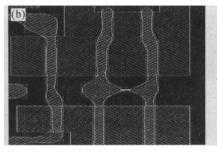

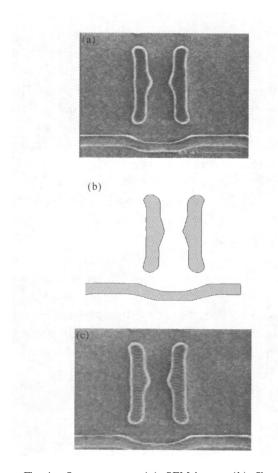

to determine the wafer location of every printed edge correctly. The simulated silicon image is used to verify the correct electrical operation of the chip and its compliance to semiconductor manufacturing rules. By using control files, the inspector should show and identify problematic areas for circuit function failure directly related to the yield due to the proximity effect-("m-dash") transistor channel length uniformity, line-end pullback, bridges for possible short circuits, and critical line widths for possible open circuits, for example. Instances of gate length uniformity, line-end pullback, and line break checking are shown in Fig. 2.

Fig. 1 Verification flow

Fig. 2 Failure checking (a) Gate length uniformity and line-end pullback; (b) Line breaking

#### 2.2 Process modeling

A critical issue in applying RETs and in post-RET verification are having a fast enough simulation engine that can predict the mask to silicon pattern transfer with reasonable accuracy.

We divide the whole lithographic model used for process simulation into three parts: an optical model, a resist development model, and an etching model.

The optical model is used to compute optical intensities near a specific point. The imaging mechanism of a stepper can be modeled by the Hopkins Eqs. (1a) and (1b)<sup>[5]</sup>.

$$I(x, y) = F^{-1}\{I(f, g)\}$$

(1b)

$$I(x,y) = c_i(F(x,y) \otimes K0_i(x,y))^2$$

(2)

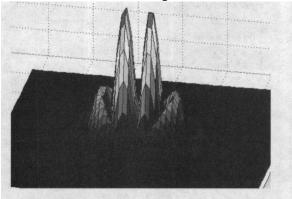

In these equations, the transmission cross coefficients (TCCs) of the optical system contain all the information of an optical system from light source to image plane and are independent of mask geometries. For a given optical system with fixed illumination, numerical aperture, defocus and other aberrations, the TCC is fixed, and the calculated TCC can then be reused for aerial image simulations of different mask patterns exposed on the same optical system. That is to say, according to the Hopkins equations, optical intensities on a wafer can be computed by a convolution of TCC and mask transmissions. Implementations in the space domain or the frequency domain can be found in simulators such as SPLAT<sup>[5]</sup>. Based on Gabor 's "reduction to principal waves", the "kernel-based convolution 15,8] method is listed in Eq. (2), in which a set of 2D kernels  $\{K0_i\}$  are generated. The sum of the products of these kernels is an approximation of the 4D transferring function of the bi-linear system. The intensity at one spatial point is calculated by summing the squares of the convolutions of the mask and these kernels. A typical convolution kernel is shown in Fig. 3.

Fig. 3 A convolution kernel

Usually, only the first few convolution kernels are required to meet the accuracy requirement. Granik *et al.* [2] discussed the number of kernels to be used and the range of ambit. This point is closely related to the accuracy of the model. Lookup tables storing the convolution values of element feature shapes and each 2D kernel are built up to avoid further direct convolution computations. Significant acceleration has been achieved by checking up these tables in calculating the intensities of sparse aerial points on different mask pattern environments<sup>[9]</sup>.

To better simulate the effects caused by the resist layer thickness and materials of different reflection factors on the wafer surface ,we have modified the purely optical model by adding some extra model parameters for describing the vertical intensity distribution inside the resist layer. Layered  $TCCs^{[5]}$  are computed and a weight average is taken ,so the controlling parameters can be empirically fitted in later model calibration.  $Z_d$  is the thickness of the resist in Eq. (3).

$$TCC_{av} = \frac{1}{Z_d} \sum_{z=0}^{Z_d} TCC(z) dz$$

(3)

In fact, the modification to the aerial image simulation includes convolving the aerial image with a 2D Gaussian filter to smear the image in a manner analogous to photo acid generator diffusion, the formula for which is given in Eq. (4). Reference [8] shows how to extend convolution kernels to model chemically amplified resist processing. This method is very efficient since the new TCC is computed once throughout the lateral diffusion, and some mask processing effects are computed in the frequency domain.

$$T(f, g, f, g) = T(f, g, f, g) \times G(f - f, g - g)$$

(4)

The etching effect is another important issue in manufacturing flow. A half-empirical variable bias model (VBM) based on shape-morphing has been developed to fully treat this effect and is given in Eq. (5). The environment surrounding a specific edge is represented by parameters such as pattern densities of different ranges, intensity slopes, and feature granularity<sup>[7]</sup>, all of which are factors in predicting the morphing bias in our VBM.

bias =

$$+/g + /g^2 + 1 +$$

$1^2 + \Phi_8 + s^2$  (5)

To get the most benefits from the process simulation, we should properly calibrate the simulation model according to the process to be characterized. That is, given a representative set of critical dimension (CD) measurements obtained from the process, we fine-tune the process model parameters so that the simulated/predicted CDs match the measured CDs well. Therefore, we need to design all kinds of test patterns. The measured data from

test chips containing groups of test patterns are input to our model calibration tool, which can automatically find optimal parameter values for both the resist development model and the etch model.

Figure 4(c) shows that the simulated result in Fig. 4(b) is very consistent with the SEM image in Fig. 4(a), which shows that the process model exactly describes the calibrated process to be characterized.

Fig. 4 On test case (a) SEM image; (b) Simulated result; (c) Superposition comparison

## 3 Experiment results

We have applied the three types of defect checking described in the above sections to a large 0. 13µm post-RET layout containing about 400,000 transistors. The total verification time is about 10min on a 1. 6 GHz PC. More than 10,000 potential defects were found. Two examples were shown in Fig. 2 for the purpose of explaining these defects.

## 4 Conclusions

The optical proximity effect (OPE) has caused great design concerns for the next several technology nodes. RETs for improving manufacturability and yield in sub-wavelength lithographic processes, such as optical proximity correction and phase shifting masks, have been introduced to address the OPE. The necessity of post-RET verification in dealing with the more aggressive uses of RETs, has been demonstrated and discussed in this paper. We have developed fast IC process simulation techniques based on empirical resist and etch models to compute silicon images of layouts as large as a full chip. The simulated silicon image is used to verify the correct electrical operation of the chip and its compliance with semiconductor manufacturing rules.

In order to reduce the manufacturing and development turn-around-time by decreasing the number of costly and time-consuming test cycles, more applications of full-chip scale manufacturing verification should be explored in future work.

#### References

- [1] Ogawa K, Ashida I, Kawahira H. New mask data verification method after optical proximity effect correction. SPIE, 2001, 4409:186

- [2] Granik Y, Cobb N, Do T. Universal process modeling with VTRE for OPC. SPIE, 2002, 4691:377

- [3] Yan Xiaolang, Chen Ye, Shi Zheng, et al. Architecture of a post-OPC silicon verification tool. Proc ASICON, 2003:1365

- [4] Malhotra V, Chang F. Verifying the 'correctness' of your optical proximity correction designs. SPIE, 1999, 3679:130

- [5] Cobb N, Zakhor A. A mathematical and CAD framework for proximity correction. SPIE, 1996, 2726:208

- [6] Lee S. LAVA web-based remote simulation: Enhancements for education and technology innovation. SPIE, 2001, 4346: 1500

- [7] Wang Guoxiong, Yan Xiaolang, Shi Zheng, et al. Design and implementation for model-based optical correction system.

Journal of Zhejiang University (Engineering Science), 2004, 38(5):521 (in Chinese) [王国雄,严晓浪,史峥,等. 基于模型的光学校正系统的设计与实现. 浙江大学学报(工学版), 2004, 38(5):521]

- [8] Shi Zheng, Wang Guoxiong, Yan Xiaolang, et al. A Kernel-based convolution method to calculate sparse aerial image intensity for lithography simulation. Chinese Journal of Semi-conductors, 2003, 24(4):357

- [9] Chen Zhijin, Shi Zheng, Wang Guoxiong, et al. A new method of 2D contour extraction for fast simulation of photolithographic process. Chinese Journal of Semiconductors, 2002, 23 (7):766(in Chinese) [陈志锦,史峥,王国雄,等.一种快速光刻模拟中二维成像轮廓提取的新方法.半导体学报,2002,23 (7):766]

## 亚波长设计中的可制造性验证方法\*

### 王国雄 严晓浪

(浙江大学超大规模集成电路设计研究所, 杭州 310027)

摘要:描述了一种采用分辨率提高技术后用于可制造性设计的验证方法.该方法的目的是验证设计功能与设计目的是否一致,更精确地说,使刻印出来的图像与设计一致.还描述了这种基于模型的验证方法的过程建模,实例说明这种方法的性能.

关键词:可制造性验证;分辨率提高技术;光学邻近校正

**EEACC:** 2550G

中图分类号: TN305.7 文献标识码: A 文章编号: 0253-4177(2006)05-0819-05

<sup>\*</sup>国家自然科学基金(批准号:90207002)及国家高技术研究发展计划(批准号:2002AA1Z1460)资助项目

<sup>↑</sup>通信作者. Email :wanggx @vlsi. zju. edu. cn