# Comparison of Body-Contact and Patterned-SOI LDMOSFETs for RF Wireless Applications

Li Wenjun<sup>1,†</sup>, Cheng Xinhong<sup>2</sup>, Song Zhaorui<sup>2</sup>, Chen Zhanfei<sup>1</sup>, Liu Jun<sup>1</sup>, and Sun Lingling<sup>1</sup>

(1 Microelectronic CAD Center, Hangzhou Dianzi University, Hangzhou 310018, China) (2 Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, Shanghai 200050, China)

Abstract: A novel patterned-SOI LDMOSFET with a silicon window beneath the p-type channel is designed and fabricated for RF power amplifier applications. It has good DC and RF characteristics, with no kink effect on the output performance, an off-state breakdown of up to 13V,  $f_T = 8$ GHz at a DC bias of  $V_G = 4$ V and  $V_D = 3.6$ V. These characteristics are better than those of body-contact SOI LDMOSFETs on the same wafer with the same process conditions.

Key words: body-contact; patterned-SOI; LDMOSFET; RF

EEACC: 2560B; 2560R

CLC number: TN386 Document code: A Article ID: 0253-4177(2006) S0-0032-04

#### 1 Introduction

The lateral double-diffused MOSFET (LD-MOSFET) has been a popular candidate in power amplifier applications. However, its high parasitic output capacitance and leakage current on bulk substrate result in lower power gain and power-aided efficiency. The silicon-on-insulator (SOI) LD-MOSFET has much lower parasitic output capacitance and leakage current, making it a better candidate for high frequency applications [1~4]. However, the buried oxide layer induces a serious floating body effect in the partially-depleted SOI device, such as a kink in the I-V characteristics, which gives rise to distortion during power operation and produces poor power efficiency<sup>[5]</sup>. In addition, application of the SOI in a high-power-integrated circuit is limited by the self-heating effect caused by the poor thermal conductivity of the insulating SiO<sub>2</sub> layers.

Body-contact technology<sup>[5]</sup>, shallow source implantation technology<sup>[6]</sup>, and patterned-SOI technology<sup>[7,8]</sup> have been proposed to eliminate the floating body effect. However, the body-contact structure reduces gate width, and shallow source implantation requires careful process control, especially for a thin-film SOI structure. Ren et al. [7] fabricated a patterned-SOI LDMOSFET

with no buried oxide beneath the source and ptype well regions, resulting in poor isolation between adjacent circuits. In addition, the process used to form patterned-SOI materials is too complex to be accepted widely. Park et al. [8] simulated a patterned-SOI structure with no buried oxide underneath the drain region, which increased the leakage current and parasitic output capacitance.

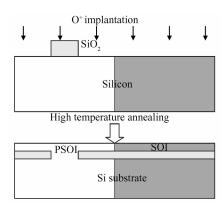

In this paper, a novel patterned-SOI (PSOI) LDMOSFET structure is proposed. The buried oxide is interrupted beneath the p-type well region, which is in a region called the silicon window. PSOI materials can be realized easily by masked SIMOX technology<sup>[9]</sup>.

#### **Device fabrication**

The main processes used to form the PSOI/ SOI materials on the same die are illustrated in Fig. 1. Thick thermal SiO<sub>2</sub> was grown on a p-type wafer ( $10 \sim 20\Omega \cdot \text{cm}$ ) and etched selectively where the buried oxide layer was to be formed. Then the oxygen ion was implanted (low dose, 100keV, with an ULVACIM-200) and annealed (1300°C for 5h). The thickness of the active silicon was about 0.  $2\mu m$ , the thickness of the buried oxide was about 0.  $1\mu m$ , and the length of the silicon window was about 0.8 $\mu$ m.

The PSOI and body-contact SOI LDMOS-

<sup>†</sup> Corresponding author. Email: lwjmln@yahoo.com.cn

Fig. 1 Local SIMOX process

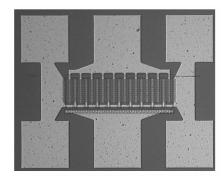

FETs were fabricated simultaneously on the same die, compatible with a standard 1µm CMOS process. Each cell has 20 fingers with a 1µm gate and finger width, for a total gate width of 1mm (Fig. 2). The gate oxide was thermally grown on the SOI wafer with a thickness of 30nm and a length of  $1\mu m$ . Boron ions  $(1.5 \times 10^{13} \text{ cm}^{-2})$ , 35keV) were implanted into the source region and annealed for 2h at 1150°C to form p-well doping. The length of the drift region was  $0.5\mu m$ . The drift region doping was achieved by a blanket implantation of phosphorus  $(2 \times 10^{12} \text{ cm}^{-2}, 50 \text{keV})$ and annealing. Oxide was deposited by TEOS and was etched selectively to define the drift region and to form a spacer wall. After the source and drain regions were made by phosphorus ion implantation, a titanium silicide was performed.

Fig. 2 Image of the LDMOSFETs with GSG pad

### 3 Results and discussion

The devices were characterized on the wafer level by examining the DC *I-V* curves with an Agilent 4156C precision semiconductor parameter analyzer and the *S*-parameters with an Agilent

E8363B PNA series network analyzer. The software we used includes ICCAP-2004 and ADS-2004A. Several differences are observed and corresponding reasons are explained in this section.

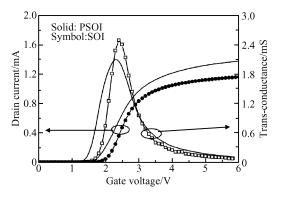

The transfer characteristics are shown in Fig. 3. The threshold voltage of the PSOI device is about 1.6V, which is 0.4V lower than that of the body-contact SOI LDMOSFET in the same B<sup>+</sup> implantation and annealing conditions because of the diffusion of the B<sup>+</sup> ions into substrate through the silicon window under the gate. As shown in Fig. 3, we can conclude that the current drive ability by the gate voltage of the PSOI LDMOSFET is better than that of the body-contact SOI device due to the lower threshold voltage of the PSOI device and the reduction of the effective gate width for the p<sup>+</sup>-type body-contact of the SOI LDMOSFET.

Fig. 3 Transfer characteristics of the devices at  $V_D = 0.1$ V

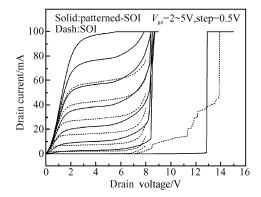

The DC output characteristics are shown in Fig. 4, in which the gate voltage varies from 2 to 5V by 0.5V steps. From Fig. 4, as Fig. 3, we can conclude that the PSOI LDMOSFET has better current drive ability by the gate voltage. For example, at the same bias condition as  $V_G = V_D =$ 3V, the drain current of the PSOI LDMOSFET is 23mA, while that of the SOI device is only 7. 2mA. The output characteristics curves in the saturation region of the PSOI LDMOSFET are very flat, proving that the floating body effect, like the kink effect, is eliminated by the novel PSOI structure we proposed, because the holes generated by the impact ionization in the neutral p-type region, can easily flow to the substrate through the silicon window. The on-state and offstate breakdown voltages of the PSOI LDMOS-

FET are 8 and 13V, respectively, which satisfy the requirements of the RF power amplifiers used in cell phones. We should explain that when the  $V_{\rm D}$  rises to 5V, the output drain current of the PSOI device is locked to 0. 1A for self-protection of the equipment.

Fig. 4 DC output characteristics of the devices

The small signal characterization was performed using coplanar waveguide GSG probes. Calibration to the probe pads was obtained using a ceramic impedance standard substrate (ISS) and the short-open-load-thru (SOLT) method.

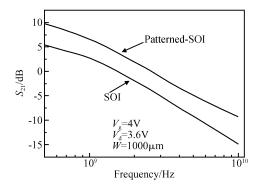

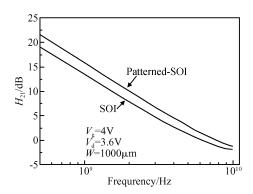

The S-parameters of the devices were measured to 10GHz. Figure 5 shows that the small signal voltage gain of the PSOI LDMOSFET is 6dB at 1GHz, which is better than that of the bodycontact SOI device. Also,  $f_{\rm T}$  was calculated by extrapolating at a slope of 20dB/Dec from  $H_{21}$  in Fig. 6. The  $f_{\rm T}$  of the PSOI LDMOSFET is about 8GHz, greater than the value of 6GHz that was obtained for the body-contact SOI device.

Fig. 5  $S_{21}$  versus frequency of PSOI and SOI LDMOSFETs

Fig. 6  $H_{21}$  versus frequency of the devices

#### 4 Conclusion

An RF power PSOI LDMOSFET was fabricated using masked SIMOX technology and a standard SOI CMOS process. This novel device has good DC and RF characteristics, with no kink effect on the output performance, an off-state breakdown of up to 13V, and  $f_{\rm T} = 8 {\rm GHz}$  at a DC bias of  $V_{\rm G} = 4 {\rm V}$  and  $V_{\rm D} = 3.6 {\rm V}$ . This is a promising technology for RF PAs in the future generations of highly integrated wireless systems.

#### References

- [1] Luo Luyang, Fang Jian, Luo Ping, et al. Breakdown characteristics of novel SOI-LDMOS with reducing field electrode and U-type drift region. Chinese Journal of Semiconductors, 2003,24(2):194(in Chinese)[罗卢杨,方健,罗萍,等. 具有降场电极 U 形漂移区 SOI-LDMOS 的耐压特性. 半导体学报, 2003,24(2):194]

- [2] Matsumoto S, Hiraoka Y, Sakai T. A high efficiency thinfilm SOI power MOSFET having a self-aligned offset gate structure for multi-gigahertz applications. IEEE Trans Electron Devices, 2001, 48(6):1270

- [3] Murari B, Bertotti F, Vignola G A. Smart power ICs. Spring-Verlag, 1996

- [4] Fiorenza J G, Antoniadis D A. RF power LDMOSFET on SOI. IEEE Electron Device Lett, 2001, 22(143):139

- [5] Matasumoto S, Hiraoka Y, Sakai T. Radio-frequency performance of a state-of-art 0. 5μm-rile thin film SOI power MOSFET.IEEE Trans Electron Devices, 2001, 48(6):1251

- [6] Fiorenza J G, Del Alamo J A. Experimental comparison of RF power LDMOSFETs on thin-film SOI and bulk silicon. IEEE Trans Electron Devices, 2002, 49(4):687

- [7] Ren Changhong, Cai Jun, Liang Y C, et al. The partial silicon-on-insulator technology for RF power LDMOSFET devices and on-chip microinductors. IEEE Trans Electron Divices, 2002, 49(12):2271

- [8] Park J M, Grasser T, Kosina H, et al. A numerical study of partial-SOI LDMOSFETs. Solid-State Electron, 2003, (47):

- [ 9 ] Dong Yemin, Wang Xi, Wang Xiang, et al. Low defect density and planar patterned SOI materials by masked SIMOX. Chem Phys Lett, 2003, 378:470

## 射频无线应用的体连接和图形化 SOI LDMOSFET 的比较

(1 杭州电子科技大学徽电子 CAD 研究所,杭州 310018) (2 中国科学院上海徽系统与信息技术研究所,上海 200050)

摘要:设计并制作了一种可应用于无线通信放大器的新型的图形化 SOI LDMOSFET.该器件沟道下方的埋氧层是断开的.测试表明,输出特性曲线没有发现明显的翘曲效应,关态的击穿电压达 13 V,在  $V_G = 4$  V 和  $V_D = 3.6$  V 时  $f_T$  为 8 GHz,直流和射频性能均优于同一芯片上相同工艺条件制备的体接触 LDMOSFET.

关键词:体接触;图形化SOI;LDMOSFET;射频

**EEACC**: 2560B; 2560R

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177(2006)S0-0032-04