Vol. 27 Supplement Dec., 2006

CHINESE JOURNAL OF SEMICONDUCTORS

# 两种自主开发的图形外延 SiGe 工艺

# 徐阳\*王飞许军刘志弘钱佩信

(清华大学微电子学研究所,北京 100084)

摘要:使用清华大学微电子学研究所研发的 UHV/CVD 系统深入研究了图形外延 SiGe 工艺,分别选用单一的 SiO $_2$  介质层和 SiO $_2$ /Poly-Si 复合介质层,作为图形外延 SiGe 单晶材料的窗口屏蔽介质,开发出了不同的实用化图形外延 SiGe 工艺.

关键词:图形外延; SiGe; 超高真空化学气相淀积

PACC: 8110B; 8115H; 6855

中图分类号: TN304.054 文献标识码: A 文章编号: 0253-4177(2006)S0-0389-03

# 1 引言

图形外延生长 SiGe 单晶材料工艺是目前世界上先进的 SiGe 集成电路工艺技术必不可少的关键工艺模块,在高性能 SiGe 微波 HBT 器件、SiGe BiCMOS 超高速电路以及 SiGe 单片微波集成电路中都有重要的应用价值.

本文使用清华大学微电子学研究所研发的超高 真空化学气相淀积(UHV/CVD)系统,开展 SiGe 单晶材料图形外延工艺的研究. 在不使用 HCl 等腐 蚀性气体的情况下[1],分别采用 SiO<sub>2</sub> 和 SiO<sub>2</sub>/Poly-Si 薄膜作为硅晶园片样品表面窗口的屏蔽介质,制 备了两种不同类型的图形外延 SiGe 单晶材料.第一 种方法是在图形窗口内的单晶 Si 表面生长出单晶 SiGe 外延层,而在图形窗口外的 SiO<sub>2</sub> 介质层上不 生长任何物质,这种外延技术通常称为选择性外延; 第二种方法是在图形窗口内单晶 Si 表面生长出单 晶 SiGe 外延层的同时,在图形窗口外的 SiO<sub>2</sub>/Poly-Si 复合介质层上也生长出一定厚度的多晶 SiGe,这 种外延技术通常称为非选择性的图形外延.对于前 者,工艺中采用的关键措施一般是通过对其生长温 度和源气体流量等工艺参数的控制,使得多晶 SiGe 在 SiO<sub>2</sub> 表面的成核时间大于单晶 SiGe 薄膜总的工 艺生长时间,从而实现选择性外延.而对于后者,由 于复合介质层 SiO<sub>2</sub>/Poly-Si 的表面是多晶形态的 Si,因而在单晶 SiGe 生长的同时,图形窗口外的介 质层上也会生成一定厚度的多晶 SiGe,并且通过控 制底层介质 SiO<sub>2</sub> 薄膜的厚度,可以使得单晶 SiGe 和 Poly-Si/Poly-SiGe 在图形窗口边缘有良好的电 学连接.这两种图形外延生长技术各具特点,都可以 应用于实用化的 SiGe 微波器件与集成电路的制作工艺.

# 2 图形外延工艺

#### 2.1 采用 SiO<sub>2</sub> 介质层的选择性外延

对于采用 SiO<sub>2</sub> 介质层的选择性外延来讲,SiO<sub>2</sub> 介质层可以通过常规的热氧化方法制备.本文采用 900°C 的湿氧工艺制备了 80nm 厚的 SiO<sub>2</sub> 介质层,然后采用光刻和刻蚀的方法形成外延生长单晶 SiGe 的窗口.需要指出的是刻蚀 SiO<sub>2</sub> 介质层时应 先采用干法刻蚀工艺,最后剩余少量的 SiO<sub>2</sub> 薄膜,则用稀氢氟酸溶液腐蚀去除,这样既保证了图形外延的窗口边缘清晰陡峭,又使得窗口内单晶 Si 表面不受到干法刻蚀的等离子体轰击损伤.将经过这样处理后的硅晶园片送入 UHV/CVD 系统中,具体的外延生长工艺条件和硅晶园片整片外延 SiGe 单晶薄膜材料的工艺流程<sup>[2]</sup>大致相同,这里不再赘述.

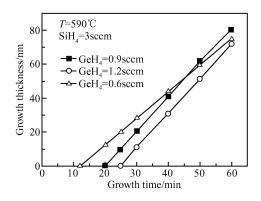

在 590°C 下采用相同的  $SiH_4$  流量和不同的  $GeH_4$  流量在  $SiO_2$  薄膜表面生长不同时间的多晶 SiGe 样品片.图 1 是 590°C 下生长的多晶 SiGe 薄膜 的厚度与生长时间的关系图,从图中可见,要在  $SiO_2$  表面生长出 SiGe 薄膜,必须满足一个最小的临界生长时间,即 SiGe 多晶颗粒在  $SiO_2$  表面的成核时间,低于这个成核时间,在  $SiO_2$  表面将不会生长出 SiGe 多晶薄膜,而超过这个成核时间,在  $SiO_2$  表面生长的 SiGe 多晶薄膜厚度将与外延生长的时间成线性关系.

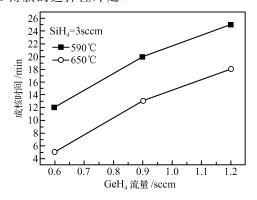

同样,还可以得到 650℃下在 SiO<sub>2</sub> 表面生长多晶 SiGe 薄膜的成核时间. 从图 2 可见,在一定的生

图 1  $SiO_2$  介质层上多晶 SiGe 厚度和生长时间的关系 Fig. 1 Thickness of the SiGe-Poly films versus the growth time for the  $SiO_2$  film

长温度下,随着 GeH4 源气体流量的增大,在 SiO2 表面生长多晶 SiGe 薄膜的成核时间也相应增大;而在相同的气体流量下,随着生长温度的提高,SiO2表面多晶 SiGe 的成核时间有明显的下降. 因此,可以通过控制反应温度和气体流量,使得在作为屏蔽层的 SiO2 上多晶 SiGe 的成核时间大于单晶 Si 表面单晶 SiGe 薄膜总的生长时间,从而实现单晶 SiGe 薄膜的选择性外延.

图 2 多晶 SiGe 成核时间与 GeH4 流量关系 Fig. 2 Nucleation time of the Poly-SiGe verus the GeH4 flow

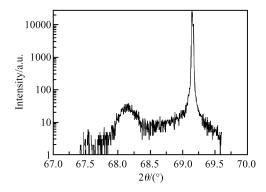

图 3 是选择性外延生长的 SiGe 样品材料的 X 射线双晶衍射(DCXRD)摇摆曲线. 由于 X 射线聚焦的光斑尺寸较大,覆盖了多个外延窗口,因此图中的 SiGe 峰说明了图形内生长的是单晶 SiGe 材料.

# 2.2 采用 $SiO_2/Poly$ -Si 复合介质层的非选择性图形外延

对于  $SiO_2/Poly-Si$  复合介质层的非选择性图形外延工艺,先要采用热氧化方法生长一定厚度的  $SiO_2$ ,然后再利用 LPCVD 工艺淀积一层 100nm 厚的多晶硅(Poly-Si),并对多晶硅进行浓硼注入和退火处理.接下来光刻并刻蚀出用于外延生长的图形

图 3 选择性外延 SiGe 样品的 DCXRD 测试曲线 Fig. 3 DCXRD curve of the SiGe sample by selective epitaxial growth technology

窗口,在干法刻蚀多晶硅之后,同样采用干法刻蚀与湿法腐蚀相结合的方法刻蚀  $SiO_2$ ,样品经这样的处理后送入 UHV/CVD 系统中,仍然采用和硅晶园片整片外延 SiGe 单晶薄膜材料相类似的外延生长工艺流程进行 SiGe 薄膜非选择性的图形外延生长.

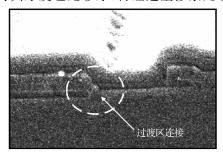

大量的实验结果表明,在这种非选择性的图形外延生长工艺中,图形窗口外复合介质层 Poly-Si上的多晶 SiGe (Poly-SiGe)与图形窗口内的单晶 SiGe 几乎是同时开始生长的,但在 590℃的生长条件下,多晶 SiGe 的生长速率约为单晶 SiGe 生长速率的 50%.图形内单晶 SiGe 与介质层上 Poly-Si/Poly-SiGe 的过渡与连接是图形外延工艺中需要重点解决的关键问题.研究发现,过渡连接区的宽度通常是由单晶 SiGe 薄膜的生长厚度所决定的,而在一定的单晶 SiGe 薄膜厚度下,要想获得比较好的电学连接,就需要严格控制 SiO₂介质层的厚度和湿法腐蚀 SiO₂时的过腐蚀量.

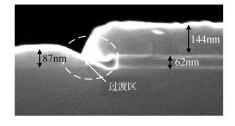

图 4 是一个实验样品的过渡连接区的剖面 SEM 照片.为了更好地观察过渡区的生长情况,对 SiO<sub>2</sub> 层的湿法腐蚀增加了一定的过腐蚀量,使得多

图 4 图形外延过渡区 SEM 照片

Fig. 4 SEM photo of the intergradations of the patterned epitaxial growth

晶 Si 与单晶 Si 衬底之间形成了较明显的悬臂结构. 研究结果表明,过渡区的宽度与单晶 SiGe 薄膜的厚度成正比例关系,即单晶 SiGe 层越薄,则过渡区也就越窄,因此采用较薄的单晶 SiGe 薄膜可以获得更

小的过渡区,从而在制作器件时就越容易消除过渡 区对于器件特性所带来的漏电等不利影响.

另一方面,为了使得图形窗口内的单晶 SiGe 和图形窗口外的多晶 SiGe 之间有良好的电学连接,要求同时起引线作用的过渡区必须具有一定的厚度.这除了与单晶 SiGe 薄膜的生长厚度有关外,还与复合介质底层 SiO<sub>2</sub> 薄膜的厚度有很大的关系.工艺实验的结果表明,较薄的 SiO<sub>2</sub> 层通常可以获得更好的连接,但是考虑到 SiO<sub>2</sub> 上 Poly-Si/Poly-SiGe 会形成场板结构,从而在下面的硅衬底中产生出一定的感生电荷,所以此 SiO<sub>2</sub> 层也不宜过薄.本文的研究结果表明,SiO<sub>2</sub> 厚度为单晶 SiGe 薄膜生长厚度的90%左右即可.依据这样的工艺设计原则,本文制作的实验样品获得了较好的过渡区电学连接.通过SEM 照片(见图 5),可以看到过渡区的宽度非常窄,同时其厚度也足够厚,再经过重掺杂处理,对于

图 5 过渡区连接处的 SEM 照片 Fig. 5 SEM photo of the intergraded connection

自对准的 SiGe HBT 器件来说,完全可以获得更小的基区串联电阻.

# 3 结论

详细介绍了通过控制反应生长温度和 GeH4 源 气体流量,在利用 SiO2 作为窗口介质的硅片上,选择性外延生长 SiGe 的工艺流程.这种工艺具有不使用 HCl 等腐蚀性气体,与现有的 UHV/CVD 外延系统工艺兼容的优点;但是由于其对 GeH4 流量较敏感,因此目前尚不适合用于制备 Ge 组分渐变的单晶 SiGe 薄膜.本文还对采用 SiO2/Poly-Si 复合介质的非选择性图形外延 SiGe 工艺进行了研究,讨论了过渡区的宽度与单晶 SiGe 薄膜生长厚度之间的关系;并通过选择复合介质底层 SiO2 薄膜的厚度与单晶 SiGe 薄膜厚度的比例关系,使得单晶 SiGe 薄膜和多晶 Si 以及多晶 SiGe 之间具有很好的电学连接.

#### 参考文献

- [1] Oda K, Ohuea E, Tanabeb M, et al. SiGe selective epitaxial growth for ultra-high-speed self-aligned HBTs. Thin Solid Films, 2000, 369, 358

- [2] Jia Hongyong, Lin Huiwang, Chen Peiyi, et al. Epitaxy of SiGe HBT structure by high vacuum/rapid thermal processing/chemical vapor deposition. Chinese Journal of Semiconductors, 2001, 22(3):251

# Two Kinds of Patterned SiGe Epitaxial Growth Technologies

Xu Yang<sup>†</sup>, Wang Fei, Xu Jun, Liu Zhihong, and Qian Peixin

(Institute of Microelectronics, Tsinghua University, Beijing 100084, China)

**Abstract:** We lucubrate on the patterned SiGe epitaxial growth technology based on Tsinghua's UHV/CVD system. We develop different applied technologies of the patterned SiGe epitaxial growth by using the SiO<sub>2</sub> single-film or SiO<sub>2</sub>/Poly-Si double-film as the patterned-window isolated layer.

Key words: patterned epitaxial growth; SiGe; UHV/CVD

PACC: 8110B; 8115H; 6855

**Article ID:** 0253-4177(2006)\$0-0389-03