## Two-Stage Driving Circuit for One-Chip TFT-LCD Driver IC\*

Gao Wu, Wei Tingcun<sup>†</sup>, and Gao Deyuan

(Aviation Microelectronics Center, Northwestern Polytechnical University, Xi'an 710072, China)

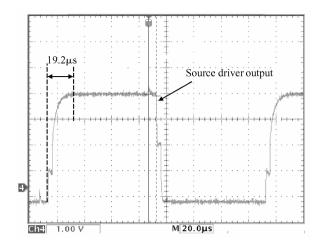

Abstract: A two-stage driving circuit of a one-chip TFT-LCD driver IC for portable electronic devices is proposed. The driving buffers of the new circuit are built in the  $\gamma$ -correction circuit rather than in the source driver. The power consumption, die area, and driving capability of the driving circuit are discussed in detail. For a two-stage driving circuit with 13 driving buffers, the settling time of the driving voltage within 0.2% error is about 19.2 $\mu$ s when 396 pixel-loads are driven by the same grayscale voltage. The quiescent current of the whole driving circuit is  $518\mu$ A, and the power consumption can be reduced by 77%. The proposed driving circuit is successfully applied in a  $132RGB \times 176$ -dot, 260k color one-chip driver IC developed by us for the TFT-LCD of mobile phone, and it can also be used in other portable electronic devices, such as PDAs and digital cameras.

Key words: TFT-LCD; source driver; γ-correction; grayscale voltage

**EEACC:** 1205; 1220

#### 1 Introduction

With the rapid development of VLSI and mobile communication technologies, portable electronic devices, such as cell phones and PDAs have been widely used in people's daily life. Because TFT-LCD has many advantages such as high luminance, high image quality, fast response time, and low power consumption, it is widely applied in all kinds of portable electronic devices. The TFT-LCD driver IC is one of the key parts in LCM (LCD module), which directly affects the image quality and power dissipation of LCM.

Currently, TFT-LCD driver ICs can be classified into two kinds. One is the multi-chip solution applied for large TFT-LCD panels, which consists of a source driver IC, gate driver IC, TCON IC, etc, and in which driving buffers are connected to the outputs of the source driver [1]. The other is the one-chip solution applied for portable electronic devices that use a battery power supply [2~5], for which all functional blocks used for large TFT-LCD driver ICs are integrated in a one-chip driver IC in order to reduce die area and power consumption. Small die area can decrease the chip cost, and low power dissipation can

lengthen battery's working life.

The settling time of the source driver output voltage is an important factor for a one-chip driver IC. A large driving ability can yield better image quality. Currently, for 260k color TFT-LCD one-chip driving ICs, the power consumption is under 5mW in the module; the die area is about 20.69mm  $\times$  2.47mm; and the settling time is less than  $35\mu s^{[3\sim4]}$ . However, the circuits of driver ICs must be optimized further in order to achieve lower power consumption and chip cost.

In this paper, we proposed a two-stage driving circuit for one-chip TFT-LCD driver IC. The driving buffers are placed in the part outputs of  $\gamma$ correction circuit rather than in the every outputs of it, and thus the number of driving buffers is reduced greatly as compared with the conventional driving circuit. Considering the trade-off for the power consumption, the die area and the driving capability, a typical two-stage driving circuit with 13 driving buffers is designed which is satisfying the requirement of driving circuit with 13 driving buffers is designed which is satisfying the requirement of driving capability. The designed driving circuit is successfully applied in 132RGB × 176dot,260k color one-chip driver IC developed by us for TFT-LCD of mobile phone.

<sup>\*</sup> Project supported by the National High Technology Research and Development Program of China (No. 2005AA1Z1193), the Xi'an-Applied Materials Innovation Fund(No. XA-AM-200511), and the Graduate Starting Seed Fund of Northwestern Polytechnical University(No. Z200648)

<sup>†</sup> Corresponding author. Email: weitc@nwpu.edu.cn

### 2 Driving circuits of one-chip driver IC

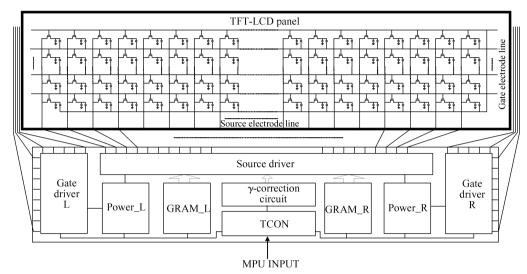

A block diagram of an LCM using a one-chip driver  $IC^{[2\sim5]}$  is shown in Fig.1. The driving buff-

er of a one-chip driver IC is usually connected to the output of the  $\gamma$ -correction circuit while the source driver block is only used as a digital-to-analog converter.

Fig. 1 Block diagram of LCM using one-chip driver IC

The timing controller (TCON), gate driver, source driver,  $\gamma$ -correction circuit, DC-DC converters, and graphic RAM are typical circuit blocks for a one-chip driver IC. TCON generates controlling signals and timing clocks for the whole driver IC. The gate driver and source driver generate line driving voltages and column driving voltages, respectively. The  $\gamma$ -correction circuit generates grayscale voltages corresponding to input digital display data. The DC-DC converters generate operational voltages of all blocks and driving voltages for the panel. Graphic RAM is used to store one frame of digital display data.

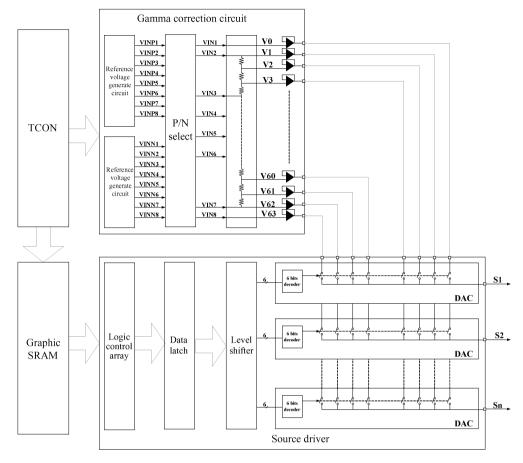

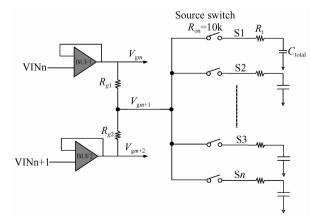

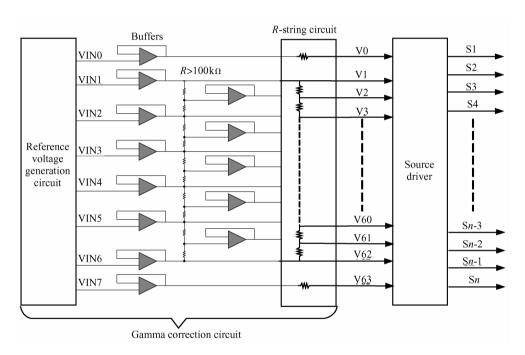

In the one-chip driver IC, the  $\gamma$ -correction circuit generates full-scale grayscale voltages appended with driving buffers at the outputs, and the source driver selects the proper grayscale voltages by D/A converter according to input digital display data and then outputs to the LCD panel to display the color images. Figure 2 shows the conventional driver architecture of a one-chip driver IC for a small TFT-LCD.

In Fig. 2, the driving voltage buffers are included in the  $\gamma$ -correction circuit and the source driver is only used to select the grayscale voltages. This is different from the source driver IC for a large TFT-LCD panel where the driving voltage buffers are included in every source driver [6]. The

number of driving buffers in Fig. 2 is smaller than that of the source driver IC for a large TFT-LCD panel so that the die area and power dissipation of the driver IC can be reduced greatly.

# 3 Load analysis of TFT-LCD panel and driving capability requirement

#### 3.1 Load analysis of TFT-LCD

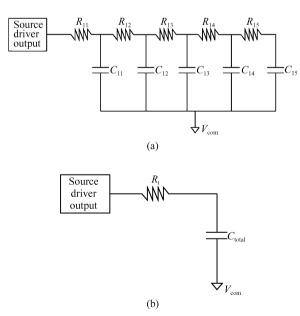

The equivalent load of one pixel in a TFT-LCD panel can be modeled by a five-stage serial RC circuit or a one-stage RC circuit [7], as shown in Figs. 3 (a) and (b). A one-stage RC equivalent circuit is suitable for a small TFT-LCD panel because the area of sub-pixels is small and the length of ITO and metal (Cr/A1) line is short as compared with large TFT-LCD.  $R_{\rm t}$  is the equivalent resistance when the TFT is on, and  $C_{\rm total}$  is the equivalent capacitance of the sub-pixel. The values of  $R_{\rm t}$  and  $C_{\rm total}$  are different for all sizes of TFT-LCD panels, but for a 50mm TFT-LCD panel, the equivalent RC loads of one sub-pixel are about  $R_{\rm t}$  =  $10{\rm k}\Omega$  and  $C_{\rm total}$  =  $20{\rm pF}$ .

In Fig. 2, the load impedances of the driving voltage buffers are different from each other depending on the input digital display data. For the best situation, the digital display data are different from each other so that every grayscale voltage

Fig. 2 Conventional driver architecture of one-chip driver IC for small TFT-LCD

Fig. 3 Load models of TFT-LCD panel (a) Five-stage serial RC circuit; (b) One-stage RC circuit

(also every driving buffer) drives only one subpixel, and the load impedance of every driving buffer is  $R_t$  and  $C_{total}$ . However, in the worst situation, the digital display data all have the same value so that the whole line of sub-pixels are driven by one grayscale voltage (also by one driving buffer). If there are N sub-pixels in a line, then N sub-pixels are paralleled for a driving buffer, so that the total load impedance of one driving buff-

er is

$$R_t^N = \frac{R_t}{N}$$

and  $C_{\text{total}}^N = NC_{\text{total}}$ .

#### 3. 2 Driving capability requirement

The settling time of the grayscale voltage is the sum of the SR limiting settling time ( $T_{\rm SR}$ ) and the small signal settling time ( $T_{\rm SS}$ )<sup>[6]</sup>. In this paper, the settling time of the driving voltage is defined as the time that the output voltage of the driving buffer takes to rise from zero to the grayscale voltage  $V_{\rm g}$  within  $\pm$  0.2% error at the worst load condition ( $R_{\rm t}^N$  and  $C_{\rm total}^N$ ).

For a one-chip TFT-LCD driver IC,  $T_{\rm S}$  is determined by the minimum row period  $T_{\rm row,min}$  and maximum charge sharing time  $T_{\rm charge\_share,max}$ ; their relationship is as follows<sup>[4,5]</sup>:

$$T_{\rm s} < T_{\rm row,min} - T_{\rm charge\_share,max}$$

(1)

This relationship ensures that the liquid pixels and storage capacitor can be charged to grayscale voltage in a row period.

For a  $132 \text{RGB} \times 176\text{-dot}$ , 260 k color one-chip driver IC of a TFT-LCD used for a mobile phone,  $T_{\text{row,min}} - T_{\text{charge\_share,max}} = 40 \mu \text{s}$ , We need  $T_{\text{s}} < 30 \mu \text{s}$  ( $10 \mu \text{s}$  for margin), and  $T_{\text{SR}} < 20 \mu \text{s}$ ,  $T_{\text{SS}} < 10 \mu \text{s}$ .

# 4 Driving architecture with buffers built into the γ-correction circuit

# 4. 1 One-stage driving architecture with 8 driving buffers

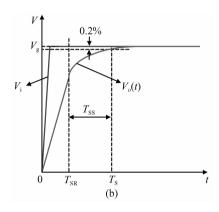

In order to further reduce the power consumption and the die area, the circuit shown in Fig. 2 can be simplified to the one-stage architec-

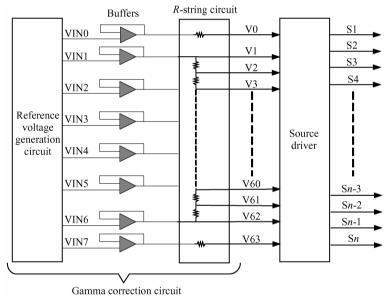

ture shown in Fig. 4 with 8 built-in buffers in the  $\gamma$ -correction circuit, where the driving buffers are moved from the outputs of the  $\gamma$ -correction circuit to the outputs of 8 reference voltages circuit, and the number of driving buffers is reduced from 64 to 8.

#### 4. 2 Load analysis of one-stage driving architecture

In this architecture, 8 reference voltages (VIN0 $\sim$ VIN7) are driven by 8 OPAMP buffers and are then applied to the resistance-string circuit to generate 64 level grayscale voltages. The loads of buffers consist of three parts; the equivalent loads of the TFT-LCD panel, the on-resistance of the 6-bit DAC, and the resistance in resistance-string of the  $\gamma$ -correction circuit. The loads of the buffers are different when digital display data from the MPU is changed.

Fig. 4 One-stage driving architecture with 8 built-in driving buffers

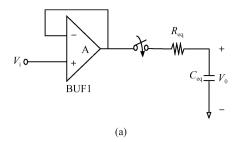

In the worst load situation, the loads for whole lines of pixels are driven by one grayscale voltage  $V_{gm+1}$ , as shown in Fig. 5. VINn and VIN n+1 are two adjacent reference voltages, and  $R_{\rm gl}$  and  $R_{\rm g2}$  are the equivalent resistances in the resistance-string. For BUF1, the circuit shown in Fig. 5 can be equivalently simplified to the circuit shown in Fig. 6(a).

If the on-resistance of the analog switch in the source driver is  $R_s$ , the output impedance of BUF1 is

$$Z_{L} = \frac{(NR_{g1} + R_{s} + R_{t})R_{g2}C_{total}s + R_{g2}}{[N(R_{g1} + R_{g2}) + R_{s} + R_{t}]C_{total}s + 1} = R_{eq} + \frac{1}{C_{eq}s}$$

Fig. 5 Equivalent load model of one-stage driving architecture in the worst situation

Fig. 6 Load equivalent circuit of BUF1 and its step voltage response (a) Equivalent circuit; (b) Step voltage response

When  $R_{\rm g2}$  is large enough, the quiescent current of  $R_{\rm g2}$  is very little as compared with the charging current of loads, and so  $R_{\rm g2}$  can be ignored, thus we have,

$$R_{\rm eq} = R_{\rm g1} + \frac{R_{\rm s} + R_{\rm t}}{N} \tag{3}$$

$$C_{\text{eq}} = NC_{\text{total}}$$

(4)

Thus the time constant  $\tau$  for the output load of BUF1 is

$$\tau = R_{eq} C_{eq} = (NR_{g1} + R_s + R_t) C_{total}$$

(5)

#### 4.3 Settling time analysis

For the circuit shown in Fig. 6 (a),  $C_{\rm eq}$  is charged by the output voltage of the buffer through the resistance  $R_{\rm eq}$  when the switch is ON. The capacitor charging process when the input is applied by a step voltage can be considered as follows. From start to  $T_{\rm SR}$ , the driving buffer experiences a slew rate process, and the voltage of  $C_{\rm eq}$  rises with a constant slope of SR. When  $t > T_{\rm SR}$ , BUF1 operates under a linear small signal process, the voltage of  $C_{\rm eq}$  rises exponentially until the output voltage  $V_{\rm o}$  equals the input voltage  $V_{\rm i}$ , as shown in Fig. 6 (b).

Assuming the driving buffers are two-stage OPAMPs with bias current  $I_{\rm bias}$  and open loop gain A, and a Miller capacitor  $C_{\rm c}$  is used to improve

the phase margin, then the slew rate can be written as [8,9]

$$SR = \frac{dV_o}{dt} = \frac{I_{bias}}{C_c + C_{eq}}$$

(6)

Because the slew rate process is over at  $T_{\rm SR}$ , the output voltage of BUF1 at this time is

$$V_{\rm ol} = SR \times T_{\rm SR} \tag{7}$$

When  $t > T_{SR}$ , the driving buffer is assumed to be in a linear small signal process, and we have

$$\frac{V_{o}(s)}{V_{i}(s)} = \frac{A}{1+A} \times \frac{1}{1+\tau s}$$

(8)

Thus the step voltage response can be obtained by inverse Laplace transform as

$$V_{o} = V_{i} \frac{A}{1+A} (1 - e^{-\frac{t}{\tau}}) U(t)$$

(9)

Then the voltage of capacitor  $C_{\rm eq}$  can be obtained as

$$V_{o}(t) = \begin{cases} SR \times t, & 0 < t \leq T_{SR} \\ V_{ol} + (V_{g} - V_{ol}) \frac{A}{1 + A} (1 - e^{-\frac{t - T_{SR}}{\tau}}), t > T_{SR} \end{cases}$$

(10)

At time  $T_s$

$$\frac{\mid V_{o}(t) - V_{g} \mid}{V_{g}} \times 100\% \leqslant 0.2\%$$

(11)

We have

$$T_{\rm S} = T_{\rm SR} + \tau \ln \left[ \frac{\left(1 - \frac{V_{\rm ol}}{V_{\rm g}}\right) \frac{A}{1 + A}}{\left(1 - \frac{V_{\rm ol}}{V_{\rm g}}\right) \frac{A}{1 + A} - 0.998 + \frac{V_{\rm ol}}{V_{\rm g}}} \right]$$

(12)

From Eq. (12), it is observed that  $T_{\rm S}$  depends on A, SR,  $\tau$  and  $V_{\rm g}$ . When A is large enough, we have

$$T_{\rm S} = T_{\rm SR} + \tau \left[ \ln \left( 1 - \frac{V_{\rm ol}}{V_{\rm g}} \right) + 6 \right]$$

(13)

According to Eq. (13),  $T_s$  is determined mainly by  $T_{\rm SR}$ ,  $\tau$ , and  $V_{\rm ol}/V_{\rm g}$ , and  $T_{\rm S}$  is larger when  $T_{\rm SR}$  and  $\tau$  are larger or  $V_{\rm ol}/V_{\rm g}$  is less. For fixed  $V_{\rm ol}/V_{\rm g}$ ,  $T_{\rm SR}$  is the main factor of  $T_{\rm S}$ , so we can increase the SR of the driving buffer to reduce  $T_{\rm s}$ . Further,  $\tau$  is another important factor for reducing  $T_{\rm s}$ . Since  $C_{\rm total}$  and  $R_{\rm t}$  are the load of the TFT-LCD panel and cannot be changed, reducing the values of  $R_{\rm s}$  and  $R_{\rm gl}$  is the only way to reduce  $\tau$  according to Eq. (4).

An analog switch with a 6bit decoder circuit can be used in the source driver so as to obtain a low  $R_s$ . However, there are two methods to reduce  $R_{\rm gl}$ : one is reducing the value of unit resistance in the grayscale voltage generating circuit (resist-

ance-string), and the other is changing the topology of the driving circuit. However, if the value of unit resistance is reduced, the quiescent current of the resistance-string circuit will be increased, which is not desirable for a TFT-LCD driver IC. Consequently, it is necessary to change the driving buffers' architecture to increase  $T_{\rm s}$  but without increasing the power dissipation.

The driving buffers' architecture can be changed by adding additional driving buffers into the  $\gamma$ -correction circuit at the proper place of the resistance-string circuit. For example, in the circuit shown in Fig. 5, another voltage driving buffer can be added between BUF1 and BUF2. Its input (or output) voltage is between VIN n and VIN

n+1, and as a result, the load conditions of the driving buffers are changed and  $R_{\rm gl}$  is reduced.

#### 4.4 Two-stage driving circuit with 13 driving buffers

The properties of the driving architecture shown in Fig. 4 can be improved by increasing the number of driving buffers. As shown in Fig. 7, five additional buffers are added into the  $\gamma$ -correction circuit, which is called a two-stage driving architecture. In this new driving architecture, the number of reference voltages appended with driving buffers at the outputs is increased from 8 to 13, so the  $R_{\rm gl}$  of each buffer is reduced, and also  $T_{\rm s}$  can be expected to decrease.

Fig. 7 Two-stage driving architecture with 13 driving buffers

The two-stage driving architecture is formed as follows. The 8 first-stage driving buffers are added at each of the outputs of the 8 reference voltages (VIN0  $\sim$  VIN7), two large resistances (larger than  $100k\Omega$ ) for voltage division are connected between outputs of two adjacent buffers for the middle reference voltages (VIN1  $\sim$  VIN6), and then the 5 second-stage driving buffers are added between the division resistances and grayscale voltage generating circuit (resistance-string). Then the outputs of the second-stage buffers are connected to the resistance-string circuit accordingly without changing the grayscale voltage

ges division ratio. With the increase of the unit resistance in the grayscale voltage generating circuit (resistance-string), the quiescent current will be reduced, but the circuit area will increase, and the resistance load of the buffers will increase so that the settling time will be affected. A tradeoff between the unit resistance value (power consumption and die area) and the settling time needs to be made.

#### 5 Simulation and measurement results

The driving circuits using the two-stage driv-

ing architecture proposed in this paper are designed and simulated by HSPICE using a  $0.25\mu m$  CMOS process. The parameters of  $R_t$  and  $C_{\text{total}}$  in the load model are  $10 \text{k}\Omega$  and 20 pF, respectively. The simulation results for 3 kinds of driving architectures in the worst load situation are shown in Table 1.

Table 1 Simulation results for 3 kinds of driving architecture

| Simulation condition                          |                 |             | Simulation results |                  |             |             |             |             |

|-----------------------------------------------|-----------------|-------------|--------------------|------------------|-------------|-------------|-------------|-------------|

| worst load situation $T = 27^{\circ}\text{C}$ |                 |             | 8 buffers          |                  | 13 buffers  |             | 64 buffers  |             |

| $R_s + R_t$                                   | $C_{\rm total}$ | $R_{\rm g}$ | $T_{\rm s}$        | $I_{\mathrm{s}}$ | $T_{\rm s}$ | $I_{\rm s}$ | $T_{\rm s}$ | $I_{\rm s}$ |

| $/k\Omega$                                    | /pF             | $/\Omega$   | $/\mu s$           | $/\mu A$         | $/\mu s$    | $/\mu A$    | $/\mu s$    | $/\mu A$    |

| 10 + 5                                        | 20              | 135/4       | 13.4               | 764.2            | 9.4         | 922.1       | 6.6         | 2707        |

|                                               |                 | 135/3       | 16.3               | 629.1            | 11.3        | 787.6       | 6.6         | 2674        |

|                                               |                 | 135/2       | 22.1               | 494.1            | 15.0        | 653.1       | 6.5         | 2404        |

|                                               |                 | 135         | 30.0               | 359.0            | 26.0        | 518.6       | 6.6         | 2269        |

Note:  $R_{\Box} = 135\Omega$ ,  $R_{g}$  is the unit resistance of R-string circuit,  $T_{s}$  is the settling time, and  $I_{s}$  is the quiescent current.

From the simulation results shown in Table 1, we can draw the following conclusions.

First, for a given driving architecture, the settling time and quiescent current consumption are affected by the value of unit resistance of the *R*-string circuit. With the decrease of the value of unit resistance, the settling time decreases but the quiescent current consumption is increases.

Second, for the given value of unit resistance, the settling time and quiescent current consumption are different for different driving architectures. With the increase of the number of driving buffers, the settling time decreases but the quiescent current consumption increases.

Third, for a two-stage driving architecture with 13 buffers, the settling time and power dissipation are the tradeoff of the values for the architecture with 8 buffers and 64 buffers. When  $R_{\rm g}=135\Omega$ , we have  $T_{\rm s}=26\mu{\rm s}$  and  $I_{\rm s}=518.6\mu{\rm A}$ ,  $T_{\rm s}$  satisfies our design specifications, and the power dissipation can be reduced by 77% as compared with the conventional architecture with 64 buffers.

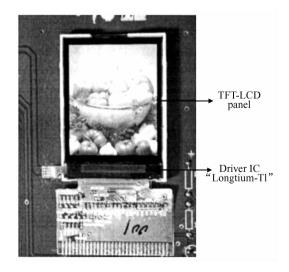

The two-stage driving architecture proposed in this paper has already been successfully applied in a 132RGB×176-dot,260k color one-chip driver IC (named as "Longtium-T1") developed by us for the TFT-LCD of mobile phone.

The measured waveform of the source driver output voltage of the driver IC using 13 driving buffers and  $R_g = 135\Omega$  is shown in Fig. 8. The set-

Fig. 8 Measured waveform of source driver output

tling time of the grayscale voltage from 0.8 to 5.0V is about 19.2 $\mu$ s, which satisfies the design requirement. It can be seen that the measured settling time is less than the simulated one ( $T_s = 26\mu$ s) shown in Table 1. This is because the loading parameters of the TFT-LCD panel such as  $R_t$  and  $C_{total}$  used in the simulation are larger than the real parameters.

The test results of the LCM using this driver IC ("Longtium-T1") are shown in Fig. 9. It is shown that high quality display images are achieved, in which the two-stage driving circuit proposed is used.

Fig. 9 Photo of LCM using longtium-T1 driver IC

#### 6 Conclusions

A two-stage driving buffer architecture of a one-chip TFT-LCD driver IC for portable elec-

tronic devices has been proposed. For this new architecture, the power dissipation and the die area of the driver IC has been greatly reduced by reducing the number of driving buffers.

Optimization of the two-stage driving architecture can be carried out in order to drive different sizes of TFT-LCD panels and to reduce the power dissipation and the die area further, and even three-stage or multi-stage driving architectures can be considered.

#### References

- [1] Choi I, Shim H, Chang N. Low power color TFT-LCD display for hand held embedded systems. Proc ISLPED, 2002: 112

- [ 2 ] Kim B S.Ko J S, Lee W H. Low power 260k color TFT LCD driver IC. ETRI Journal, 2003, 25(5): 288

- [3] Kim B S.Kim Y G. Hong S Y. Low power 260k color TFT LCD one-chip driver IC. 5th International Symposium on

- Quality Electronic Design Proceedings, 2004:126

- [4] RENESAS. HD66773RSpecification: 262.144-color, 132 × 176-dot graphics controller driver for TFT LCD panels. JUN. 21. 2003, Rev1. 20:84

- [5] Wei Tingcun, Ding Xingbo, Gao Deyuan. Output buffer circuits for medium or small size TFT-LCD driver IC. Chinese Journal of Semiconductors, 2006, 27(12): 2214 (in Chinese) [魏廷存,丁行波,高德远.中小屏幕 TFT-LCD 驱动芯片的输出缓冲电路.半导体学报,2006,27(12): 2214]

- [6] Itakura T, Minamizaki H, Saito T. A 402-output TFT-LCD driver IC with power control based on the number of colors selected. IEEE J Solid-State Circuits, 2003, 38(3):503

- [7] Shur M, Jacunski M, Slade H, et al. Analytical models for amorphous and polysilicon thin film transistors for high definition display technology. Journal of Society for Information Display, 1995, 3(4):223

- [8] Razavi B. Design of analog CMOS integrated circuits. Xi'an: Xi'an Jiaotong University Press, 2003 (in Chinese) [毕查德·拉扎维.模拟 CMOS 集成电路设计.西安:西安交通大学出版社,2003]

- [9] Allen P E, Holberg D R. CMOS analog circuit design. 2nd ed. Beijing: Publishing House of Electronics Industry. 2005

### TFT-LCD 驱动芯片的二级驱动电路\*

高 武 魏廷存 高德远

(西北工业大学航空微电子中心,西安 710072)

摘要:针对单芯片集成的 TFT-LCD 驱动芯片的特性,提出了在  $\gamma$  校正电路中加入两级驱动 Buffer 的驱动电路结构,以及提高其驱动能力的有效措施.对于具有 13 个驱动 buffer 的二级驱动电路,当由一个灰度电压驱动全部 396 个像素单元时,驱动电压的最大安定时间约为 19.  $2\mu$ s;静态消耗电流为  $518\mu$ A,与传统的 64 个驱动 buffer 电路相比,其功耗减小了 77%.本文的设计结果已成功应用于  $132RGB \times 176$  分辨率、26 万色彩色显示手机用 TFT-LCD 驱动芯片中,其也可用于 PDA、数码相机等其他便携电子设备的显示驱动.

关键词: TFT-LCD; 驱动电路; γ校正; 灰度电压

EEACC: 1205; 1220

中图分类号: TN432 文献标识码: A 文章编号: 0253-4177(2007)03-0385-08

<sup>\*</sup> 国家高技术研究发展计划(批准号:2005AA1Z1193),西安应用材料创新基金(批准号:XA-AM-200511)和西北工业大学研究生创业种子基金(批准号:Z200648)资助项目