# A Novel Equivalent Circuit Model of GaAs PIN Diodes\*

Wu Rufei<sup>1,†</sup>, Zhang Haiying<sup>1</sup>, Yin Junjian<sup>1</sup>, Li Xiao<sup>2</sup>, Liu Huidong<sup>1</sup>, and Liu Xunchun<sup>1</sup>

(1 Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China) (2 University of Sichuan, Chengdu 610064, China)

**Abstract:** A novel equivalent circuit model for a GaAs PIN diode is presented based on physical analysis. The diode is divided into three parts; the  $p^+$   $n^-$  junction, the i-layer, and the  $n^ n^+$  junction, which are modeled separately. The entire model is then formed by combining the three sub-models. In this way, the model's accuracy is greatly enhanced. Furthermore, the corresponding parameter extraction method is easy, requiring no rigorous experiment or measurement. To validate this newly proposed model, fifteen groups of diodes are fabricated. Measurement shows that the model exactly represents behavior of GaAs PIN diodes under both forward and reversely biased conditions.

Key words: GaAs PIN diodes; model; parameter extraction

**PACC:** 7340L **EEACC:** 2560B

#### 1 Introduction

Monolithic microwave integrated circuits (MMIC) are widely used in microwave control applications such as antenna switches, phase shifters, and attenuators as a result of recent progress in MMIC technology<sup>[1]</sup>. Compared to HEMT, GaAs PIN diodes have the advantage of higher cut-off frequency, higher power-handling capability, lower conductive resistance, and lower off-state capacitance, leading to their wide use in MMIC control circuits<sup>[2,3]</sup>. To design such circuits, developing the device model of GaAs PIN diodes is essential, since it is the dominant factor in determining the accuracy of circuit design.

There are two main kinds of models: equivalent circuit models and physical models. In papers concerning equivalent circuit models, GaAs PIN diodes are characterized mainly with shunt intrinsic resistors and intrinsic capacitors. When the behavior between junction and i-layer is different, the accuracy of the traditional model is limited. It is necessary to model each part of the diode separately to enhance model accuracy. Physical models, on the other hand, are based on describing and solving numerically basic diffusion-drift semiconductor equations, using the finite element method, for example [4]. In this way, device behavior is modeled very precisely in two or even three dimensions. Unfortunately, a precise physical model with high numerical complexity involves very long computational time, making this approach suited to individual device design and optimization, but prohibitive for circuit level modeling.

A novel equivalent circuit model of GaAs PIN diodes is reported in this paper. Based on physical mechanisms, GaAs PIN diodes are divided into three parts, the p<sup>+</sup> n<sup>-</sup> junction, i-layer, and n<sup>-</sup> n<sup>+</sup> junction. Each part is modeled separately, and the entire PIN diode model is then formed by combining the three sub-models. Since characteristics of the junction and i-layer are described, the model accuracy is improved. Meanwhile, compared to physical models, the parameters of this model are fewer, and the parameter extraction method is simpler, which lead to its feasibility in circuit design.

# 2 GaAs PIN diode model and parameter extraction

#### 2.1 Equivalent circuit model of GaAs PIN diodes

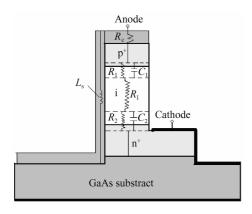

A commonly used device structure, proposed by Takasu<sup>[5]</sup>, is shown in Fig. 1. When the diode is forward biased, the diode impedance is small because the i-layer is filled with carriers and the junction capacitance is very large. When reversely biased, the i-layer is depleted of carriers and the impedance is very high. The junction capacitance becomes smaller as depletion width increases.

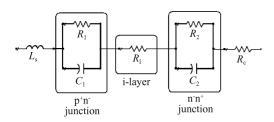

The novel equivalent circuit model of GaAs PIN diodes is shown in Fig. 2. The GaAs PIN diodes are divided into three parts according to their respective

<sup>\*</sup> Project supposed by the National Natural Science Foundation of China (No. 10002909) and the State Key Development Program for Basic Research of China (No. G2002CB311901)

<sup>†</sup> Corresponding author. Email: rfwu04@ mails. gucas. ac. cn

Fig. 1 Cross-sectional view

characteristics, namely the p<sup>+</sup> n<sup>-</sup> junction, i-layer, and n n i junction. Thus, the equivalent circuit model of GaAs PIN diodes is composed of three sub-models. The characterization of p<sup>+</sup> n<sup>-</sup> junction and n<sup>-</sup> n<sup>+</sup> junction can be implemented using the conventional theory of pn junction modeling[6]. The junction resistor  $R_1$  and junction capacitor  $C_1$  model the characteristics of the p<sup>+</sup> n<sup>-</sup> junction. Similarly, junction resistor  $R_2$  and junction capacitor  $C_2$  model the characteristics of the n<sup>-</sup> n<sup>+</sup> junction. The i-layer is modeled by a variable resistor  $R_{\rm I}$ , which is dominated by the bias condition of the diode. These three sub-models are connected in a series configuration to ensure the same DC current flow.  $L_s$  is a parasitic inductor and  $R_c$  is a contact resistor.  $L_s$  and  $R_c$  both exist in the anode and cathode, while Figure 1 is simplified so that  $L_s$  and  $R_s$ are only in the anode. Each sub-model will be analyzed in detail.

### 2. 2 $p^+ n^-$ junction

The p<sup>+</sup> n<sup>-</sup> junction can be represented by the conventional model of a pn junction. The sub-model comprises junction resistor  $R_1$  and junction capacitor  $C_1$ . When the diode is forward biased,  $R_1$  is small and can be calculated using Eq. (1).  $C_1$  is composed of the space-charge region capacitance  $C_{T1}$  and the diffusion capacitance  $C_{\rm D1}$ , as shown in Eq. (2). J is the current density and A is the area of the  $p^+ n^-$  junction. When the diode is reversely biased, the junction resistance  $R_1$  is large and junction capacitance  $C_1$  comprises only the space-charge region capacitance  $C_{\rm T1}$ .  $C_{\rm T1}$  can be

Fig. 2 Novel equivalent circuit model

reduced by increasing the i-layer thickness. However, unintentional doping of the i-layer limits the maximum depletion width to about  $1\mu$ m and prevents further reduction of the junction capacitance. The calculation of  $C_{\rm T1}$  and  $C_{\rm D1}$  is given in Eqs. (3) and (4).  $V_{\rm BJ1}$ is the built-in voltage of the  $p^+ n^-$  junction and  $V_{A1}$  is the voltage drop across the p<sup>+</sup> n<sup>-</sup> junction, which are expressed in Eqs. (5) and (6), respectively. In Eq. (6),  $J_{01}$  is the saturation current density, which is given in Eq. (7).

$$R_1 = \frac{kT}{aAJ} \tag{1}$$

$$C_{\text{total1}} = C_{\text{T1}} + C_{\text{D1}} \tag{2}$$

$$R_{1} = \frac{kT}{qAJ}$$

(1)

$$C_{\text{totall}} = C_{\text{T1}} + C_{\text{D1}}$$

(2)

$$C_{\text{T1}} = A\sqrt{\frac{\epsilon q N_{\text{B}}}{2(V_{\text{BJI}} - V_{\text{A1}})}}$$

(3)

$$C_{\rm Dl} = qA \frac{q}{kT} L_{\rm P} p_{\rm n0} \exp\left(\frac{qV_{\rm Al}}{kT}\right) \tag{4}$$

$$V_{\rm BJI} = \frac{kT}{a} \ln\left(\frac{N_{\rm A} N_{\rm D}}{n_{\rm i}^2}\right) \tag{5}$$

$$V_{\rm Al} = \frac{kT}{q} \ln \left( \frac{J}{J_{\rm 0l}} \right) \tag{6}$$

$$J_{01} = \frac{qD_{\rm n} n_{\rm op}}{L_{\rm cr}} + \frac{qD_{\rm p} p_{\rm on}}{L_{\rm cr}} \tag{7}$$

#### 2.3 $n^-n^+$ junction

The sub-model of the n<sup>-</sup> n<sup>+</sup> junction comprises the junction resistor  $R_2$  and the junction capacitor  $C_2$ . The calculation of sub-model parameters is similar to the p<sup>+</sup> n<sup>-</sup> junction, except for the built-in voltage and saturation current density. The built-in voltage of the  $n^- n^+$  junction is given in Eq. (8). The saturation current density is expressed by Eq. (9).

$$V_{\rm BJ2} = \frac{kT}{q} \ln\left(\frac{n_{\rm onl}}{n_{\rm on2}}\right) \tag{8}$$

$$J_{02} = \frac{qD_{\rm n} n_{\rm op}}{L_{\rm n}} \tag{9}$$

#### 2.4 i-layer

The i-layer is modeled by a variable resistor  $R_1$ , which depends on the bias condition of the diode. When the diode is in the on-state,  $R_{\perp}$  is small due to the conductivity modulation effect<sup>[7]</sup>; in the off-state,  $R_1$  is large since the i-layer is depleted of carriers.

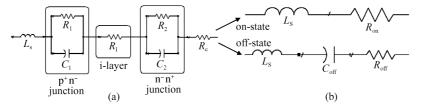

The extraction of  $R_1$  is implemented through the measurement of the ABCD-parameter of the diode. When the diode is forward biased, the entire equivalent circuit model of the diode can be simplified to parasitic inductor  $L_s$  and small signal on-state resistor  $R_{\rm on}$  in series configuration.  $R_{\rm on}$  is composed of the resistor of i-layer  $R_1$ , the resistor of the  $p^+ n^-$  and  $n^- n^+$ junction  $R_1$  and  $R_2$ , and parasitic contact resistor  $R_c$ . When the diode is reversely biased, the entire model can be simplified to the series of off-state capacitor

Fig.3 Equivalent circuit model of GaAs PIN diodes (a) Entire equivalent circuit model; (b) Simplified model of on-state and off-state diode

$C_{\rm off}$ , parasitic inductor  $L_{\rm s}$ , and off-state resistor  $R_{\rm off}$ .  $R_{\rm off}$  is composed of the resistor of i-layer  $R_{\rm I}$  and parasitic contact resistor  $R_{\rm c}$ . This simplification is shown in Fig. 3. The value of  $R_{\rm on}$  and  $R_{\rm off}$  can be extracted through the measurement of the real part of the AB-CD-parameter of the diode. The resistance of the i-layer  $R_{\rm I}$  can be calculated by Eq. (10).

$$R_{1}(\text{on-state}) = R_{\text{on}} - R_{c} - R_{1} - R_{2} \approx \text{Re}(ABCD(1,2))_{\text{on}} - R_{c} - R_{1} - R_{2}$$

$$R_{1}(\text{off-state}) = R_{\text{off}} - R_{c} \approx \text{Re}(ABCD(1,2))_{\text{off}} - R_{c}$$

(10)

#### 2.5 Parasitic parameters

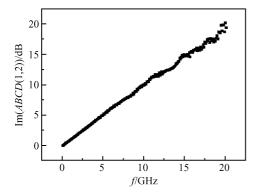

Parasitic resistor  $R_c$  comes from the contact resistor of the anode and cathode, and the measurement of  $R_c$  is represented in Ref. [8]. Parasitic inductance is caused by electrode down-lead inside the diode. When the diode is forward biased, the capacitance is very large and the impact of the capacitor and the diode impedance is negligible compared to the inductor, especially under high frequency. Thus, the parasitic inductance can be approximated by Eq. (11). The relationship between the imaginary part of the ABCD-parameter and the frequency is shown in Fig. 4.  $R_c$  and  $L_s$  are independent of the bias condition of the diode.

$$L_{s} = \frac{\operatorname{Im}(ABCD(1,2))}{2\pi f} \tag{11}$$

Fig. 4 Im  $(ABCD\ (1,2))$  versus frequency under forward biased condition

## 3 Experimental results

The diodes were manufactured on a molecular beam epitaxy (MBE) grown material. The p<sup>+</sup> - and n<sup>+</sup>-layer were highly doped with a concentration of  $1\times10^{18}\sim5\times10^{19}\,\mathrm{cm}^{-3}$  (gradually increasing) and  $3\times$ 1018 cm<sup>-3</sup> to minimize the on-state resistance. The diodes were fabricated on circular mesas using wet etching with  $H_3 PO_4 : H_2 O_2 : HO_2 = 2 : 3 : 30$  solution. Ptype metal contacts made of Pt/Ti/Au were deposited on the p<sup>+</sup>-layer. Ni/Ge/Au/Ge/Ni/Au contacts were then deposited on the n<sup>+</sup>-layer. Both contacts were annealed at 375°C for 1min. Diodes were passivated with 0.5 µm Si<sub>3</sub>N<sub>4</sub>. Electroplating was used to implement the electrode down-leads instead of evaporation since the evaporation is anisotropic and cannot cover the p<sup>+</sup> - and i-layer step tightly, whereas the electroplating is isotropic.

Three types of diodes with different sizes were designed: ① radius of p<sup>+</sup>-layer =  $40\mu$ m, radius of n<sup>+</sup>-layer =  $60\mu$ m; ② radius of p<sup>+</sup>-layer =  $30\mu$ m, radius of n<sup>+</sup>-layer =  $50\mu$ m; ③ radius of p<sup>+</sup>-layer =  $25\mu$ m, radius of the n<sup>+</sup>-layer =  $45\mu$ m. For each type, five groups of diodes were implemented to validate the model . The

Table 1 The value of model parameters

| Table 1 The value of model parameters |                                                        |      |                                     |      |      |                                      |      |      |

|---------------------------------------|--------------------------------------------------------|------|-------------------------------------|------|------|--------------------------------------|------|------|

|                                       | Description                                            | Unit | Value                               |      |      |                                      |      |      |

| Name                                  |                                                        |      | $I_{\text{forward}} = 10 \text{mA}$ |      |      | $V_{\text{reverse}} = -10 \text{ V}$ |      |      |

|                                       |                                                        |      | 1                                   | 2    | 3    | 1                                    | 2    | 3    |

| $C_1$                                 | p <sup>+</sup> n <sup>-</sup><br>junction<br>capacitor | pF   | 360                                 | 201  | 141  | 0.42                                 | 0.23 | 0.17 |

| $R_1$                                 | p + n - junction<br>intrinsic<br>resistor              | Ω    | 0.38                                | 0.38 | 0.38 | _                                    | _    |      |

| $R_{\rm I}$                           | Base region resistor                                   | Ω    | 0.26                                | 1.29 | 1.67 | 10                                   | 16   | 28   |

| $C_2$                                 | n n + junction<br>capacitor                            | pF   | 457                                 | 256  | 179  | 0.45                                 | 0.24 | 0.17 |

| $R_2$                                 | n - n + junction<br>intrinsic<br>resistor              | Ω    | 0.38                                | 0.38 | 0.38 | _                                    | _    |      |

| $L_{\rm s}$                           | Parasitic inductor                                     | nН   | 0.12                                | 0.12 | 0.12 | 0.12                                 | 0.12 | 0.12 |

| $R_{\rm c}$                           | Parasitic resistor                                     | Ω    | 1.28                                | 1.28 | 1.28 | 1.28                                 | 1.28 | 1.28 |

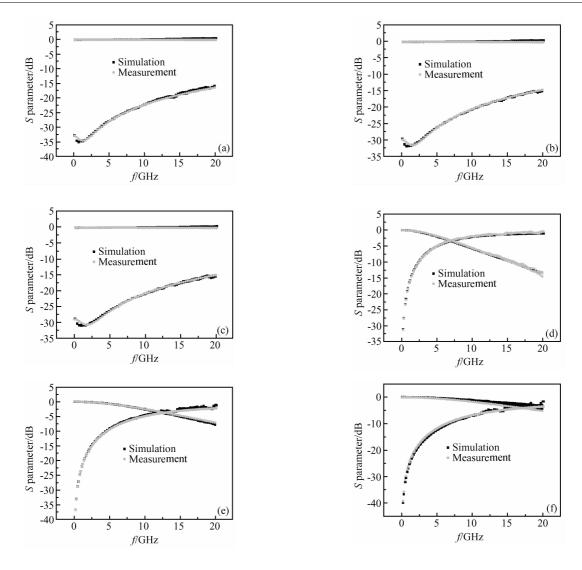

Fig. 5 Comparison between simulation and measurement (a)  $I_{on} = 10 \text{mA}$ , size ①; (b)  $I_{on} = 10 \text{mA}$ , size ②; (c)  $I_{on} = 10 \text{mA}$ , size ③; (d)  $V_{off} = -10 \text{V}$ , size ①; (e)  $V_{off} = -10 \text{V}$ , size ②; (f)  $V_{off} = -10 \text{V}$ , size ③

forward biased current is 10mA and the reversely biased voltage is -10V. Using Eqs. (1) to (9), the values of  $R_1$ ,  $R_2$ ,  $C_1$ , and  $C_2$  were obtained.  $R_c$  was measured with the conventional method. The S-parameter of the diode was measured and transformed into the real part and imaginary part of the ABCD-parameter.  $R_1$  and  $L_s$  can be calculated with Eqs. (10) and (11). All of the model parameters are shown in Table 1.

With the extracted model parameters, the equivalent circuit model was simulated as a linear network in the Advanced Design Simulator (ADS) from Agilent Technologies, which is suitable for high frequency simulation. In ADS, the S-parameter of the model is swept form 0.1 to 20.1 GHz to compare with measurement. Fifteen groups belonging to the three types of diodes were measured under both forward and reversely biased conditions with the network analyzer HP 8510C, which can sweep S-parameters from 100

MHz to 20.1GHz. Comparison between simulation and measurement revealed that the developed model excellently agrees with experimental measurement over a wide range of frequency for every type of diode, as shown in Fig. 5.

#### 4 Conclusion

A new equivalent circuit model of a GaAs PIN diode and the corresponding parameter extraction method are presented. The GaAs PIN diodes are divided into three parts to be modeled separately, greatly improving the model's accuracy. The procedure of parameter extraction is convenient to manipulate. Only two parameters of the model are determined by measurement while the others can be obtained by straightforward calculation. Excellent agreement is found between experiment measurement and model simulation.

676 半 导 体 学 报 第 29 卷

#### References

- [1] Lee J L, Zych D, Reese E, et al. Monolithic 2-18GHz low loss, onchip biased PIN diode switches. IEEE Trans Microw Theory Tech, 1995, 43(2):250

- [2] Asu H,Sasaki F,Kawasaki H,et al. W-band SPST transistor switches. IEEE Microw Guided Wave Lett. 1996.6(9):315

- [3] Mizutani H, Funabashi M, Kuzuhara M, et al. Compact DC-60 GHz HJFET MMIC switches using ohmic electrode sharing technology. IEEE Trans Microw Theory Tech, 1998, 46(11):1597

- [4] Igic P M, Mewhy P A, Towers M S, et al. New physically-based

- PIN diode compact model for circuit modeling applications. IEE Proc Circuits Devices Syst,2002,8,(149);257

- [5] Takasu H. Estimation of equivalent circuit parameters for a millimeter-wave GaAs PIN diode switch. IEEE Proc Circuits Devices Syst,2003,150(2):92

- [6] Gao Wenhuan, Liu Rensheng. Electronic network basis. Beijing: Higher Education Press, 1996; 41

- [7] Baliga B J. Tower semiconductor devices. PWS Publishing Company, 1996:155

- [8] Wu Dingfen, Yan Benda. Theory, measurement and technology of ohmic contact of the interface of metal and semiconductor. Press of Shanghai Jiao Tong University, 1989;24

## GaAs PIN 二极管的新等效电路模型\*

吴茹菲1, 张海英1 尹军舰1 李 潇2 刘会东1 刘训春1

(1 中国科学院微电子研究所,北京 100029) (2 四川大学,成都 610064)

摘要:基于物理原理的分析,提出了 GaAs PIN 二极管的一种新等效电路模型. GaAs PIN 二极管被分成 p<sup>+</sup> n<sup>-</sup> 结、基区和 n<sup>-</sup> n<sup>+</sup> 结三部分分别建模,总的模型由三个子模型组成,从而极大地提高了模型的准确性. 相应的模型参数提取过程不要求苛刻的实验或测试条件,简便易操作. 研制了 15 组 GaAs PIN 二极管来验证模型,测试结果表明模型准确地反映了 GaAs PIN 二极管的正向和反向特性.

关键词: GaAs PIN 二极管;模型;参数提取

**PACC:** 7340L **EEACC:** 2560B

中图分类号: TN31 文献标识码: A 文章编号: 0253-4177(2008)04-0672-05

<sup>\*</sup>国家自然科学基金(批准号:10002909)和国家重点基础研究发展规划(批准号:G2002CB311901)资助项目

<sup>†</sup>通信作者.Email:rfwu04@mails.gucas.ac.cn