# Degradation of nMOS and pMOSFETs with Ultrathin Gate Oxide Under DT Stress\*

Hu Shigang<sup>†</sup>, Hao Yue, Ma Xiaohua, Cao Yanrong, Chen Chi, and Wu Xiaofeng

(Key Laboratory of Wide Band-Gap Semiconductor Materials and Devices, School of Microelectronics, Xidian University, Xi'an 710071, China)

**Abstract:** The degradation of device parameters and the degradation of the stress induced leakage current (SILC) of thin tunnel gate oxide under constant direct-tunneling voltage stress are studied using nMOS and pMOSFETs with 1.4nm gate oxides. Experimental results show that there is a linear correlation between the degradation of the SILC and the degradation of  $V_{th}$  in MOSFETs during different direct-tunneling (DT) stresses. A model of tunneling assisted by interface traps and oxide trapped positive charges is developed to explain the origin of SILC during DT stress.

Key words: threshold voltage; interface traps; direct tunneling; SILC

PACC: 7340G; 7320; 7340Q

#### 1 Introduction

Aggressive shrinking of MOSFETs causes direct-tunneling (DT) gate leakage to become significant in transistor operation, and thus spurs investigation into DT phenomena through gate insulators. In the thin gate oxide regime, direct tunneling current increases exponentially as oxide thickness decreases, which is of primary concern for CMOS scaling<sup>[1~5]</sup>. Some models have been presented to investigate the theory of direct tunneling. However, few studies have concentrated on the degradation of devices under DT stress.

The stress induced leakage current (SILC), namely the excess low field current across a thin gate oxide after a high electric field stress, is a major concern for long-term reliability and the scaling of the tunnel oxide in nonvolatile memories [6~11]. SILC plays an important role in the reliability of devices. The SILC has been also indicated as a precursor of catastrophic breakdown<sup>[12~15]</sup>. For these reasons, the investigation of SILC is of primary importance for oxide degradation. Although a consensus has been reached in understanding the conduction mechanism of SILC in relatively thick samples (>4nm), the low voltage SILC generation mechanism in ultrathin (<3nm) oxide films is still not clearly under $stood^{\lceil 16 \sim 18 \rceil}.$  Therefore, further study is necessary to investigate the origin of SILC during DT stress.

In this work, we present experimental results of MOSFETs reliability with ultrathin oxide (1.4nm).

The current through the oxide under direct tunneling stress degrades the quality of the oxide, causing drift in the threshold voltage ( $V_{\rm th}$ ), a reduction of saturation drain current ( $I_{\rm dsat}$ ), and an increase of stress-induced oxide leakage current. It is found experimentally that there is a linear correlation between the degradation of the stress induced leakage current and the degradation of  $V_{\rm th}$  in MOSFETs during different DT stresses. We develop a model of tunneling assisted by interface traps and oxide trapped positive charges to explain the origin of SILC during DT stress.

## 2 Devices and experiments

The MOSFETs used here were fabricated using 90nm process technology with a lightly doped drain (LDD) structure and a shallow trench isolation (STI) scheme. The MOSFETs have a channel length of  $40\mu m$ , a width of  $10\mu m$ , and a gate oxide thickness of 1.4nm. The gate oxides of all devices were annealed in  $N_2O$  gas ambient after thermal growth. The operation voltage is 1.0V for the MOSFETs. An Agilent B1500A high-precision semiconductor parameter analyzer was used to conduct the tests.

Constant voltage stress and *I-V* measurements were performed with an Agilent B1500A semiconductor parameter analyzer. Both positive gate bias DT (+ DT) stress and negative gate bias DT (- DT) stress were performed on MOSFETs. For both the nMOSFET and pMOSFET, the + DT stress was per-

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Nos. 60736033, 60506020)

<sup>†</sup> Corresponding author. Email: hsg99528@126.com

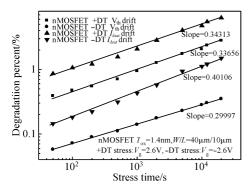

$\label{eq:fig.1} \begin{tabular}{ll} Fig. 1 & Time dependence of degradation of device parameters in nMOSFET under positive and negative gate bias DT stress \end{tabular}$

formed at  $V_{\rm gs}=+2.6{\rm V}$  and the  $-{\rm DT}$  stress was performed at  $V_{\rm gs}=-2.6{\rm V}$ . Stress was interrupted at regular intervals and device parameters were measured. The SILCs were characterized by measuring the *I-t* (gate current-stress time) characteristics at constant, low, pre-tunneling voltages at regular intervals. The SILC was measured at  $V_{\rm g}=0.8{\rm V}$  during DT stress for the nMOSFET and measured at  $V_{\rm g}=-0.8{\rm V}$  during DT stress for the pMOSFET. All experiments were performed at room temperature.

### 3 Results and discussion

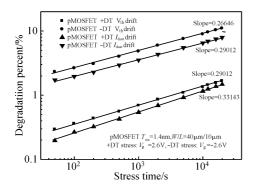

First, we study the degradation of device parameters including  $V_{\rm th}$  and  $I_{\rm dsat}$  under constant direct-tunneling voltage stress in MOSFETs. Figures 1 and 2 show the time dependence of the degradation of device parameters in nMOSFETs and pMOSFETs, respectively.  $V_{\rm th}$  in the nMOSFET increases towards the positive direction and  $I_{\rm dsat}$  in the nMOSFET decreases.  $V_{\rm th}$  in the pMOSFET increases towards the negative direction and the absolute value of  $I_{\rm dsat}$  in the pMOSFET decreases. The degradation of device parameters during + DT stress is more serious than that of during - DT stress for the nMOSFET, and the degradation of device parameters during + DT stress is more serious than that of during + DT stress for the

Fig. 2 Time dependence of degradation of device parameters in pMOSFET under positive and negative gate bias DT stress

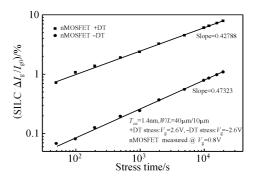

$\label{eq:Fig.3} \ \ \, \text{Time evolution of SILC under direct tunneling stress on the nMOSFET}$

pMOSFET. It is also evident that the degradation of  $I_{\rm dsat}$  is more serious than that of  $V_{\rm th}$  during both DT stresses for the nMOSFET, but the degradation of  $V_{\rm th}$  is more serious than that of  $I_{\rm dsat}$  during both DT stresses for the pMOSFET.

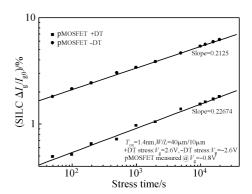

Second, the SILC of ultrathin gate oxide is also investigated. Figures 3 and 4 show the time evolution of SILC under direct tunneling stresses on the nMOS-FET and pMOSFET, respectively. SILC in the nMOS-FET increases towards the positive direction and SILC in the pMOSFET increases towards the negative direction. The relationship between SILC and stress time under different stresses shows perfect linearity in the log-log scale, as shown in Figs. 3 and 4. The SILC increases with the stress time under four different tunneling stresses. The degradation of SILC measured at  $V_g = 0.8V$  during + DT stress is more serious than that of during - DT stress for the nMOSFET, and the degradation of SILC measured at  $V_g = -0.8V$  during - DT stress is more serious than that of during + DT stress for the pMOSFET. The SILC result is consistent with the result of the degradation of device parame-

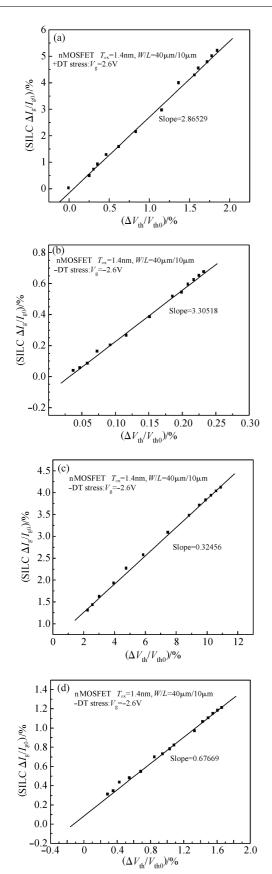

In our experiments, there is a good linear correlation between the degradation of SILC and the degradation of  $V_{\rm th}$  in MOSFETs during different DT stresses, as shown in Fig. 5. This result is deserved to be paid

Fig. 4 Time evolution of SILC under direct tunneling stress on the pMOSFET

Fig. 5 SILC (measured at  $V_{\rm g}$  = 0.8V for the nMOSFET and measured at  $V_{\rm g}$  = -0.8V for the pMOSFET) variations versus  $V_{\rm th}$  variations under different DT stresses for MOSFETs

attention to. Through a good analysis of the result, we can investigate the origin of SILC in MOSFETs

during DT stress.

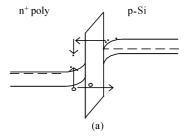

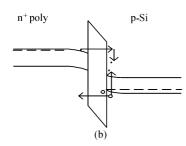

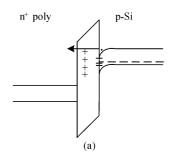

For a good understanding of the experimental results, it is necessary to clearify the process of the motion of carriers under various constant direct-tunneling voltage stresses in the MOSFETs. Figure 6 shows the energy band diagrams of the MOS structure under the four stress conditions. The energy band diagram for the nMOSFET under + DT stress is presented in Fig. 6 (a). Electrons directly tunneling from the inverted channel are dominant during + DT stress in the nMOSFET. A fraction of the injected electrons arriving at the anode (the polysilicon gate) lose their energy by creating electron-hole pairs in the valence band of the polysilicon gate via impact ionization. These holes tunnel back into the oxide layer and are transported towards the cathode. Some of the injected holes get trapped near the gate/oxide interface and become a part of the oxide trapped charges.

The energy band diagram for the nMOSFET under - DT stress is shown in Fig. 6 (b). Electrons are first injected from the gate into the conduction band of SiO<sub>2</sub> due to direct tunneling. Since the electric field is very high, the injected electrons will gain kinetic energy from the oxide field and will lose energy by phonon scattering. The energetic electrons will arrive at the silicon substrate and will produce electron-hole pairs via the interband impact mechanism. The holes generated with enough energy will tunnel back into the oxide layer. A small fraction of these holes are trapped near the Si-SiO<sub>2</sub> interface and become a part of the oxide trapped charges. When stress was interrupted at regular intervals, device parameters were measured. The measurement setup is the same.  $V_{\rm th}$  is one of the most important parameters, and here we mainly focus on the degradation of  $V_{\rm th}$ .  $V_{\rm th}$  in an nMOSFET can be expressed as

$$V_{\text{th}} = 2\phi_{\text{F}} + \frac{\sqrt{2qK_{\text{s}}\varepsilon_{\text{o}}N_{\text{A}}(2\phi_{\text{F}})}}{C_{\text{ox}}} + \phi_{\text{MS}} - \frac{\lambda Q_{\text{ox}}}{C_{\text{ox}}} - \frac{Q_{\text{it}}(\phi_{\text{s}} = 2\phi_{\text{F}})}{C_{\text{ox}}}$$

(1)

where  $\phi_{\rm F}$  is the Fermi potential, q the electron charge,  $K_{\rm s}$  the silicon dielectric constant,  $\varepsilon_{\rm 0}$  the permittivity of free space,  $N_{\rm A}$  the acceptor doping concentration,  $C_{\rm ox}$  the oxide capacitance,  $\phi_{\rm MS}$  the metalsemiconductor work function difference, and  $\lambda$  the charge distribution factor<sup>[19]</sup>. Here,  $Q_{\rm ox}$  is defined as the trapped-oxide sheet charge density, which includes all charge components that are not sensitive to the silicon surface potential such as the trapped-oxide charge and the fixed oxide charge,  $\lambda$  is the charge distribution factor and  $Q_{\rm it}$  is the interface trapped charge density at the Si/SiO<sub>2</sub> interface, which depends on the surface potential  $\phi_{\rm s}$ . The shift of  $V_{\rm th}$  can be

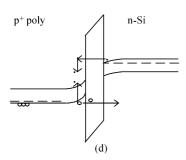

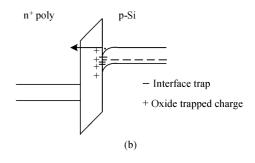

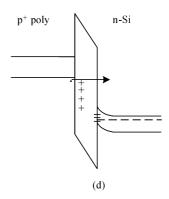

Fig. 6 Energy band diagrams of the MOS structure under different stress conditions (a) + DT stress for the nMOSFET; (b) - DT stress for the nMOSFET; (c) - DT stress for the pMOSFET; (d) + DT stress for the pMOSFET

caused by the increase of the trapped-oxide charges and interface traps. For the nMOSFET under DT, interface traps are charged negatively during the measurement, and the trapped-oxide charges are positive. Interface traps make  $V_{\rm th}$  drift positively, but the trapped-oxide charge makes  $V_{\rm th}$  drift negatively. The trapped-oxide charges and interface traps in the nMOSFET during DT stress play different roles in the degradation of  $V_{\rm th}$ . When the injected holes get trapped near the gate/oxide interface,  $\lambda$  is very small and is almost 0. When the injected holes get trapped

near the  $Si/SiO_2$  interface,  $\lambda$  is large and is almost 1. So the holes trapped near the Si/SiO<sub>2</sub> interface are more effective than the holes trapped near the gate/ oxide interface. In addition, the difference between - DT and + DT stresses is that the impact-ionization generated electron-hole pairs will occur at the Si/SiO<sub>2</sub> interface in the case of - DT stress and will play an important role in the generation of interface traps, whereas the electron-hole pairs generated in the +DT stress will be generated in the heavily-doped polysilicon and quickly recombine. Figure 1 shows that the degradation of  $V_{th}$  during + DT stress is more serious than that of during - DT stress for the nMOSFET. Thus, the increase of holes trapped near the Si/SiO<sub>2</sub> interface can shield a part of the increase of interface traps at the Si/SiO<sub>2</sub> interface during - DT stress for the nMOSFET.

The energy band diagram for the pMOSFET under – DT stress is presented in Fig. 6(c). The valence electrons tunnel from the  $p^+$  polysilicon gate into the inverted p type channel of the substrate. A fraction of the injected electrons will lose their energy when arriving at the anode by creating electron-hole pairs via impact ionization. These holes tunnel back into the oxide layer and are transported towards the cathode. Some of the injected holes get trapped near the Si/SiO<sub>2</sub> interface and become a part of oxide trapped charges.

The energy band diagram for the pMOSFET under + DT stress is shown in Fig. 6 (d). The electrons tunnel from the accumulated substrate Si layer into the p<sup>+</sup> polysilicon gate. A fraction of the injected electrons will lose their energy when arriving at the anode by creating electron-hole pairs via impact ionization. These holes tunnel back into the oxide layer and are transported towards the cathode. Some of the injected holes get trapped near the gate/oxide interface and become a part of the oxide trapped charges. The shift of  $V_{\rm th}$  is caused by the increase of trappedoxide charges and interface traps in the pMOSFET. For the pMOSFET, interface traps are charged positively during the measurement, and the trapped-oxide charges are positive. Interface traps make  $V_{\rm th}$  drift negatively and the trapped-oxide charges also make  $V_{\rm th}$  drift negatively. The holes trapped near the Si/ SiO<sub>2</sub> interface play a more important role than the holes trapped near the gate/oxide interface. The impact-ionization generated electron-hole pairs will occur at the Si/SiO<sub>2</sub> interface in the case of -DT stress and play an important role in the generation of interface traps. This experimental result shows that the degradation of device parameters during - DT stress is more serious than that of during + DT stress for the pMOSFET, as shown in Fig. 2.

The origin of SILC has been examined many  $\mathsf{times}^{[20\sim 26]}$  . Some models have been presented to investigate the SILC, among which the trap assisted tunneling model, the thermal assisted tunneling model, and the resonant tunneling model are the most popular. However, no complete agreement has been reached and it is not easy to analyze the SILC in ultrathin 1. 4nm thick oxide using these models. SILC is measured by interrupting stress at regular intervals. There is a good linear correlation between the degradation of SILC and the degradation of  $V_{\rm th}$  in MOS-FETs during different DT stresses, as shown in Fig. 5. Because the shift of threshold voltage results from the generation of interface traps and oxide trapped positive charges, there should be some connection between the degradation of gate leakage current and their generation. We develop a model with interface traps and oxide trapped positive charges to explain the SILC here.

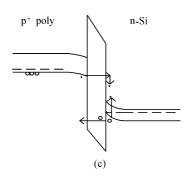

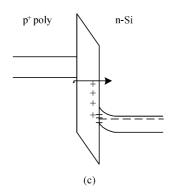

The model with interface traps and oxide trapped positive charges assisting tunneling are schematically shown in Fig. 7. For nMOSFETs, the SILC is measured at  $V_g = 0.8V$  after DT stress. When the measurement voltage is applied, there are interface traps and oxide trapped positive charges generated. Because the gate voltage is much larger than 0V, as shown in Figs. 7 (a) and 7(b), the p-Si conduction band is higher than the n<sup>+</sup>-polysilicon valence band. Electrons can emit from the inverted channel. The energy band diagram for the measurement of SILC in the nMOSFET under + DT stress is drawn in Fig. 7 (a). Interface traps at the Si/SiO<sub>2</sub> interface can serve as a stepping stone because they effectively capture the electrons from the inverted channel and then immediately emit them. Meanwhile, the oxide trapped positive charges near the gate/oxide interface help electrons to tunnel through the oxide by causing a barrier height lowering and enhancing the electric field in the oxide. The energy band diagram for the measurement of SILC in the nMOSFET under - DT stress is presented in Fig. 7 (b). The oxide trapped positive charges are near the Si/SiO<sub>2</sub> interface. Interface traps and oxide trapped positive charges play the same role in Figs. 7 (a) and 7(b).

For pMOSFETs, the SILC is measured at  $V_{\rm g} = -0.8 \, \rm V$  after DT stress. When the measurement voltage is applied, there are also interface traps and oxide trapped positive charges that have been generated. Because the gate voltage is much smaller than 0V, as shown in Figs. 7(c) and 7(d), the p<sup>+</sup>-polysilicon valence band is higher than the n-Si conduction band. Electrons can emit from the p<sup>+</sup>-polysilicon valence

Fig. 7 Schematics of the model with interface traps and oxide trapped charges assisting tunneling during the measurement of SILC (a) Under +DT stress for the nMOSFET; (b) Under -DT stress for the nMOSFET; (c) Under -DT stress for the pMOSFET; (d) Under +DT stress for the pMOSFET

band. The energy band diagram for the measurement of SILC in the pMOSFET under – DT stress is drawn in Fig. 7(c). The oxide trapped positive charges near the Si/SiO<sub>2</sub> interface help electrons to tunnel through the oxide by causing a barrier height lowering and en-

hancing the electric field in the oxide. Interface traps at  $\mathrm{Si/SiO_2}$  interface can serve as a stepping stone. They can effectively capture the electrons from the  $\mathrm{p^+}$ -polysilicon valence band and then immediately emit them toward the substrate. The energy band diagram for the measurement of SILC in pMOSFET under +DT stress is shown in Fig. 7 (d). The oxide trapped positive charges are near the gate/oxide interface. Interface traps and oxide trapped positive charges play the same role in Figs. 7(c) and 7(d). In this model, the interface traps and oxide trapped positive charges during DT stress play an important role in the degradation of the SILC.

#### 4 Conclusion

In this paper, the degradation of devices has been investigated in detail under a variety of DT stress conditions. First, the degradation of device parameters, including  $V_{\rm th}$  and  $I_{\rm dsat}$ , under constant direct-tunneling voltage stress in MOSFETs was presented. Second, the SILC of ultrathin gate oxide was also investigated and it was found that there is a linear correlation between the degradation of SILC and the degradation of  $V_{\rm th}$  in MOSFETs during different DT stresses. By analyzing the process of motion of carriers under various constant direct-tunneling voltage stresses in the MOS-FETs, it is confirmed that the degradation of  $V_{\rm th}$  and the degradation of SILC are interrelated due to the generation of interface traps and trapped holes during DT stresses. We developed a model of tunneling assisted by interface traps and oxide trapped positive charges to explain the origin of SILC during DT stresses.

#### References

- [1] Momose H S, Nakamura S, Ohguro T, et al. Study of the manufacturing feasibility of 1.5-nm direct-tunneling gate oxide MOS-FETs: uniformity, reliability, and dopant penetration of the gate oxide. IEEE Trans Electron Devices, 1998, 45(3):691

- [2] Yang N, Henson W K, Hauser J R, et al. Modeling study of ultrathin gate oxides using direct tunneling current and capacitance-voltage measurements in MOS devices. IEEE Trans Electron Devices, 1999, 46(7):1464

- [3] Samanta P.Tsz Y, Alain C K, et al. Direct tunneling stress-induced leakage current in nMOS devices with ultrathin gate oxides. IEEE 43rd Annual International Reliability Physics Symposium, 2005; 594

- [4] Liu P T, Huang C S, Lee D Y, et al. Modeling of nitrogen profile effects on direct tunneling probability in ultrathin nitrided oxides. Appl Phys Lett, 2008:022112-1

- [5] Yeo Y C, King T J, Hu C. Direct tunneling leakage current and scalability of alternative gate dielectrics. Appl Phys Lett, 2002, 81 (11), 2091

- [6] Blauwe J D, Houdt J V, Wellekens D, et al. SILC-related effects in flash E<sup>2</sup>PROM's-Part I: a quantitative model for steady-state SILC. IEEE Trans Electron Devices, 1998, 45(8):1745

- [7] Blauwe J D, Houdt J V, Wellekens D, et al. SILC-related effects in flash E<sup>2</sup>PROM's-Part II: prediction of steady-state SILC-related disturb characteristics. IEEE Trans Electron Devices, 1998, 45 (8):1751

- [8] Ielmini D, Spinelli A S, Lacaita A L, et al. Statistical profiling of SILC spot in flash memories. IEEE Trans Electron Devices, 2002, 49(10), 1723

- [9] Ielmini D, Spinelli A S, Visconti A, et al. Characterization of oxide trap energy by analysis of the SILC roll-off regime in flash memories. IEEE Trans Electron Devices, 2006, 53(1):126

- [10] Vianello E. Driussi F. Esseni D. et al. Explanation of SILC probability density distributions with nonuniform generation of traps in the tunnel oxide of flash memory arrays. IEEE Trans Electron Devices, 2007, 54(8):1953

- [11] Driussi F, Widdershoven F, Esseni D, et al. Experimental characterization of statistically independent defects in gate dielectrics-part II: experimental results on flash memory arrays. IEEE Trans Electron Devices, 2005, 52(5):949

- [12] Rodriguez R, Miranda E, Pau R, et al. Monitoring the degradation that causes the breakdown of ultrathin (<5nm) SiO<sub>2</sub> gate oxides. IEEE Electron Device Lett, 2000, 21(5):251

- [13] Pantisano L. Cheung K P. Stress-induced leakage current (SILC) and oxide breakdown; are they from the same oxide traps. IEEE Trans Devices and Materials Reliability, 2001, 1(2):109

- [14] Ielmini D, Spinelli A S, Lacaita A, et al. Defect generation statistics in thin gate oxides. IEEE Trans Electron Devices, 2004, 51 (8):1288

- [15] Ielmini D, Spinelli A S, Lacaita A, et al. Impact of correlated generation of oxide defects on SILC and breakdown distributions.

IEEE Trans Electron Devices, 2004, 51(8), 1281

- [16] DiMaria D J, Cartier E. Mechanism for stress-induced leakage currents in thin silicon dioxide films. J Appl Phys, 1995, 78(6): 3883

- [17] Kimura M. Ohmi T. Conduction mechanism and origin of stressinduced leakage current in thin silicon dioxide films. J Appl Phys, 1996,80(11):6360

- [18] Samanta P, Tsz Y, Alain C K, et al. Direct tunneling stress-induced leakage current in nMOS devices with ultrathin gate oxides. IEEE 43rd Annual International Reliability Physics Symposium, 2005;594

- [19] Park Y B, Schroder D K. Degradation of thin tunnel gate oxide under constant Fowler-Nordheim current stress for a flash EEP-ROM. IEEE Trans Electron Devices, 1998, 45(6):1361

- [20] Wang T, Zous N K, Yeh C C. Role of positive trapped charge in stress-induced leakage current for flash EEPROM devices. IEEE Trans Electron Device, 2002, 49(11), 1910

- [21] Takagi S, Yasuda N, Toriumi A. Experimental evidence of inelastic tunneling in stress-induced leakage current. IEEE Trans Electron Devices, 1999, 46(2):335

- [22] Kang T K, Chen M J, Liu C H, et al. Numerical confirmation of inelastic trap-assisted tunneling (ITAT) as SILC mechanism. IEEE Trans Electron Devices, 2001, 48(10):2317

- [23] Rosenbaum E, Register L F. Mechanism of stress-induced leakage current in MOS capacitors. IEEE Trans Electron Devices, 1997, 47 (2):317

- [24] Tsujikawa S. SILC and NBTI in pMOSFETs with ultrathin SiON gate dielectrics. IEEE Trans Electron Devices, 2007, 54(3):524

- [25] Zhang Heqiu, Xu Mingzhen, Tan Changhua. Stress induced leakage current in different thickness ultrathin gate oxide MOSFET. Chinese Journal of Semiconductors, 2004, 25(3):257

- [26] Yang Guoyong, Huo Zongliang, Wang Jinyan, et al. Experimental evidence of interface-trap-related SILC in ultrathin (4nm- and 2.5nm-thick) n-MOSFET and p-MOSFET under hot-carrier stress. Chinese Journal of Semiconductors, 2003, 24(6):131

# 直接隧穿应力下超薄栅氧 MOS 器件退化\*

胡仕刚\* 郝 跃 马晓华 曹艳荣 陈 炽 吴笑峰

(西安电子科技大学微电子学院 宽禁带半导体材料与器件教育部重点实验室, 西安 710071)

摘要:研究了栅氧厚度为 1.4nm MOS 器件在恒压直接隧穿应力下器件参数退化和应力感应漏电流退化.实验结果表明,在不同直接隧穿应力过程中,应力感应漏电流(SILC)的退化和  $V_{th}$ 的退化均存在线性关系.为了解释直接隧穿应力下 SILC 的起因,建立了一个界面陷阱和氧化层陷阱正电荷共同辅助遂穿模型.

关键词: 阈值电压; 界面陷阱; 直接隧穿; 应力感应漏电流

PACC: 7340G; 7320; 7340Q

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177(2008)11-2136-07

<sup>\*</sup> 国家自然科学基金资助项目(批准号:60736033,60506020)

<sup>†</sup> 通信作者.Email:hsg99528@126.com 2008-05-16 收到,2008-06-23 定稿