## An Improved Description of Characteristics Length in Substrate Current Model for Submicron and Deep-Submicron LDD MOSFET's\*

Yu Chunli, Yang Lin'an and Hao Yue

(Microelectronics Institute, Xidian University, Xi'an 710071, China)

Abstract: A novel substrate current model is proposed for submicron and deep-submicron lightly-doped-drain (LDD) n-MOSFET, with the emphasis on accurate description of the characteristics length by taking the effects of channel length and bias into account. This is due to that the characteristics lenth significantly affects the maximum lateral electric field and the length of velocity saturation region, both of which are very important in modeling the drain current and the substrate current. The comparison between simulations and experiments shows a good prediction of the model for submicron and deep-submicron LDD MOSFET. Moreover, the analytical model is suitable for descgn of devices as it is low in computation consumption.

Key words: LDD MOSFET; substrate current; characteristics length; maximum lateral electric field

PACC: 7220H, 7230 EEACC: 2560B, 2560R

#### 1 Introduction

Substrate current is a very sensitive parameter to monitoring the hot carrier degradation in scaling down devices to deep submicron. The lightly-doped-drain (LDD) process technology finds wide applications in the improvement of hot carrier immunity. However, the substrate current in LDD MOSFET still demonstrates a unique characteristics different from the conventional MOSFET, particularly in very short gate length devices. The modeling of substrate current for LDD structure is therefore different from that for conventional S/D

structure devices. Many publications in this area have given a great deal of experiments and analysis<sup>[1-5]</sup>, nevertheless, lack of clear differences in modeling mechanism between LDD and conventional S/D structures. In details, the modeling of n<sup>-</sup> doped region induced effective channel length, the modeling of velocity saturation region length, the modeling of threshold voltage and saturation voltage, etc., should be paid more attention to LDD structure. References [3~5] demonstrate the improved substrate current models, but not especially for LDD devices.

In this paper we investigate the mechanism of the substrate current of LDD MOSFET, and put

<sup>\*</sup> Project supported by National Natural Science Foundation of China (No. 60206006)

Yu Chunli female, PhD candidate. Her research interests focus on the reliability and modeling of deep-submicron devices.

Yang Lin'an male, PhD. His research interests include reliability of deep-submicron devices and modeling & fabrication of microwave power devices based on wide band gap semiconductor materials.

Hao Yue male, professor. His research interests include IC reliabilit, manufacturability, methodology for IC design, and new type of semiconductor devices and circuits.

the emphasis on the modification of the characteristics length which is also defined as the effective ionization length in some papers. The characteristic length significantly affects the modeling of drain current and substrate current for the MOSFET from long channel to short channel. Thus many papers have to utilize the extracted empirical descriptions to pursue the model accuracy. To this end, a modified characteristics length model of LDD MOSFET is developed which is suitable for the description of submicron and deep-submicron devices, and is implemented in the proposed drain current and substrate current models. The related experiments are compared with the simulation results as validity.

# 2 Improved model of characteristics length

An accurate description of maximum lateral electric field  $E_m$  is extremely important for calculating the substrate current. From quasi two-dimensional simulation,  $E_m$  is given as  $^{[6]}$

$$E_{\rm m} = \sqrt{\left[\frac{V_{\rm ds} - V_{\rm dsat}}{l}\right]^2 + E_{\rm c}^2} \tag{1}$$

where  $V_{\rm dsat}$  and  $E_{\rm c}$  are saturation voltage and critical saturation electric field, respectively. If the critical saturation electric field  $E_{\rm c}$  is neglected, it is simplified to Eq. (2) which is widely used in modeling substrate current shown as

$$E_{\rm m} \approx \frac{V_{\rm ds} - \eta V_{\rm dsat}}{I} \tag{2}$$

where l is defined as the characteristics length (or effective ionization length), a very important parameter in modeling the maximum electric field. The emphasis in this paper is in turn put on the description of characteristics length for the MOSFETs with different gate lengths and structures.  $\eta$  is an adjustable parameter close to unity to fit the experiment.

In solving the distribution of channel electric field, the parameter l is normally defined as

$$l = \sqrt{\frac{\epsilon_{\rm si}}{\epsilon_{\rm ox}} t_{\rm ox} x_{\rm j}} \tag{3}$$

where  $t_{ox}$  and  $x_j$  are the gate oxide thickness and the S/D junction depth (n region junction depth for LDD MOSFET), respectively. However, this expression yields a significant dispersion as the LDD device is scaled down to submicron or deep-submicron regime. Many experiment-based modification methodologies therefore have been developed to improve the model accuracy. Some empirical expressions are given as follows [7]:

$$l = 0.0007x_{\rm i}^{1/3}t_{\rm ox} \tag{4}$$

where  $x_j$  and l are in micrometers,  $t_{ox}$  is in angstroms. It is suitable for short channel length LDD or conventional MOSFET.

$$l = 0.22x_{\rm j}^{1/2}t_{\rm ox}^{1/3[8]} \tag{5}$$

where l,  $x_j$ , and  $t_{0x}$  are in centimeters. Equation (4) is suitable for long channel devices, although occasionally being used in submicron devices.

In practice, the parameter l is gate bias—and drain bias-dependent. Thus an empirical bias-dependent model is developed as<sup>[9]</sup>

$$l=l_0+l_1(V_{\rm ds}-V_{\rm dsat})+l_2(V_{\rm ds}-V_{\rm dsat})^2$$

(6) where  $l_0, l_1$ , and  $l_2$  are fitting parameters. Furthermore, the third order is even considered in some fitting models.

The measurements of  $E_{\rm m}$  against  $V_{\rm gs}$  and  $V_{\rm ds}^{[1,2]}$  demonstrate that  $E_{\rm m}$  is approximately proportional to  $V_{\rm gs}$ , and also l is approximately proportional to  $V_{\rm gs}$ , and also l is approximately proportional to  $V_{\rm gs}$  in short gate length LDD MOSFET's. The parameter l affects not only the maximum lateral electric field, but also the threshold voltage  $V_{\rm th}$ . In this paper, we develop an equivalent model of characteristics length l which takes the bias and the channel length into account, universally suitable for submicron and deep-submicron regiem, given as

$$l = l_0[a_1L_{\rm eff}^{1/5} + a_2V_{\rm gs}(V_{\rm ds} - V_{\rm dsat})^2]$$

(7) where  $l_0$  and  $L_{\rm eff}$  are in micrometers, defined as the effective characteristics length and the effective channel length of submicron and deep-submicron LDD MOSFET, respectively.  $l_0$  is given by Eq. (4)

which holds the accuracy in short channel LDD devices. The first term in the square bracket of Eq. (7) indicates that *l* is related to the gate length. Experimentally, the characteristics length l increases nonlinearly as the gate length increases. From submicron to deep-submicron regime, the change is not apparent, and the gate length-independent empirical model is in turn well used. In the micron regime, the difference of l is larger. This can also be evidenced by Eqs. (3), (4), and (5). Thus the exponent 1/5 is proposed to fit the effect of gate length on the characteristics length l in a wide range from micron to deep-submicron. The second term in the square bracket of Eq. (7) indicates that the practical characteristics length l is nearly proportional to the gate bias [7]. The drain bias-dependent factor is also considered in this term in which the square factor is close to the reality.  $a_1(\mu m^{-1})$ and  $a_2(V^{-3})$  are fitting parameters. Then, this model is implemented in  $l_d$  and  $V_{th}^{[10]}$ , to model the substrate current of the LDD MOSFET from submicron to deep submicron regime.

# 3 Modeling of substrate current for LDD MOSFET's

Theoretically, the formations of substrate current  $I_{\rm sub}$  are of less difference between conventional S/D and LDD MOSFET's. The key consideration of  $I_{\rm sub}$  model for LDD MOSFET is in both modeling of I-V characteristics in which the parameters such as parasitic series resistance, effective channel length, and threshold voltage shift, etc., are included for LDD technology and implementation of  $I_{\rm sub}$ . The commonly used description of substrate current  $I_{\rm sub}$  taking the Eq. (2) into account is given by  $I_{\rm sub}$ .

$$I_{\text{sub}} = I_{\text{ds}} \times \frac{A_{\text{i}}}{B_{\text{i}}} (V_{\text{ds}} - \eta V_{\text{dsat}}) \exp \left[ - \frac{lB_{\text{i}}}{V_{\text{ds}} - \eta V_{\text{dsat}}} \right]$$

(8)

where  $I_{\rm ds}$  and  $V_{\rm dsat}$  are drain current, saturation voltage, respectively, and  $A_i$ ,  $B_i$  are impact ionization coefficients. The differences among many  $I_{\rm sub}$

models are in differences of the parameters  $V_{\rm dsat}$ , l and  $E_{\rm m}$ , etc. With appropriate determination of these parameters for LDD MOSFET, the  $I_{\rm sub}$  model can be used to demonstrate the hot carrier effects. The saturation voltage  $V_{\rm dsat}$  is obtained by

$$V_{\text{dsat}} = L_{\text{eff}} E_{\text{c}} \left[ \sqrt{1 + \frac{2(V_{\text{gs}} - V_{\text{th}})}{\gamma L_{\text{eff}} E_{\text{c}}}} - 1 \right]$$

(9)

where the effective channel length  $L_{\text{eff}}$ , the bulk charge factor  $\mathcal{Y}$ , and the critical saturation electric field  $E_{c}$  are shown in Refs. [11, 12].

A hyperbolic-tangent description has been developed to characterize the drain current  $I_{ds}$  for LDD MOSFET's<sup>[13]</sup>:

$I_{\rm ds}(V_{\rm gs},V_{\rm ds})=I_{\rm dsat}(1+\lambda V_{\rm ds})\,{\rm th}(\alpha V_{\rm ds})$  (10) where  $I_{\rm dsat},\alpha$  and  $\lambda$  are critical saturated drain current, saturation voltage parameter, and channel length modulation parameter, respectively. Taking the effect of source and drain parasitic resistances (these parasitic parameters are normally extracted from experiments rather than calculations because of their complicity for LDD MOS structure) into account, the iteration methodology is used to solve the nonlinear function Eq. (10) where the Gauss Newton and the Levenberg Marquardt optimization algorisms are utilized.

# 4 Simulation results of $I_{\text{sub}}$ model and validity

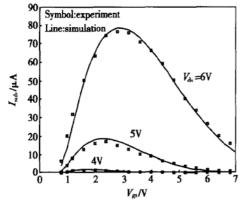

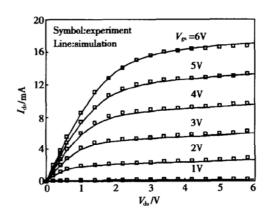

All the proposed parameters are implemented in the model to simulate the characteristics of short gate length of LDD NMOSFETs and the results are compared with the experiments. Figure 1 shows the substrate current of  $W/L_{\rm eff}=55\mu{\rm m}/0.62\mu{\rm m}$  LDD MOSFET, in which the gate oxide thickness  $t_{\rm ox}$  equals 25nm, the junction depth of n region  $x_{\rm j}$  equals 0.25 $\mu$ m, the extracted source and drain parasitic resistances equal 11.27 $\Omega$  and the n region and the channel region under the gate oxide of substrate are  $N_{\rm D}=1.0\times10^{18}{\rm cm}^{-3}$  and  $N_{\rm A}=4.08\times10^{16}{\rm cm}^{-3}$ , the flat band voltage  $V_{\rm FB}=-0.6{\rm V}$ , the electron mobility in the channel  $\mu_{\rm s}=604.88{\rm cm}^2/({\rm V} \cdot {\rm s})$ , respectively 11. The comparison between the ex-

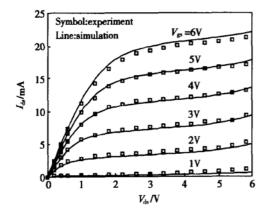

periment and the simulation illustrates a good prediction of this improved substrate model. As validity, the output drain current calculated from the model including the effect of substrate current given in Fig. 2, showing an excellent agreement be-

Fig. 1 Simulation and experiment of substrate current versus gate bias for LDD MOSFET with 0.62 $\mu$ m effective channel length at  $V_{\rm sb}$ = 0V

Fig. 2 Simulated and experimental  $I_{\rm ds}$ - $V_{\rm ds}$  characteristics of  $L_{\rm eff}$ = 0.62 $\mu$ m LDD MOSFET

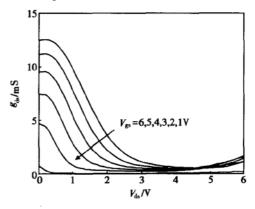

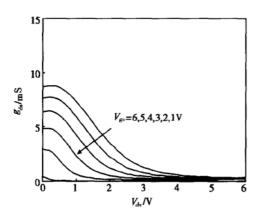

tween measurement and simulation. The simulated drain conductance is given in Fig. 3 simultaneous—ly, showing a smooth transition between linear region and saturation region, and the effect of substrate current on the drain current at large drain bias region. In this paper, the extracted parameters for substrate current simulation are given as:  $B_i$ =  $1.92 \times 10^6 \text{V/cm}$  is treated as a fixed value which is calculated from the properties of bulk silicon<sup>[9]</sup>,  $A_i$  =  $0.4 \times 10^6 \text{ cm}^{-1}$ ,  $a_1$ =  $1.15 \mu \text{m}^{-1}$ ,  $a_2$ =  $1.8 \times 10^{-3} \text{ V}^{-3}$ ,  $\eta$ = 1.05. Moreover, a micron LDD NMOS—

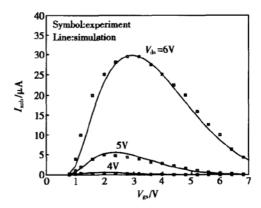

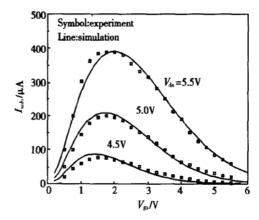

FET with  $L_{\text{eff}} = 1.02 \mu \text{m}$  is simulated by this model in Figs. 4, 5, and 6 which show the substrate current, the output I--V characteristics, and the drain

Fig. 3 Simulated drain conductance of the  $W/L_{\text{eff}}$ =  $55\mu\text{m}/0.62\mu\text{m}$  LDD MOSFET

Fig. 4 Simulation and experiment of substrate current versus gate bias for LDD MOSFET with 1.02 $\mu$ m effective channel length at  $V_{\rm sb}$ = 0V

Fig. 5 Simulated and experimental  $I_{ds}$ – $V_{ds}$  characteristics of  $L_{eff}$ = 1.02 $\mu$ m LDD MOSFET

conductance, respectively. The same extracted pa-

Fig. 6 Simulated drain conductance of the  $L_{\rm eff}$  = 1.02 $\mu$ m LDD MOSFET The effect of substrate current at large drain bias region are very small.

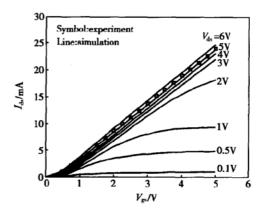

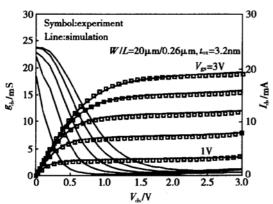

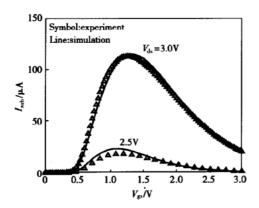

rameters are used except the drain voltage adjustable parameter  $\eta = 0.95$ . All the simulations demonstrate satisfying predictions to the reality of LDD MOSFETs, therefore presenting the robustness of the model although the effective channel length of 1.02 $\mu$ m is beyond the submicron regime. It is also obvious that the long gate length MOS-FET gives rise to the low substrate current. This is the reason that the study on the mechanism of substrate current is important for submicron and deepsubmicron devices in the reliability area. Simultaneously, the performance of a LDD MOSFET with shorter gate length ( $W/L_{\rm eff} = 40 \mu \rm m/0.32 \mu m$ ) is simulated by the model. Figure 7 shows the comparison between measurement [14] and simulation of the substrate current, resulting in good agreement. The calculated I<sub>ds</sub>-V<sub>gs</sub> curves from the linear region to saturation region are drawn in Fig. 8 with the experimental data (at  $V_{ds} = 5V$ ) as comparison. The utilized parameters in simulations are:  $t_{ox} =$  $15 \text{nm}, x_i = 0.25 \mu \text{m}, N_A = 6.2 \times 10^{16} \text{ cm}^{-3}, N_D = 1 \times 15 \text{ m}$  $10^{18} \text{ cm}^{-3}$ ,  $R_{\rm S}(R_{\rm d}) \approx 30 \Omega$ ,  $\mu_{\rm s} = 600 \text{cm}^2 / (\text{V} \cdot \text{s})$ ,  $V_{\rm FB}$ = - 0.87V, etc. The extracted parameters for substrate current simulation are given as:  $A_i = 0.38 \times$  $10^6 \text{cm}^{-1}$ ,  $B_i = 1.92 \times 10^6 \text{V/cm}$ ,  $a_1$  and  $a_2$  maintain the same value as mentioned above in extraction and equal 1. 15 and 1.  $8 \times 10^{-3}$ , and  $\eta = 1.06$  respectively. Further more, a very short gate length's LDD NMOSFET ( $W/L_{\text{mask}} = 20 \mu \text{m}/0.26 \mu \text{m}$ ) fabri-

Fig. 7 Simulation and experiment of substrate current versus gate bias for  $W/L_{\rm eff} = 40 \mu {\rm m}/0.32 \mu {\rm m}$  LDD MOSFET, where the substrate bias  $V_{\rm sb} = 0 {\rm V} \cdot {\rm A}$  large increase of  $I_{\rm sub}$  is shown compared with that in Figs. 1 and 4.

Fig. 8 Comparison between simulated  $I_{\rm ds}$ – $V_{\rm gs}$  characteristics from linear to saturation region and measurement

cated on 0.  $18\mu m$  CMOS technology is also investigated, and the good results shown in Figs. 9 and 10 are obtained. The extracted parameters by linear regression method in simulations are:  $t_{ox} = 3.2 \text{nm}$ ,  $L_{eff} = 0.23\mu m$ ,  $x_{j} = 0.03\mu m$ ,  $N_{A} = 3 \times 10^{16} \text{ cm}^{-3}$ ,  $N_{D} = 1.1 \times 10^{18} \text{cm}^{-3}$ ,  $R_{S}(R_{d}) \approx 14.5 \Omega$ ,  $\mu_{s} = 750 \text{cm}^{2}/(V \cdot s)$ ,  $V_{th} = 0.48V$ , etc. The extracted parameters for substrate current simulation are given as:  $A_{i} = 0.21 \times 10^{6} \text{cm}^{-1}$ ,  $B_{i} = 1.92 \times 10^{6} \text{V/cm}$ ,  $a_{1}$  and  $a_{2}$  maintain the same value as mentioned above in extraction and equal 1.15 and 1.8  $\times 10^{-3}$ , and  $\eta = 1.15$ , respectively. All of these investigations indicate that the improved model is suitable for the

LDD MOSFETs of a large region of gate lengths with low difference of extractions.

Fig. 9 Simulated and experimental substrate currents in 0.26 $\mu$ m gate length LDD NMOSFET ( $L_{\rm eff} \approx 0.23 \mu$ m)

Fig. 10 Simulated and experimental output drain current and drain conductance in 0.26 $\mu$ m gate length LDD NMOSFET

### 5 Conclusion

We have proposed a new description of ionization characteristics length l which is relevant to effective channel length and bias. With the improved parameter, the substrate current model and I–V characteristics model is developed to predict the performance of submicron and deep-submicron LDD n-MOSFETs. The comparison between measurements and simulations shows good agreement. Furthermore, this analytically-based model possesses an advantage of very low calculation consumption over the numerical model, suitable for the

practical design of devices.

#### References

- [1] Huang G S, Wu C Y. An analytical saturation model for drain and substrate current of conventional and LDD MOSFET's. IEEE Trans Electron Devices, 1990, 37(7): 1667

- [2] Yang J J, Chung S S, Chou P C, et al. A new approach to modeling the substrate current of pre-stressed and poststressed MOSFET's. IEEE Trans Electron Devices, 1995, 42 (6):1113

- [3] Ghalabagi R, Khalili A, Sholy B. An analytical model for lightly doped drain MOS transistors. Int J Electron, 1995, 78 (3):509

- [4] Kolatkar J S, Dutta A K. A new substrate current model for submicron MOSFET's. IEEE Trans Electron Devices, 2000, 47(4): 861

- [5] Sun Z M, Liu L T, Li Z J. Modification of MOSFET's substrate current model in deep submicrometer regime. Chinese Journal of Semiconductors, 2000, 21(2):151(in Chinese)[孙白敏, 刘理天, 李志坚. MOSFET 衬底电流模型在深亚微米尺寸下的修正. 半导体学报, 2000, 21(2):151]

- [6] Banna M E, Nokali M E. A pseudo-two-dimensional analysis of short channel MOSFETs. Solid-State Electron, 1998, 31: 269

- [7] Liu Z H, Hu C, Huang J H, et al. Threshold voltage model for deep submicron MOSFET's. IEEE Trans Electron Devices, 1993, 38(6): 1392

- [8] Chan T, Ko P, Hu C. A simple method to characterize substrate current in MOSFET's. IEEE Electron Device Lett, 1984, 5(12): 505

- [9] Arora N D, Sharma M S. MOSFET substrate current model for circuit simulation. IEEE Trans Electron Devices, 1991, 38 (6): 1392

- [10] Hu Y, Booth R V H, White M H. An analytical model for the lateral channel electric field in LDD structures. IEEE Trans Electron Devices, 1990, 37(10): 2254

- [11] Zhou X, Lim K Y, Lim D. A general approach to compact threshold voltage formulation based on 2-D numerical simulation and experimental correlation for deep-submicron ULSI technology development. IEEE Trans Electron Devices, 2000, 47(1):214

- [12] Wright G T. Physical and CAD model for the implantedchannel VLSI MOSFET. IEEE Trans Electron Devices, 1987, 34: 823

- [ 13] Yu C L, Hao Y, Yang L A. A novel empirical model of I-V characteristics for LDD MOSFET including substrate current. Chinese Journal of Semiconductors, 2004, 25(7): 778

- [14] Liu S S, Jang S L, Chyau C G. Compact LDD nMOSFET degradation model. IEEE Trans Electron Devices, 1998, 45 (7): 1538

1090 半 导 体 学 报 25 卷

### 亚微米、深亚微米 LDD MOSFET 的衬底电流模型中 特征长度改进的描述\*

#### 于春利 杨林安 郝 跃

(西安电子科技大学微电子研究所,西安 710071)

摘要:建立了衬底电流模型中特征长度参数的改进描述,该参数的引入使衬底电流模型能够有效地适用于从微米尺寸到亚微米、深亚微米尺寸的 LDD MOSFET.在以双曲正切函数描述的 1-V 特性基础上,该解析模型的运算量远低于基于数值分析的物理模型,其中提取参数的运用也大大提高了模型的精度,模拟结果与实验数据有很好的一致性.

关键词: 轻掺杂漏 MOSFET; 衬底电流; 特征长度; 最大横向电场

PACC: 7220H; 7360 EEACC: 2560B; 2560R

中图分类号: TN 386 文献标识码: A 文章编号: 0253-4177(2004)09-1084-07

<sup>\*</sup> 国家自然科学基金资助项目(批准号: 60206006)

于春利 女,博士研究生,从事深亚微米 CM OS 器件建模及可靠性应用的研究.

杨林安 男,博士,研究方向为小尺寸微波器件、宽禁带半导体材料和器件领域.

郝 跃 男, 教授, 博士生导师, 从事微电子学与半导体器件的研究.