# Degradation of pMOSFETs with Ultrathin Oxide and Different HALO Dose\*

Zhao Yao, Hu Jing, Xu Mingzhen and Tan Changhua

(Department of Microelectronics, Peking University, Beijing 100871, China)

Abstract: The effect of HALO dose on device parameter degradation of pMOSFET with 2. 1nm oxide and 0. 135µm channel length at hot carrier stress is analyzed. It is found that the degradation mechanism is not sensitive to HALO dose changing, but the degradation quantities of linear drain current, saturation drain current, and maximum transconductance increase with HALO dose enhancing and are larger than those of speculated before. The degradation of device parameters (linear drain current, saturation drain current, and maximum transconductance) is attributed to not only the drain series resistance enhancing induced by interface states under spacer oxide and carrier mobility degradation but also the threshold voltage variation and initial threshold voltage increasing with HALO dose enhancing.

Key words: hot carrier; pMOSFET; HALO; degradation

EEACC: 0170N; 2560R

#### 1 Introduction

For short channel VLSI transistors, the drain to source punch through is a serious problem when device scaling goes on continuously. HALO structure is added to prevent punch through and to improve the threshold voltage roll-off characteristic  $^{[1,2]}$ . Some results about HALO structure have been reported  $^{[3\sim5]}$ . It is found that, larger tilt implant low energy HALO devices show less degradation at hot carrier stress. However, when device characteristic dimension comes into sub-0.  $15\mu m$  and the gate oxide is ultra thin, though drain current model and hot carrier degradation of HALO

structure devices have been published<sup>[6,7]</sup>, the effect of HALO dose on device degradation at hot carrier stress has not been reported and the analytical model of drain current degradation at hot carrier stress due to HALO dose changing has not been studied carefully.

In this paper, the effect of HALO dose on pMOSFET device performance ( $I_{\rm dsat}$ ,  $I_{\rm dline}$ ,  $g_{\rm m}$ , and  $V_{\rm th}$ ) degradation under hot carrier stress is investigated. At first, the experimental set in this work is described. In the second part, the experimental results are shown to study the correlation between degradation mechanism and HALO doses after hot carrier stress. Finally, then the difference of parameter degradation quantities due to the HALO dose

<sup>\*</sup> Project supported by State Key Development Program for Basic Research of China(No. G2000-036503)

Zhao Yao male, PhD candidate. His research interest includes hot-carrier effects, small-scale MOS device modeling and characterization.

Xu Mingzhen female, professor. Her current interest includes physics and characterization of small dimension devices and reliability of semiconductor materials and devices.

changing is discussed and modeled.

### 2 Experiment

All measured devices are pMOSFETs with  $10\mu\mathrm{m}$  channel width (W) and  $0.135\mu\mathrm{m}$  channel length (L). The gate oxide thickness is about 2. Inm measured by C--V and simulation method. The test devices are divided into three groups by the HALO dose. Group I named P1, its HALO dose is minimum, group II named P2 and group III named P3, their HALO doses are respectively two and four times of the group I. Other technology conditions are similar to Ref. [5].

HP4156B semiconductor parameter analyzer and HP16440A pulse generator were used to perform the hot carrier stress, to monitor device performance degradation, and to measure charge pumping current. The stress drain bias is from - 2. 6V to - 3. 0V at room temperature. The linear drain current is extracted by biasing at  $V_{\rm g}$  = -1. 5V,  $V_d = -0.1V$ ; the saturation drain current is extracted by biasing at  $V_g = V_d = -1.5V$ ; the threshold voltage is extracted by the defined drain current  $W/L \times 10^{-7}$ A, and the maximum transconductance is extracted by the maximum differential value of the transfer characteristic curves in linear region. The saturation drain current degradation  $\mathrm{d}I_{\mathrm{dsat}}(\Delta I_{\mathrm{dline}}/I_{\mathrm{dsat0}})$ , the linear drain current degradation  $dI_{\text{dline}}(\Delta I_{\text{dline}}/I_{\text{dline}})$ , the threshold voltage variation  $\Delta V_{\text{th}}(V_{\text{th}}-V_{\text{th0}})$ , and the maximum transconductance degradation  $dg_{m}(\Delta g_{m}/g_{m0})$  are examined to characterize the device performance degradation at hot carrier stress.

#### 3 Results and discussion

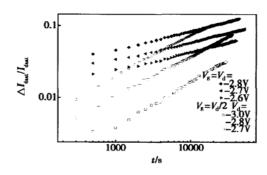

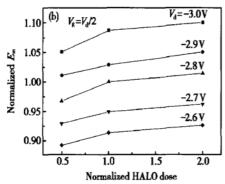

Figure 1 shows the  $I_{\rm dsat}$  degradation of P3 under  $V_{\rm g} = V_{\rm d}$  and  $V_{\rm g} = V_{\rm d}/2$  stress modes, the drain bias is from  $-2.6{\rm V}$  to  $-3.0{\rm V}$ . In this plot, at the same stress mode, the higher the stress voltage, the higher the saturation drain current degradation, also, the degradation lines are parallel to each other.

Fig. 1  $I_{dsat}$  degradation of devices with HALO dose P3 under  $V_g = V_d$  and  $V_g = V_d/2$  stress modes

It can be seen that all characteristic lines follow the well-known power law<sup>[8]</sup>. The relationship can be written as

$$\Delta = A t^{n} \tag{1}$$

where  $\Delta$  is the parameter degradation quantity, t is stress time, n is the degradation time factor which is sensitive to degradation mechanism and technology. It can also be seen that all degradation lines at each stress mode fit well, the degradation time factor, n, under  $V_{\rm g} = V_{\rm d}$  stress mode is about 0.3 by linear fit, but n is about 0.6 under the  $V_{\rm g} = V_{\rm d}/2$  stress mode. It indicates that  $V_{\rm g} = V_{\rm d}/2$  stress mode is the worst-case stress mode after long time accelerated stress, so following studies would focus on  $V_{\rm g} = V_{\rm d}/2$  stress mode.

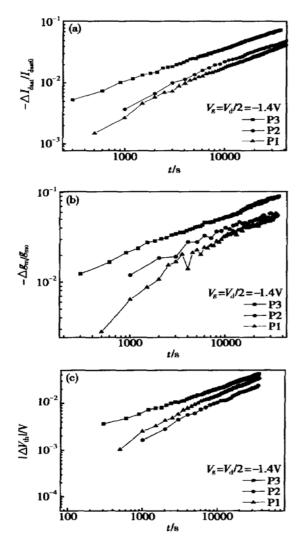

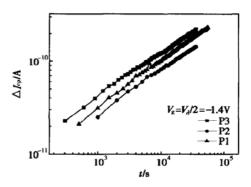

The saturation drain current degradation of P1, P2, and P3 stressed under  $V_g = V_d/2 = -1.4V$  is shown in Fig. 2(a). The three degradation lines are parallel and the degradation quantity increases as HALO dose increases. For other biased drain voltages from -3.0V to -2.6V, the experimental results are similar. Using other parameters characterizing the devices degradation, such as the degradation of maximum transconductance in Fig. 2(b) and threshold voltage variation in Fig. 2(c), the same degradation law can be found. Thus, it can be concluded that the degradation mechanism is not sensitive to the changing of HALO dose, while the parameter degradation quantities are sensitive to the changing of HALO dose.

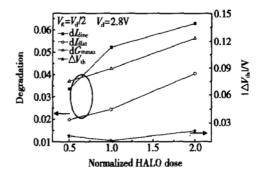

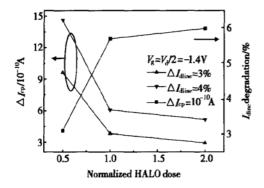

In Fig. 3, the  $\mathrm{d}I_{\mathrm{dline}}$ ,  $\mathrm{d}I_{\mathrm{dsat}}$ ,  $\mathrm{d}g_{\mathrm{m}}$ , and  $\Delta V_{\mathrm{th}}$  versus

Fig. 2  $I_{\rm dsat}$  degradation (a),  $g_{\rm m}$  degradation (b), threshold voltage variation (c) of devices with HALO dose P1, P2, and P3 under  $V_{\rm g} = V_{\rm d}/2$  stress mode

normalized HALO dose stressed at  $V_g = V_d/2 = -1.4V$  stress mode after 12000s is plotted.

$I_{\rm dsat}, I_{\rm dline}$ , and  $g_{\rm m}$  degradation increase with the HALO dose increasing, which are different from using 0.2 $\mu$ m technology with extension HALO implants and a physical oxide thickness of 3.5nm reported in Ref. [5]. But the threshold volt-

Fig. 3 d $I_{\rm dine}$ , d $I_{\rm dsat}$ , and d $g_{\rm m}$  and  $\Delta V_{\rm th}$  versus normalized HALO dose stressed at  $V_{\rm g}$ =  $V_{\rm d}/2$ = - 1.4V after 12000s

age variations are less than 10mV. The parameter degradations at other stress voltages from -3.0V to -2.6V are similar. So, the following study of HALO dose effect will focus on the degradation of  $dI_{\text{dline}}$ ,  $dI_{\text{dsat}}$ , and  $dg_{\text{m}}$ .

To investigate the experimental results, the correlation between HALO doses and channel electric field should be studied first. As we know, with enhanced HALO dose, the threshold voltage will be higher. By three-transistor threshold voltage model<sup>[9]</sup>, the threshold voltage can be expressed by:

$$V_{\text{th}} = V_{\text{te}} + \frac{kT}{q} \ln \left[ 1 + \frac{2L_{\text{h}}}{L} \left( e^{\frac{q}{kT}(V_{\text{thALO}} - V_{\text{te}})} - 1 \right) \right]$$

(2)

$$V_{\text{thALO}} = V_{\text{fb}} + 2\Phi_{\text{f}} + \gamma \sqrt{2\Phi_{\text{f}} + V_{\text{sb}}} = V_{\text{FB}} + 2\frac{kT}{q} \ln \frac{N_{\text{b}}}{N_{\text{i}}} + \gamma \sqrt{2\frac{kT}{q} \ln \frac{N_{\text{b}}}{N_{\text{i}}} + V_{\text{sb}}}$$

(3)

where  $V_{\text{te}}$  is the channel region threshold voltage,  $V_{\text{tHALO}}$  is the HALO region threshold voltage;  $L_{\text{h}}$  is the HALO region length;  $N_{\text{b}}$  is the HALO region substrate concentration. For different HALO doses,  $V_{\text{te}}$  is constant, but  $V_{\text{tHALO}}$  increases when HALO dose becomes larger.

So the saturation drain voltage  $V_{\rm dsat}$ , which can be expressed by  $^{[10]}$

$$V_{\text{dsat}} = \frac{|V_{\text{g}} - V_{\text{th}}|}{|V_{\text{g}} - V_{\text{th}}| + L_{\text{eff}} E_{\text{c}}} = \frac{1}{\frac{1}{L_{\text{eff}} E_{\text{c}}} + \frac{1}{|V_{\text{g}} - V_{\text{tc}} - \frac{kT}{q} \ln\left[1 + \frac{2L_{\text{h}}}{L} \left(e^{\frac{q}{kT}(V_{\text{tHALO}} - V_{\text{tc}})} - 1\right)\right]}}$$

(4)

Then, the maximum lateral electric field is:

$$E_{\rm m} \approx \frac{V_{\rm d} - V_{\rm dsat}}{l} \tag{5}$$

it will become larger with the increasing of HALO dose.

The substrate current is decided by the maxi-

mum electric field[11].

$$\frac{I_{\rm b}}{I_{\rm d}} = c e^{-\frac{Bi}{E_{\rm m}}} \tag{6}$$

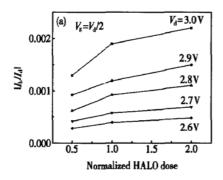

When the HALO dose increases, the maximum electric field augments, the  $I_b/I_d$  will strengthen at the same bias with HALO dose increasing. The experimental results are shown in Fig. 4(a) and the bigger  $|V_d|$ , the larger  $I_b/I_d$ . Figure 4(b) is the calculated lateral electric field versus HALO doses, which directly proves that the maximum lateral electric field,  $E_m$ , increases with the HALO dose increasing which leads to the increasing of degradation.

Fig. 4  $I_b/I_d$  versus normalized HA-LO dose (a) and the calculated maximum electric field versus normalized HALO dose (b) when biased on  $V_g = V_d/2$  mode

Additionally, the impact ionization mainly generated at the peak spot of electric field, because the maximum electric field locates in the LDD region, the interface states and charges trapping will be mainly produced there. Generally speaking, when the gate oxide thickness is below 4.5nm, the oxide

trapping is negligible<sup>[12]</sup>. In this paper, the gate oxide thickness of all test devices is 2. 1nm, so all device degradations are mainly influenced by interface states<sup>[13]</sup>.

Figure 5 shows the correlation between stress time and charge pumping current variation of P1, P2, and P3. The tested devices were biased at  $V_g$ =  $V_d/2$  mode and the drain bias is -2.8V.

Fig. 5 Charge-pumping current variation versus the stress time when stress at  $V_g = V_d/2$  stress mode The drain bias is -2.8V.

Figure 5 shows that  $\Delta I_{\text{sp}}$  of P3 is the biggest,  $\Delta I_{\text{sp}}$  of P2 is the smallest. That is to say, the enhancing lateral maximum electric field does not necessarily lead to generate more interface states with HALO dose increasing.

The generated interface state density can be described by [11]

$$N_{it}(t) = C \left[ t \frac{I_{ds}}{W} e^{-\frac{Bi}{E_m}} \right]^m$$

(6)

where C is a fitting constant, t is stress time, and m is a simulation parameter. m is about 0.48 in our experiments. The generated interface state density is a function of both impact ionization rate and drain current. From the above discussion, the maximum lateral electric field increases with increased HALO dose, but the drain current will decrease for the enhanced threshold voltage. Thus, the lateral maximum electric field enhancing does not necessarily lead to more interface states with increased HALO dose, just like what are described in Ref. [5] that the increased HALO doping concentration

does not necessarily lead to more defect generations.

In Fig. 6, at the same linear drain current degradation, such as 3% or 4%, the charge pumping current variation decreases with HALO dose increasing, and at the same charge pumping current variation, the linear drain current degradation increases and trends to saturate with HALO dose increasing.

Fig. 6 Relationship between  $\Delta I_{\rm cp}$ , -  $\Delta I/I_{\rm dline0}$ , and normalized HALO dose

According to the well known two-stage degradation model<sup>[14]</sup>, the generated interface states are distributed over channel region and under spacer oxide region. The interface states under spacer oxide region increase the drain series resistance; the interface states near the drain edge decrease the carrier mobility.

As we know, I dline can be described as [15]

$$I_{\text{dline}} = \mu_0 C_{\text{ox}} \frac{W}{L} (V_g - V_{\text{th0}} - 0.5V_d) V_d$$

(7)

But, after hot carrier stress,  $I_{

m dline}$  should be written

$$I_{\text{dline}}' = \frac{\mu_0}{1 + \beta N_{it}} C_{\text{ox}} \frac{W}{L} [V_g - (V_{\text{th0}} + \Delta V_{\text{th}}) - 0.5 V_d'] V_d'$$

(8)

where  $V_{\rm d}'=V_{\rm d}-I_{\rm d}\Delta R_{\rm d}$  is the effective drain voltage dropped into the source and channel region,  $\Delta R_{\rm d}$  is the increased drain series resistance caused by interface states under the spacer silicon oxide, it decreases the effective drain voltage. Here threshold voltage and the carrier mobility becomes  $V_{\rm th0}+\Delta V_{\rm th}$

and  $\frac{\mu_0}{1+\beta N_{ii}}$  respectively because of generated interface states, where  $\beta$  is a fitting constant and varies with different HALO doses.

Then the linear drain current degradation can be described as

$\Delta I_{\text{dline}}/I_{\text{dline}0} =$

$$\frac{V_{d} - I_{d}\Delta R_{d}}{1 + \beta N_{it}} \left[ \frac{1}{V_{d}} + \frac{0.5I_{d}\Delta R_{d}}{(V_{g} - V_{th0} - 0.5V_{d})V_{d}} - \frac{\Delta V_{th}}{(V_{g} - V_{th0} - 0.5V_{d})V_{d}} \right] - 1$$

(9)

From equation (9), the linear drain current degradation is a function of drain series resistance  $\Delta R_d$ , threshold voltage V<sub>th0</sub>, and threshold voltage variation  $\Delta V_{\text{th}}$ .  $\Delta R_{\text{d}}$  trends to saturate after long time stress and increases with HALO dose increasing. In our experiments  $\Delta R_d$  is less than  $20\Omega$  extracted by S&R method<sup>[15]</sup> and the maximum difference of  $\Delta R_d$ between P1, P2, and P3 is about 14Ω. The linear drain current,  $I_d$ , which are about 0.45, 0.5, and 0.65mA for P3, P2, and P1, respectively. The threshold voltages of P3, P2, and P1 before hot carrier stresses are about - 0.4, - 0.3, and - 0. 1V, respectively. The threshold voltage variations  $\Delta V_{\text{th}}$  of devices with different HALO doses are about 20mV. Thus with the threshold voltages increasing, the linear drain current degradation increases. In other words, the increasing threshold voltage mainly affects the linear drain current degradation as HALO dose increases. Because the threshold voltage of P2 and P3 are close and larger than that of P1, the linear drain current degradations increase with HALO dose increasing and trend to saturate. With suitable fitting parameter  $\beta$ , the calculated linear drain current degradations by equation (9) are consistent to experimental results.

Similarly, the  $I_{\text{dsat}}$  can be expressed as [15]

$$I_{\text{dsat}} = \mu_0 \frac{W}{L} C_{\text{ox}} (V_{\text{g}} - V_{\text{th0}})^2 (1 + \lambda V_{\text{d}})$$

After hot carrier stress,  $I_{

m dsat}$  should be written

$$I_{\text{dsat}}' = \frac{\mu_0}{1 + \beta N_{\text{it}}} \times \frac{W}{L} C_{\text{ox}} [V_{\text{g}} - (V_{\text{th}0} + \Delta V_{\text{th}})]^2 \times$$

$$[1 + \lambda(V_d - I_d\Delta R_d)]$$

Then

$$\Delta I_{\text{dsat}}/I_{\text{dsat0}} = \frac{1}{1 + \beta N_{ii}} \left[ \frac{V_{\text{g}} - V_{\text{th0}} - \Delta V_{\text{th}}}{V_{\text{g}} - V_{\text{th0}}} \right]^{2} \times \left[ 1 - \frac{\lambda I_{\text{d}} \Delta R_{\text{d}}}{1 + \lambda V_{\text{d}}} \right] - 1$$

(10)

Also,  $g_m$  can be expressed as [15]

$$g_{\rm m} = 2\mu_0 \frac{W}{L} C_{\rm ox} (V_{\rm g} - V_{\rm th0}) (1 + \lambda V_{\rm d})$$

After hot carrier stress,

$$g_{\text{m}}' = \frac{2\mu_0}{1 + BN_{\text{it}}} \times \frac{W}{L} C_{\text{ox}} [V_{\text{g}} - (V_{\text{th0}} + \Delta V_{\text{th}})] \times [1 + \lambda (V_{\text{d}} - I_{\text{d}} \Delta R_{\text{d}})]$$

So, gm degradation should be

$$\Delta g_{\rm m}/g_{\rm m0} = \frac{1}{1 + \beta N_{\rm it}} \left[ \frac{V_{\rm g} - V_{\rm th0} - \Delta V_{\rm th}}{V_{\rm g} - V_{\rm th0}} \right] \times \left[ 1 - \frac{\lambda I_{\rm d} \Delta R_{\rm d}}{1 + \lambda V_{\rm d}} \right] - 1$$

(11)

here  $\lambda$  is the channel length modulation factor.

From equations (10) and (11), the saturation drain current degradation and the maximum transconductance degradation are also associated with the drain series resistance, threshold voltage and threshold voltage variation. Because  $\lambda$  is about 0. 1V and  $I_{\rm d}$  is about  $10^{-3}{\rm A}$ , thus  $\lambda I_{\rm d}\Delta R_{\rm d}\ll 1+\lambda V_{\rm d}$ , and the effect of  $\frac{\lambda I_{\rm d}\Delta R_{\rm d}}{1+\lambda V_{\rm d}}$  is negligible, so the  $I_{\rm dsat}$  and  $g_{\rm m}$  degradation are also mainly determined by threshold voltage and threshold voltage variation.

#### 4 Conclusion

In this paper, the effect of HALO dose on device degradation of pMOSFET with 2.1nm ultrathin gate oxide and 0.135  $\mu$ m channel length under  $V_g = V_d/2$  stress mode is investigated. As the HALO dose increases, the drain current decreases and the threshold voltage increases. After HCI stress, the device degradation mechanism is not sensitive to HALO dose changing, but the device parameter degradation worsens with HALO doses increasing and the difference of parameter degradation quantity is larger than that of speculated in published reference [5]. The analytical expressions of the device

parameter ( $dI_{dline}$ ,  $dI_{dsat}$ ,  $dg_m$ ) degradation are modeled and discussed. The parameter degradations  $(dI_{dline}, dI_{dsat}, dg_m)$  are attributed to drain series resistance increasing and carrier mobility reduction caused by interface states. The quantities of device parameter degradation are determined by the evolution of drain series resistance, threshold voltage, and threshold voltage variation. Though the generated interface states do not necessarily increase with HALO dose increasing, the initial threshold voltage plays an important role in the degradation and determines the parameter degradation finally. So, when the HALO structure is used to reduce the device short channel effect and restrain punchthrough, the lower HALO dose should be chosen to decrease the device parameter degradations.

**Acknowledgment** Thanks to Motorola company for providing test samples and measurement equipments.

#### References

- [1] Cao K M, Liu W, Jin X, et al. Modeling of pocket implanted MOSFETs for anomalous analog behavior. IEDM Tech Dig, 1999, 1:171

- [2] Mii Y, Rishton S, Taur Y, et al. Experimental high performance sub-0. 1μm channel n-MOSFET's. IEEE Electron Device Lett, 1994, 15(1): 28

- [3] Hwang H, Lee D H, Hwang J M. Degradation of MOSFETs drive current due to HALO ion implantation. IEDM Tech Dig, 1996, 1: 567

- [4] Zanchetta S, Todon A, Abramo A, et al. Analytical and numerical study of the impact of HALOs on short channel and hot carrier effects in scaled MOSFETs. Solid-State Electron, 2002, 46(3): 429

- [5] Das A, De H, Misra V. Effects of HALO implant on hot carrier reliability of sub-quarter micron MOSFET's. IEEE 36th IRPS, 1998; 189

- [6] Koo H, Lee K, Lee K, et al. Analysis of the anomalous drain current characteristics of HALO MOSFETs. Solid-State Electron, 2003, 47(1):99

- [7] Hu Jing, Zhao Yao, Xu Mingzhen, et al. Influence of device narrowing on HALO-pMOSFETs' degradation under V<sub>g</sub> = V<sub>d</sub>/2 stress mode. Chinese Journal of Semiconductors, 2003, 24(12): 1255

- [8] Takeda E, Suzuki N. A empirical model for device degradation

- due to hot-carrier injection. IEEE Electron Device Lett, 1983, 4(4):111

- [9] Rios R, Shih W K, Shah A, et al. A three-transistor threshold voltage model for HALO processes. IEDM Tech Dig, 2002, 1:113

- [10] Sodini C G, Ko P K, Moll J L. The effect of high fields on MOS device and circuit performance. IEEE Trans Electron Devices, 1984, 31(10): 1386

- [11] Hu C, Tam S C, Hsu F C, et al. Hot-electron-induced MOS-FET degradation -model, monitor and improvement. IEEE Trans Electron Devices, 1985; 32(2):375

- [12] Brozek T, Lum E B, Viswannthan C R. Oxide thickness dependence of hole trap generation in MOS struture under

- high-field electron injection. Microelectron Eng, 1997, 36: 161

- [13] Li E, Rosenbaum E, Tao J, et al. Projecting lifetime of deep submicron MOSFET's. IEEE Trans Electron Devices, 2001, 48(4): 671

- [14] Chan V H, Chung J E. Two-stage hot-carrier degradation and its impact on sub micrometer LDD NMOSFET lifetime prediction. IEEE Trans Electron Devices, 1995, 42(5): 957

- [15] Schichman H, Hodges D A. Modeling and simulation of insulated-gate field-effect transistor switching circuits. IEEE Solid-State Circuits, 1968, 3: 285

- [16] Taur Y, Zicherman D S, Lombardi D R, et al. A new Shift and Ratio" method for MOSFET channel-length extraction. IEEE Electron Device Lett, 1992, 13(5): 267

## 不同 HALO 掺杂剂量的超薄栅 pMOSFET 的退化\*

赵 要 胡 靖 许铭真 谭长华

(北京大学微电子学系, 北京 100871)

摘要: 研究了热载流子应力下栅厚为 2. 1nm, 栅长为 0. 135μm 的 pM OSFET 中 HALO 掺杂剂量与器件的退化机制 和参数退化的关系. 实验发现, 器件的退化机制对 HALO 掺杂剂量的改变不敏感, 但是器件的线性漏电流、饱和漏电流、最大跨导的退化随着 HALO 掺杂剂量的增加而增加. 实验同时发现, 器件参数的退化不仅与载流子迁移率的退化、漏串联电阻增大有关, 而且与阈值电压的退化和应力前阈值电压有关.

关键词: 热载流子; pMOS 器件; HALO 结构; 退化

EEACC: 0170N; 2560R

中图分类号: TN 386 文献标识码: A 文章编号: 0253-4177(2004)09-1907-07

<sup>\*</sup> 国家重点基础研究发展计划资助项目(批准号: G2000-036503)

赵 要 男,博士研究生,主要研究小尺寸器件的热载流子可靠性.

许铭真 女,教授,主要从事小尺寸器件特性及其表征、半导体材料可靠性物理和器件可靠性物理的研究.

谭长华 男, 教授, 主要从事小尺寸器件物理及可靠性物理的研究.