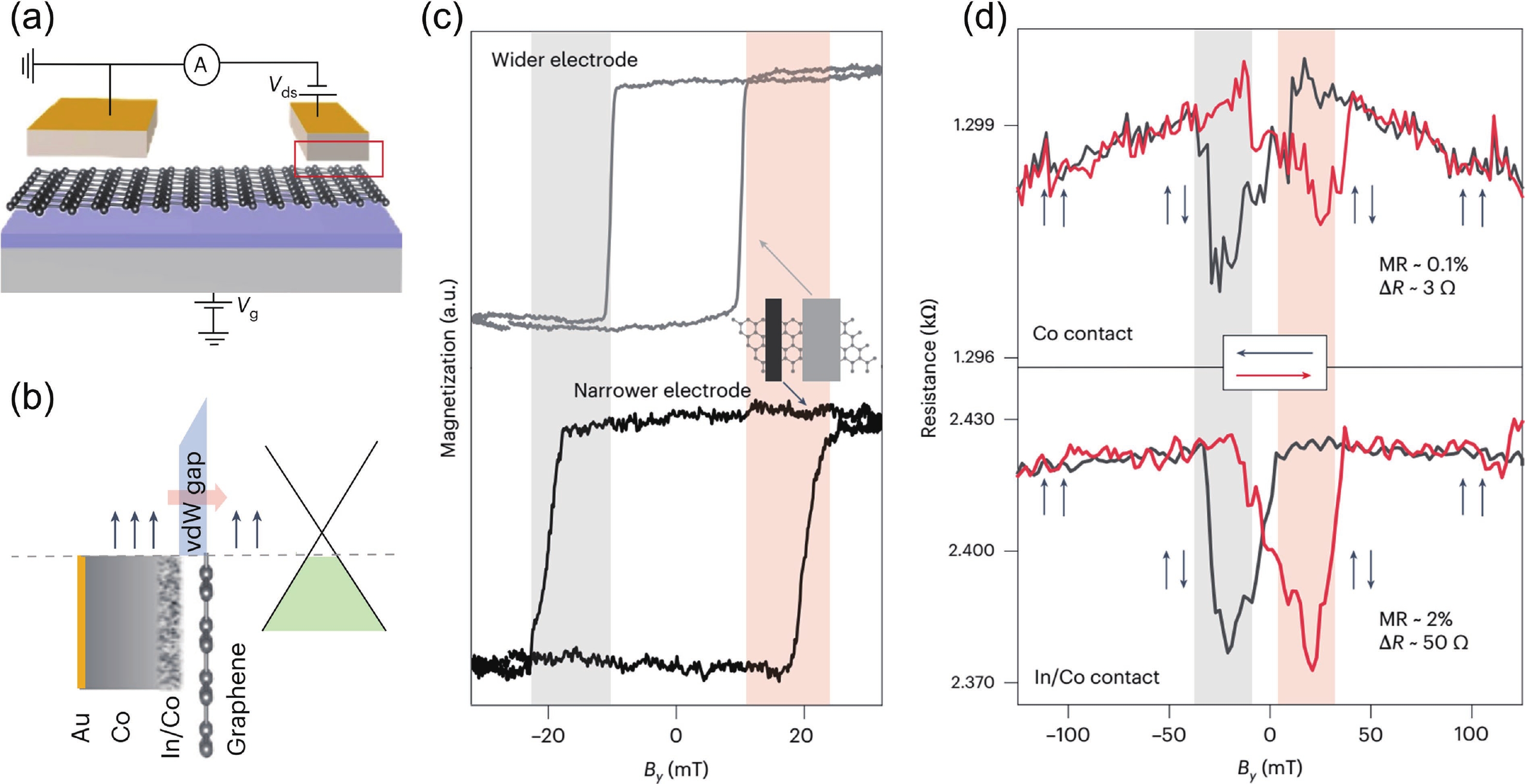

The integration of two-dimensional (2D) semiconductors with mainstream complementary metal-oxide-semiconductor (CMOS) technology is hampered by the limited ability to adjust device performance after fabrication. Here, we present a differential Schottky-barrier tuning strategy to post-customize the optoelectronic performance based on a two-dimensional asymmetric Schottky contact WSe2 photodiode, eliminating the need for device re-fabrication. A brief, room-temperature ozone exposure (1.5 min) enables in-situ tuning of the rectification ratio across three orders of magnitude (from 102 to 105) and enhances the peak responsivity at 532 nm by 11.2 times. These effects stem from differential modulation of Schottky barrier height (SBH) at the asymmetric contacts. While the SBH at the WSe2/Au interface is reduced, the SBH at the WSe2/graphene junction is elevated, a phenomenon unlocked by the combination of oxidation-induced Fermi-level lowering in WSe2 and interfacial dipole modification. Our method establishes a "device-after-design" paradigm for 2D material engineering, providing a CMOS-compatible and versatile route toward adaptive optoelectronics for applications in wearable sensing and reconfigurable photonic systems.

Just Accepted manuscripts are peer-reviewed and accepted for publication. They are posted online prior to technical editing formatting for publication and author proofing.

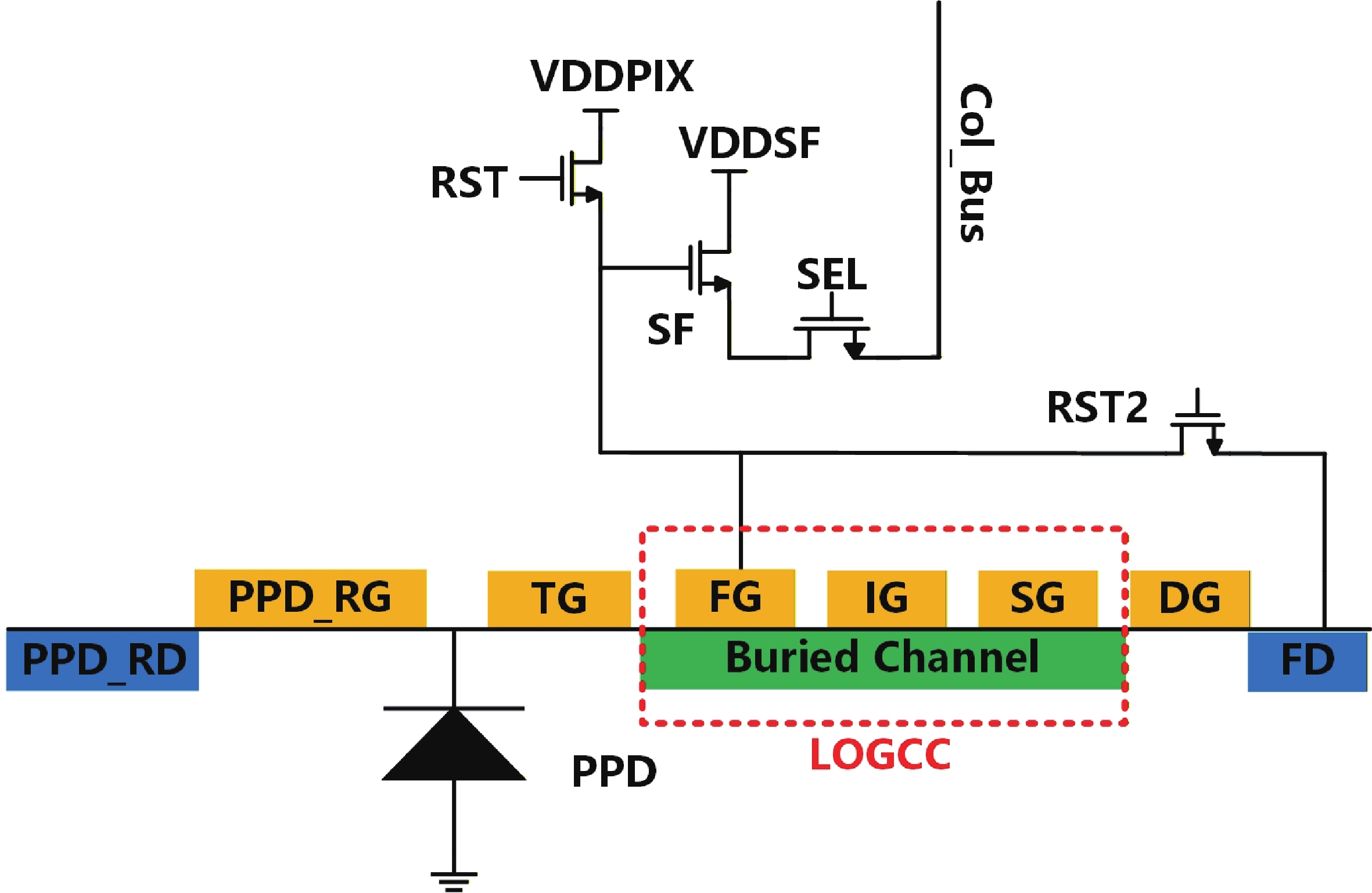

A skipper image sensor (SIS) with lateral overflow gate-coupled capacitor (LOGCC) is proposed in this work. During the integration period, the transfer gates after TG are switched on to construct a LOGCC with specific operation timing. Once high light illumination fully charges the pinned photodiode (PPD), the extra photogenerated electrons will overflow to LOGCC, which effectively improve the dynamic range (DR) of SIS. Before the readout of signal in PPD, the electrons stored in LOGCC are sampled and then reset through the floating diffusion (FD). In the end, the electrons in PPD are sampled by the method of the conventional skipper pixels. According to TCAD simulation results, the extra electrons are transferred to LOGCC through the TG effectively. Measurement of prototype chip shows that the DR is extended to 89.3 dB. As contrast, the DR is 66 dB when switching off the transfer gates, i.e. LOGCC. Compared with traditional SIS, the proposed architecture achieved DR extension by introducing LOGCC which is constructed with transfer gates. Therefore, this study proposes the introduction of LOGCC to expand the application scenarios of SIS, providing a new approach for its use in conditions requiring stronger light.

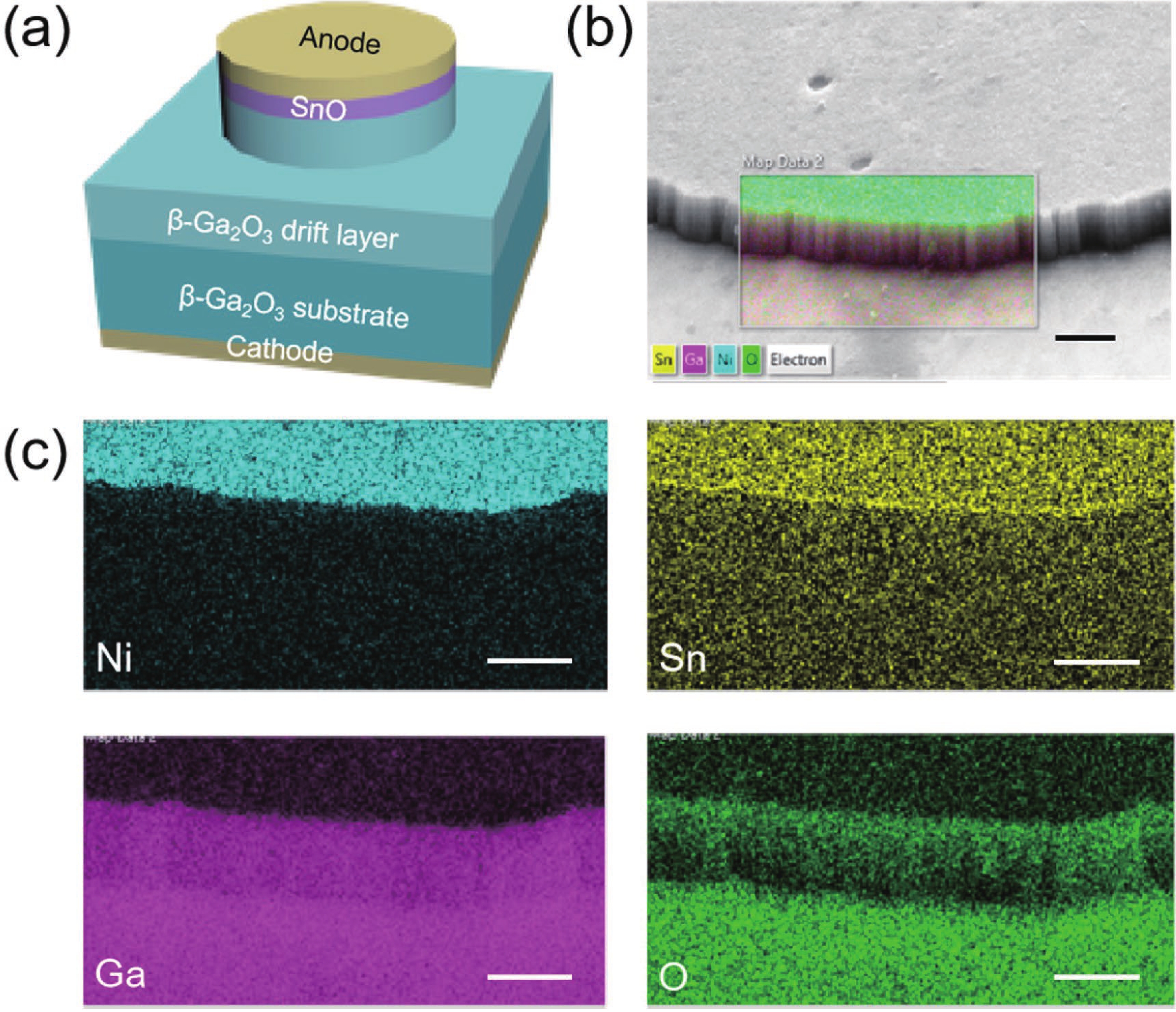

In this article, a vertical SnO/β-Ga2O3 mesa heterojunction diode (mesa-HJD) fabricated through self-aligned etching is reported. The mesa structure eliminates the influence of lateral depletion at the region, leading to an improved breakdown characteristics in comparison with its unterminated heterojunction diode (UT-HJD) counterpart. The SnO/β-Ga2O3 mesa-HJD, featuring a 500 nm mesa depth, achieves a breakdown voltage (BV) of 1100 V, which can be improved to 1631 V by sidewall passivation. With the increase of mesa depth, BV increases, accompanied by the increase of specific on-resistance (Ron,sp). Therefore, a maximum Baliga’s power figure of merit (PFOM) can be achieved for the optimized device with 500 nm mesa depth, giving the value of 0.93 GW/cm2 for the passivated device. The mesa-HJD demonstrates considerable potential for application in high BV β-Ga2O3 power electronic devices in the future.

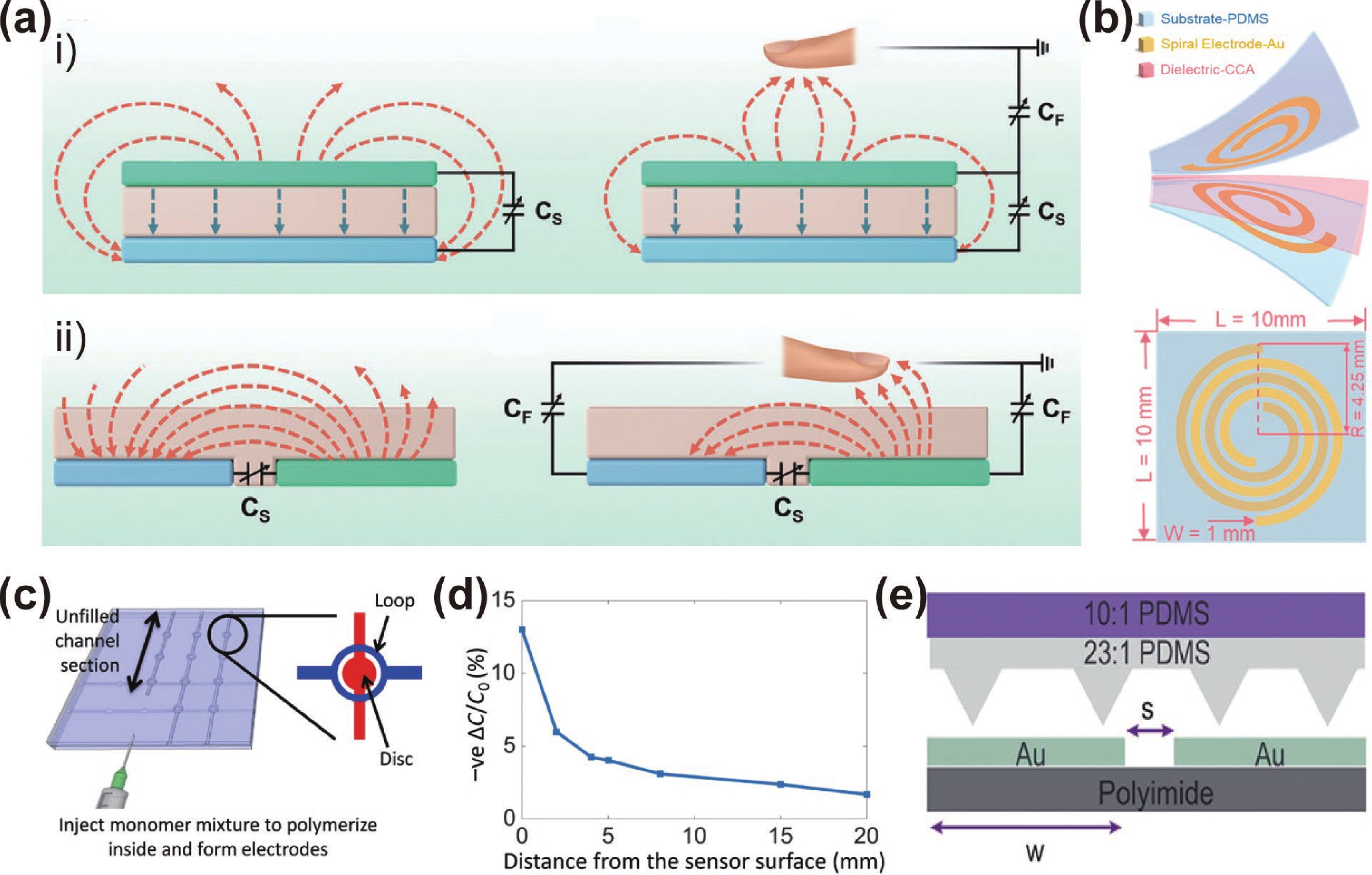

The integration of proximity sensing into flexible tactile electronic skins (e-skins) represents a fundamental shift from conventional contact-only interfaces toward anticipatory perception systems. This mini-review provides a systematic examination of recent advances in proximity-augmented e-skins, which overcome the inherent latency of tactile sensors by extending sensory awareness into the pre-contact domain. We provide a comprehensive overview of five key sensing modalities—capacitive, triboelectric, magnetic, temperature-based, and humidity-based—detailing their operating principles, material innovations, and structural optimization strategies. System-level requirements for practical deployment are also critically analyzed. Representative applications in interactive surfaces, human–robot collaboration, soft robotics, healthcare monitoring, and integrated multifunctional e-skins are highlighted to illustrate the transformative potential of this technology. Despite substantial progress, challenges persist in seamless multimodal integration, scalable manufacturing, and intelligent data fusion. Future directions are discussed to realize robust, perceptually intelligent e-skins that bridge the gap between laboratory innovations and real-world applications.

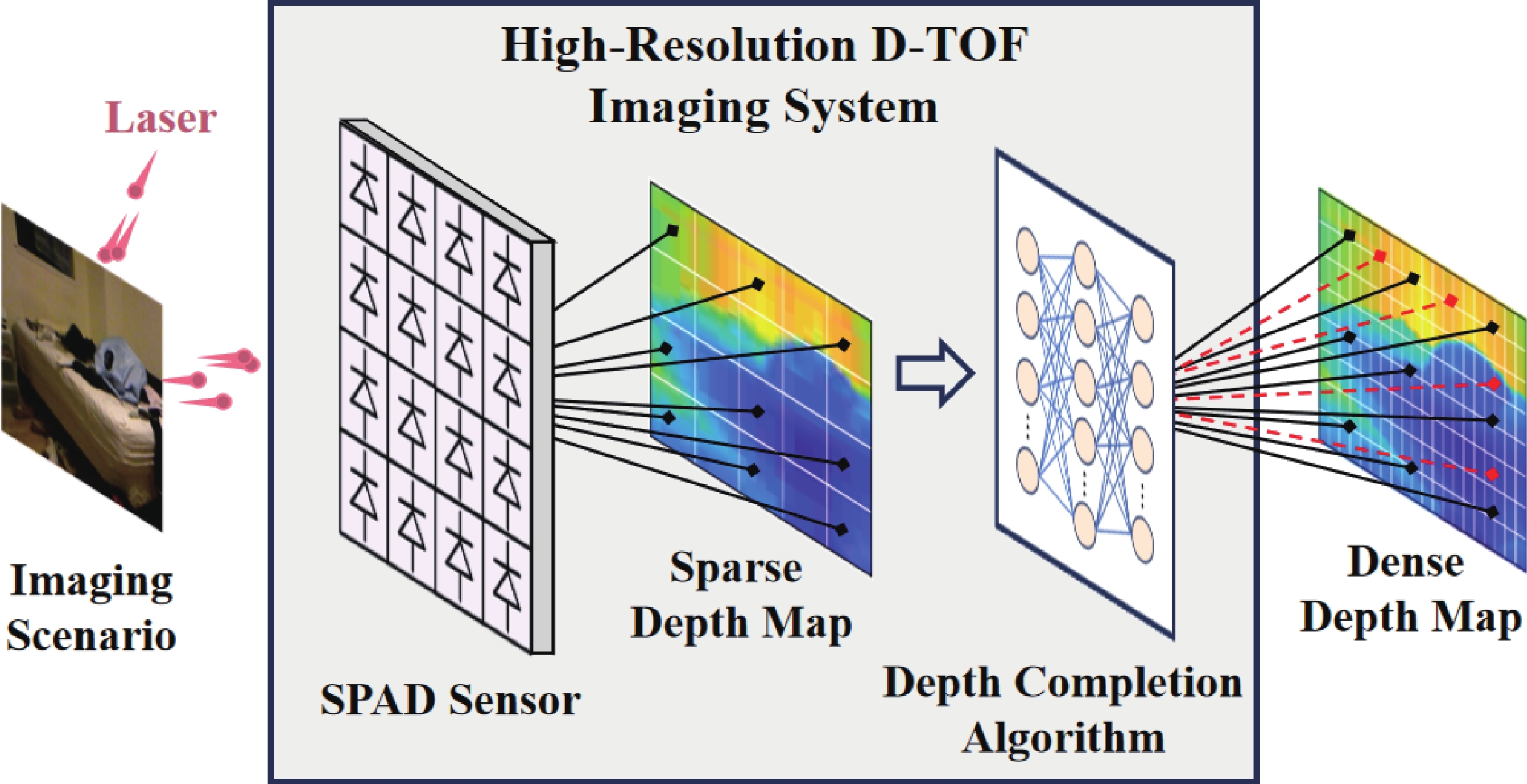

Single-photon avalanche diode (SPAD) image sensors are widely used in direct time-of-flight (D-TOF) imaging, but their ranging performance is often constrained by limited laser power. This article presents a SPAD-based D-TOF imaging system that combines a reconfigurable macro-pixel sensor architecture with a lightweight depth completion algorithm to achieve long-range depth imaging with enhanced spatial resolution under low optical power. The proposed sensor adopts a back-side illuminated (BSI) 3D-stacked architecture with programmable macro-pixels that enhance detection sensitivity and enable flexible sensitivity–resolution trade-offs. An injection-locked ring-oscillator-based time-to-digital converter (RO-TDC) array achieves a time resolution of 152.5 ps, enabling accurate TOF measurement at an optical power of 10 mW. To compensate for macro-pixel-induced resolution loss, a probabilistic normalized convolutional neural network (pNCNN) is employed for depth completion using sparse depth inputs only. Experimental results demonstrate that up to 30 × effective resolution enhancement of the system can be achieved via the depth completion algorithm without changing the physical resolution of the sensor. Additionally, the proposed system achieves a maximum ranging distance of 90 m and a range-to-power figure-of-merit (FOM) of 9 m/mW, which validates the effectiveness of the system.

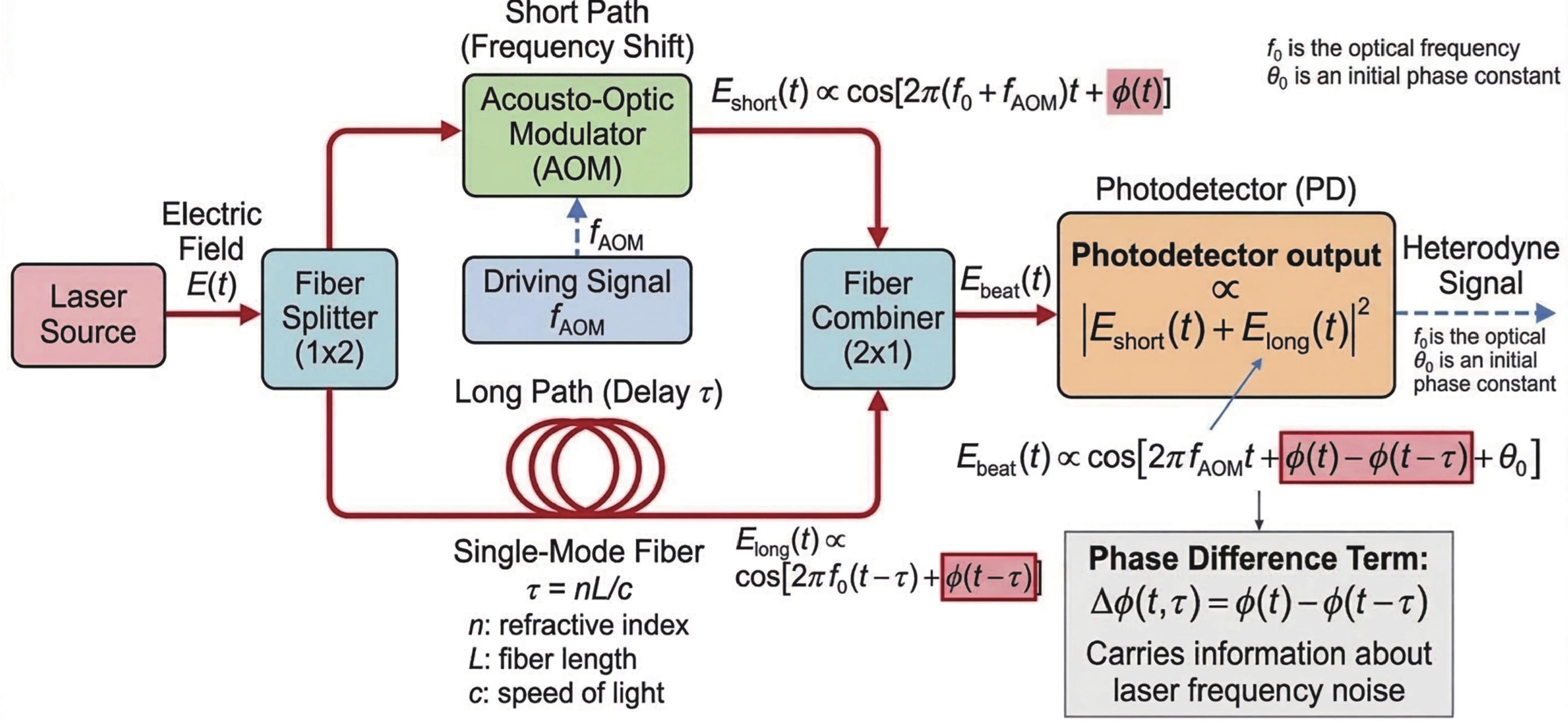

Systematic optimization of the delayed self-heterodyne method for laser frequency noise characterization is investigated across an extensive linewidth range (100 Hz to 10 MHz). By evaluating various fiber lengths, window functions, and five demodulation algorithms, we identify a critical trade-off: long fibers enhance sensitivity for narrow-linewidth lasers but exacerbate spectral leakage in broad-linewidth sources. Our findings demonstrate that Hanning and Blackman windows effectively suppress this leakage, ensuring measurement consistency across different delay lengths. Among the evaluated algorithms, the Hilbert transform offers the superior balance of high-frequency accuracy and computational efficiency. Validated under low-power conditions, this optimized framework provides a robust and power-independent methodology for precise FN analysis, offering significant guidance for high-performance laser development.