Just Accepted manuscripts are peer-reviewed and accepted for publication. They are posted online prior to technical editing formatting for publication and author proofing.

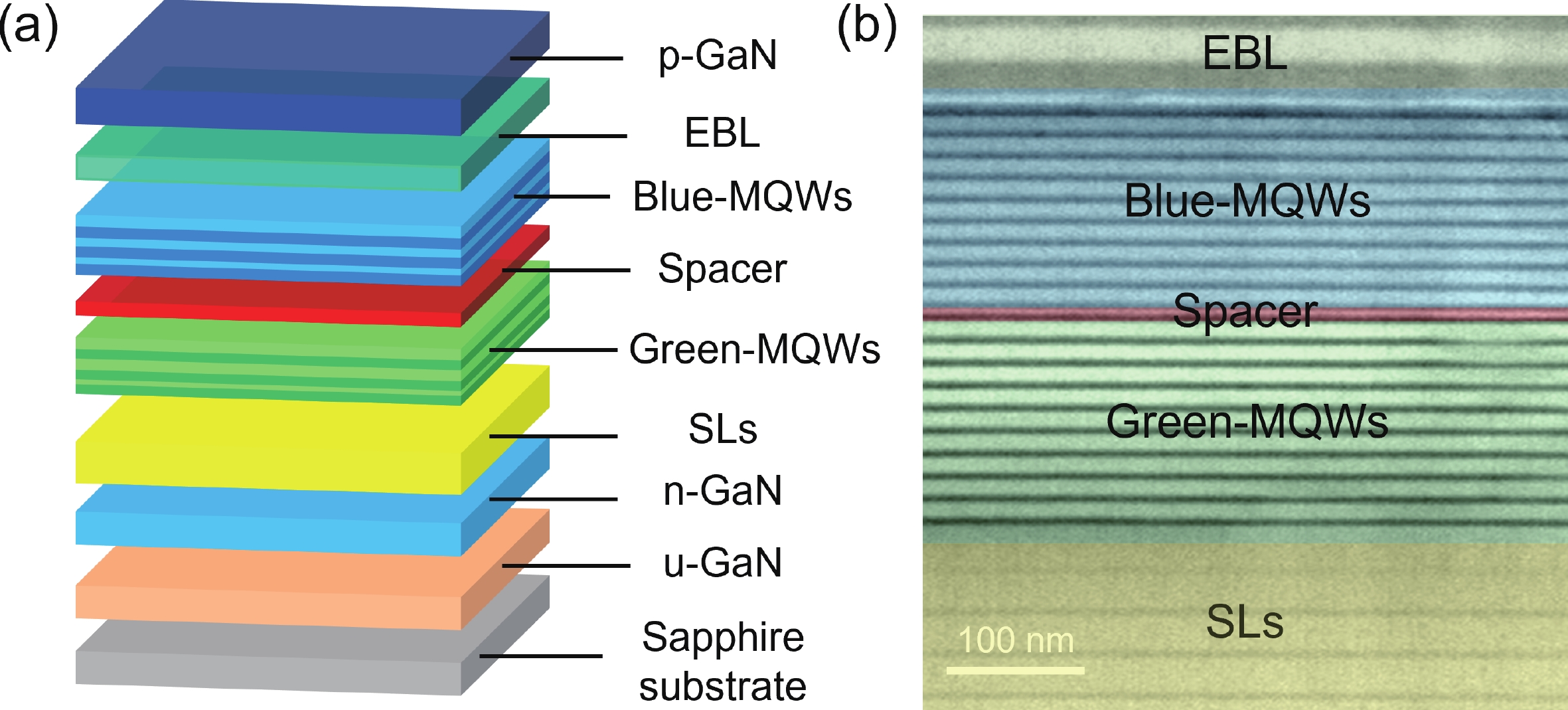

III-nitride semiconductors with continuously tunable bandgaps are promising for white light emission and full-color displays. The mainstream RGB LED integration approach suffers from low long-wavelength efficiency and complex packaging. Herein, we demonstrate a novel single-chip dual-wavelength LED structure, which integrates blue (upper) and green (bottom) multiple quantum wells (MQWs) separated by a GaN intermediate spacer layer. The device exhibits two distinct emission peaks at 446 and 528 nm, with excellent luminescence stability. We investigate the role of the spacer layer and reveal its critical effect on the carrier distribution and radiative recombination behavior. The maximum wall-plug efficiency (WPE) of the device reaches approximately 36.7%, and its abnormal droop curve indicates a transition of the green emission mechanism from electroluminescence (EL) to photoluminescence (PL). By tuning the injection current, the dual-wavelength LED achieves a continuous color transition from green to blue, which corresponds to chromaticity coordinates ranging from (0.2584, 0.7098) to (0.1771, 0.2649) in the CIE 1931 chromaticity diagram. This work provides a feasible and flexible strategy for emission color modulation, and also lays a foundation for the development of high-performance solid-state lighting devices.

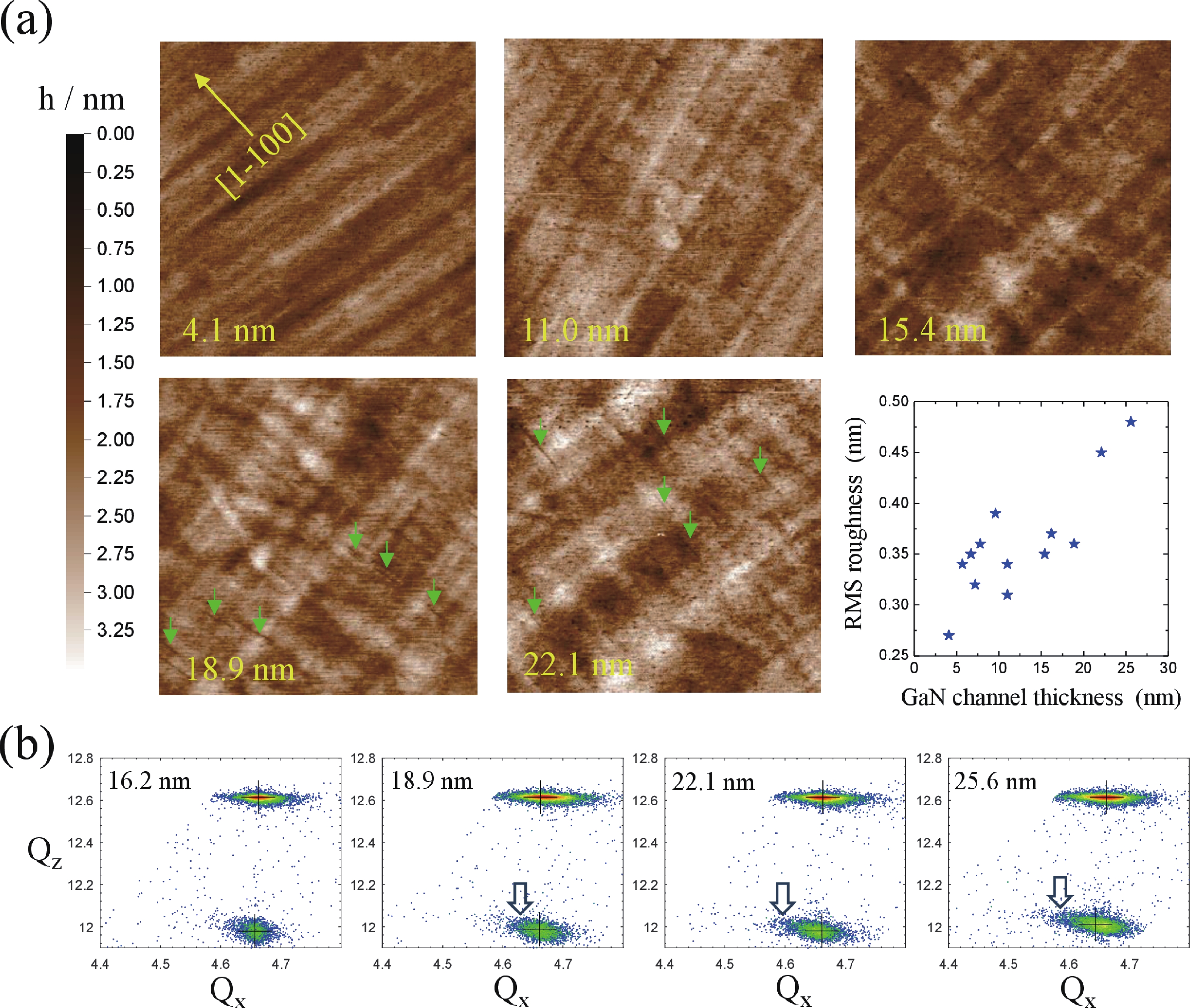

We have systematically studied the impact of thickness on the electrical properties of thin GaN channels on N-polar AlN (0001) templates grown on sapphire. The observed increase in sheet carrier density with increasing GaN thickness can be quantitatively reproduced by calculations assuming a Fermi-level pinning about 0.8 eV below the conduction band. The mobility strongly increases until 6 nm which correlates with reduced overlap of the 2DEG wave function with the surface layer. The mobility then increases more gradually up to 10 nm, corresponding to a reduced fraction of the 2DEG within the first 0.5 nm near the AlN/GaN interface, namely, the region affected by interface roughness. The mobility saturates at approximately 400 cm2·V−1·s−1, probably limited by dislocations and the overlap with deep traps inside the AlN back barrier. If the GaN thickness exceeds 15 nm, the mobility decreases, likely due to the onset of gradual relaxation and appearance of misfit dislocations. Finally, we note that the temperature-dependent mobility exhibits an unexpected contribution proportional to $ T^{-2} $ for all GaN channels on N-polar AlN, including those reported in the literature. Such observation may be explained by a 50% higher effective mass of the electron, which amplify the electron-phonon scattering, ultimately limiting the room-temperature mobility to about 750 cm2·V−1·s−1 and confining the sheet resistivity to values above 200 Ω/□.

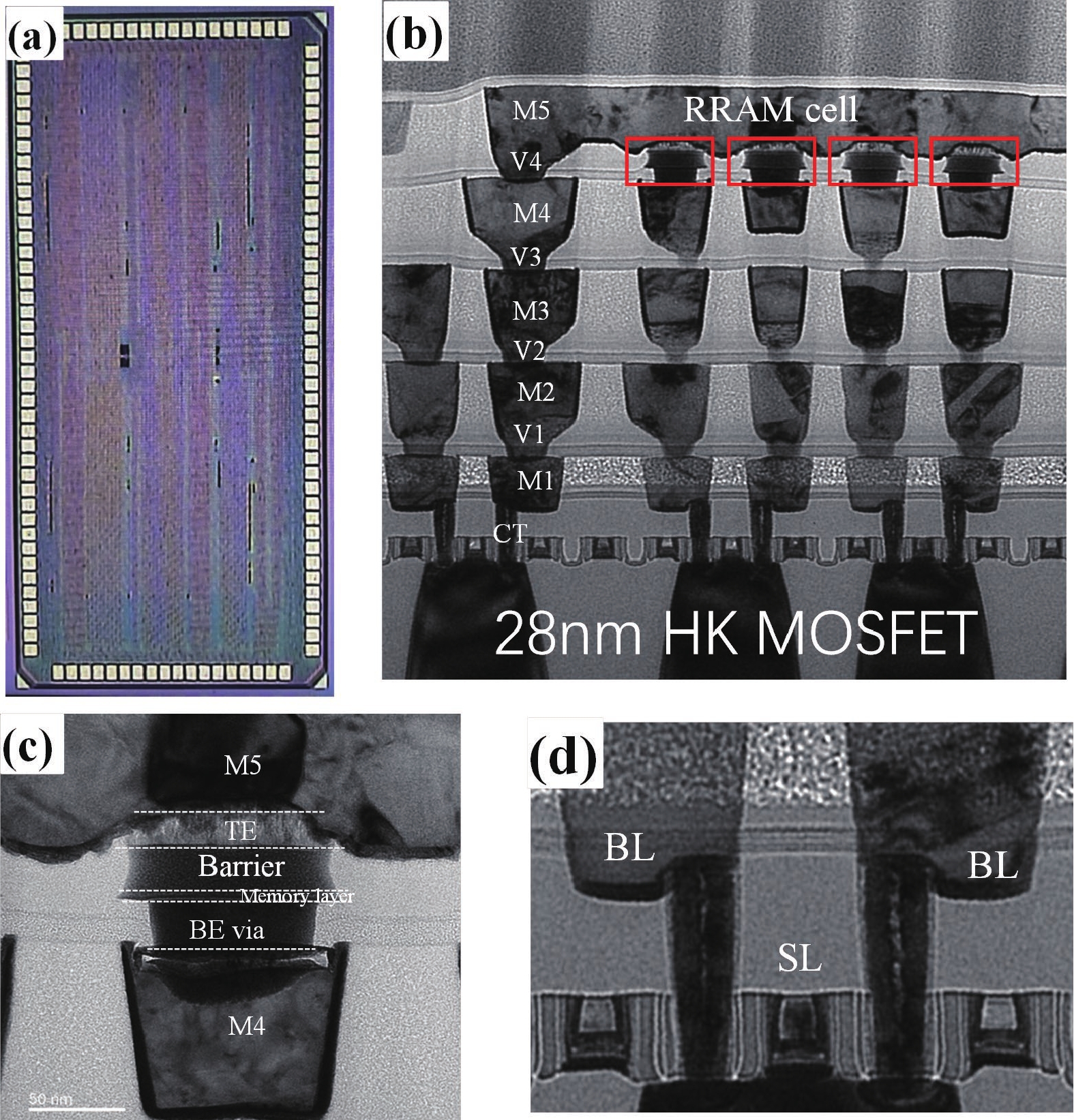

With the widespread application of artificial intelligence (AI) computing in low-temperature scenarios such as deep space and deep sea, RRAM−based edge computing has gradually attracted attention. In this paper, an adaptive reference conductance algorithm (ARCA) is proposed to improve the inference accuracy in low−temperature scenarios due to the conduction drift. The RRAM CIM chips with high read cycles are fabricated based on 28 nm CMOS logic technology, and the read times could reach 1012. By studying the influence of conductance drifting on inference accuracy in low temperature, a model of temperature and optimal reference conductance is proposed. Furthermore, by this model, adaptive selecting optimal reference conductance of Analog−to−digital converters (ADCs) to quantize column current of RRAM array under different temperatures. At −40℃, the reference accuracy could increase from 75.43% to 86.8%.

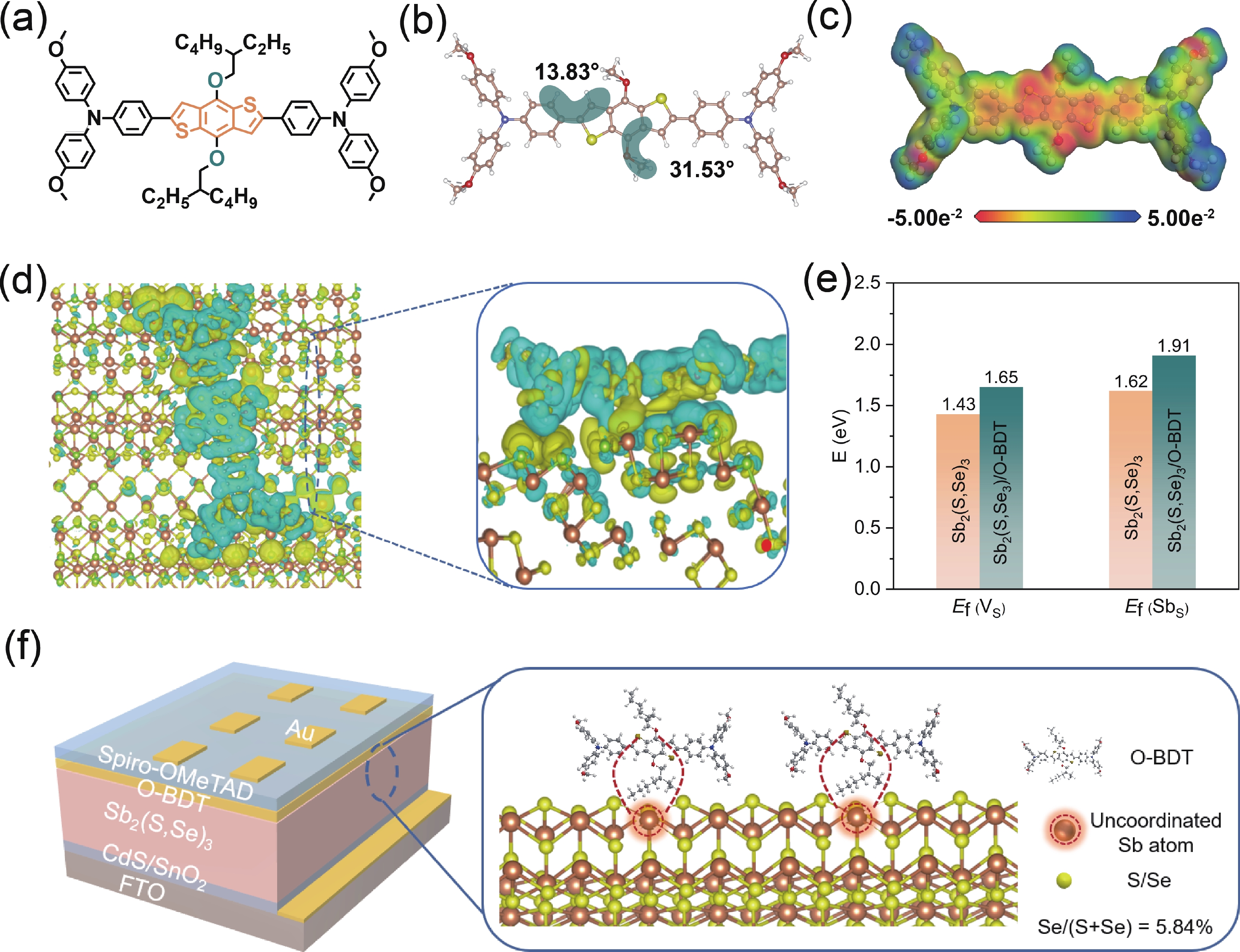

Antimony selenosulfide (Sb2(S,Se)3) is a promising photovoltaic absorber material for both outdoor and indoor application scenarios. Nevertheless, the performance of Sb2(S,Se)3 solar cells remains constrained by the severe interface trap-induced nonradiative recombination. Interface engineering has been recognized as an effective approach to suppress recombination and boost charge transport. In this work, we introduce an organic modifier (O-BDT) between Sb2(S,Se)3 absorber and hole transport layer. The theoretical and experimental results evidence that O-BDT can simultaneously passivates interface defects and optimizes the energy-level alignment, leading to a significantly reduced voltage loss. Finally, the O-BDT modified solar cell achieves a power conversion efficiency (PCE) of 8.01% under AM 1.5G illumination. Moreover, the device delivers a PCE of 19.04% under 1000 lux, 3312 K LED lighting, among the best list of IPVs based on antimony chalcogenide compounds.

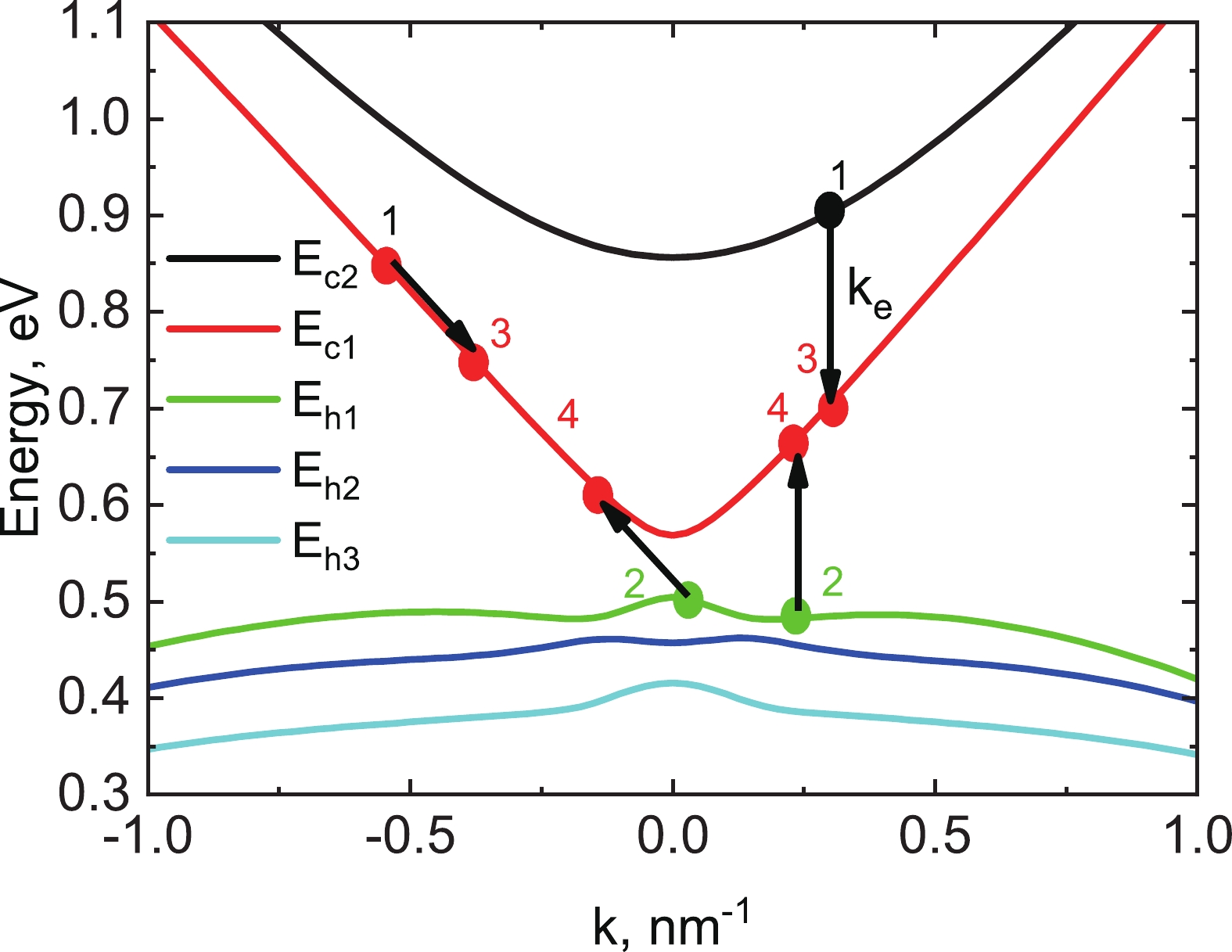

Impact ionization probabilities were calculated in a CdHgTe quantum well, where the distance between electron subbands is close to the band gap energy. This band structure enables impact ionization with small momentum transfer for electrons in the second subband. The study demonstrates that such processes increase the impact ionization probability by approximately two orders of magnitude compared to the impact ionization probability for electrons in the first subband, for which transitions with small momentum changes are impossible. The probability of single impact ionization during the electron energy loss due to optical phonon emission is estimated. Experimental methods for detecting impact ionization in this structure are discussed.