J. Semicond.

Volume 46, Issue 7, Jul 2025

Call for Papers

Special Issue on Optoelectronic Neuromorphic Devices

Guest Editors: Zhenyi Ni, Zhongqiang Wang, Jia Huang, Xiaodong Pi

Call for Papers

Special Issue on Flexible and Smart Electronics for Sensors 4.0

Guest Editors: Zhuoran Wang, Yang Li, Qilin Hua

Call for Papers

Phase Change Materials for Reconfigurable Photonics and Electronics

Guest Edited: Hongtao Lin, Tian Gu

Call for Papers

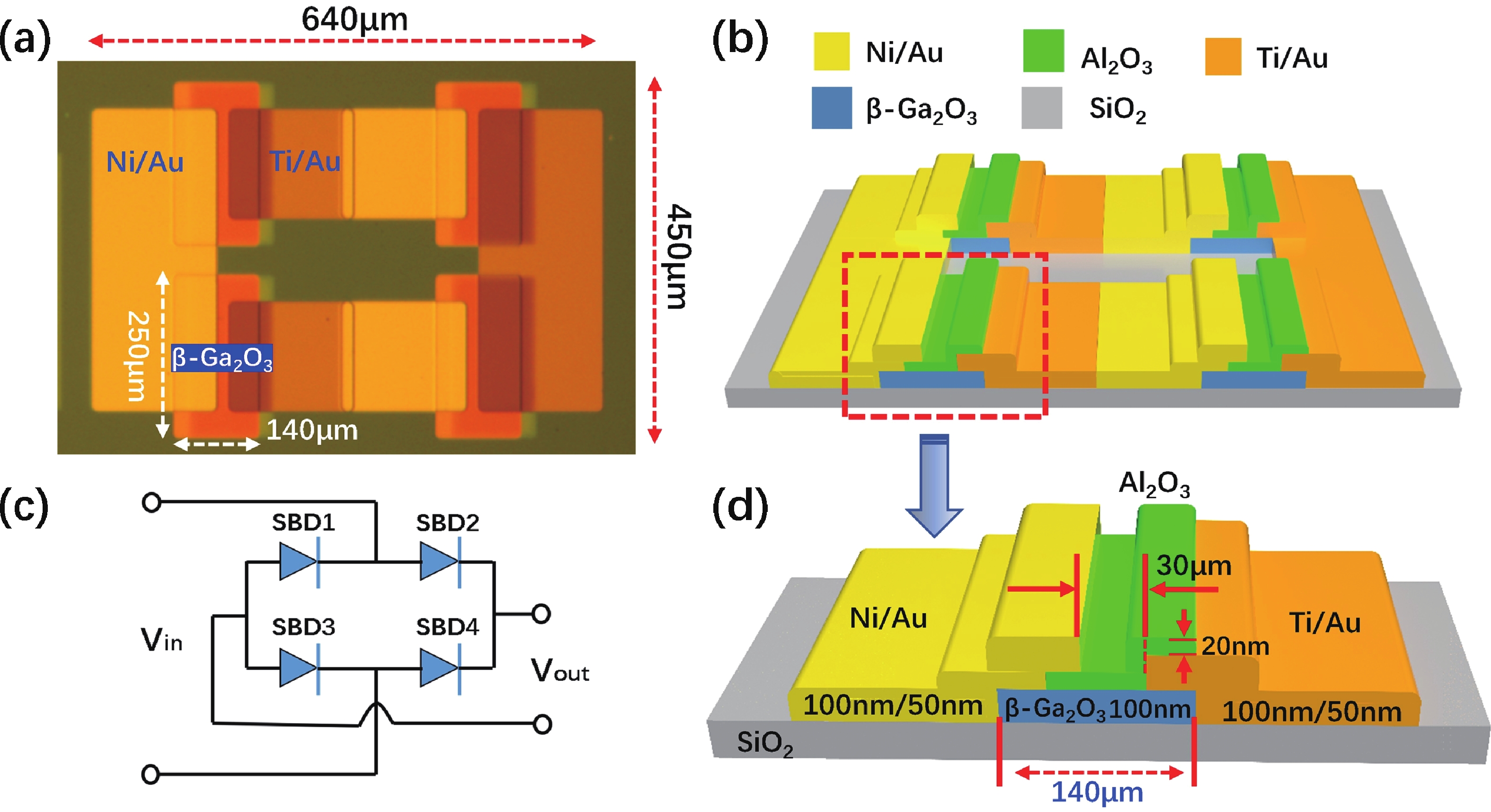

Towards High Performance Ga2O3 Electronics: Epitaxial Growth and Power Devices

Guest Editors: Genquan Han, Shibing Long, Yuhao Zhang, Yibo Wang

Call for Papers

Novel Semiconductor-Biochemical Sensors

Guest Editors: Zhao Li, Xiangmei Lin, Dongxian He, Yingxin Ma, Yuanjing Lin

Special Issue

Flexible Energy Devices

Guest Edited: Zhiyong Fan, Yonghua Chen, Yuanjing Lin, Yunlong Zi, Hyunhyub Ko, Qianpeng Zhang

Special Issue

Semiconductor Optoelectronic Integrated Circuits

Guest Edited: Wei Wang, Lingjuan Zhao, Dan Lu, Jianping Yao, Weiping Huang, Yong Liu, Brent Little

Special Issue

Beyond Moore: Three-Dimensional (3D) Heterogeneous Integration

Guest Edited: Yue Hao, Huaqiang Wu, Yuchao Yang, Qi Liu, Xiao Gong, Genquan Han, Ming Li

Special Issue

Beyond Moore: Resistive Switching Devices for Emerging Memory and Neuromorphic Computing

Guest Edited: Yue Hao, Huaqiang Wu, Yuchao Yang, Qi Liu, Xiao Gong, Genquan Han, Ming Li

Special Issue

Celebration of the 60th Anniversary of Dedicating to Scientific Research of Prof. Zhanguo Wang

Guest Editors: Zhijie Wang, Chao Zhao , Fei Ding

Special Issue

Reconfigurable Computing for Energy Efficient AI Microchip Technologies

Guest Editors: Haigang Yang, Yajun Ha, Lingli Wang, Wei Zhang, Yingyan Lin

Special Issue

Semiconductor Materials Genome Initiative: New Concepts and Discoveries

Guest Editors: Suhuai Wei, Junwei Luo, Bing Huang

Special Issues

2D-materials-related physical properties and optoelectronic devices

Guest Editors: Ping-Heng Tan, Lijun Zhang, Lun Dai, Shuyun Zhou

Special Issue

Flexible and Wearable Sensors for Robotics and Health

Guest Editors: Zhiyong Fan, Johnny C. Ho, Chuan Wang, Yun-Ze Long, Huan Liu

Special Issue

Si-Based Materials and Devices

Guest Editors: Chuanbo Li, Linwei Yu, Jinsong Xia

Special Issue

Devices and Circuits for Wearable and IoT Systems

Guest Editors: Zhihua Wang, Yong Hei, Zhangming Zhu

Special Issue

Flexible and Wearable Electronics: from Materials to Applications

Guest Editors: Guozhen Shen, Yongfeng Mei, Chuan Wang, Taeyoon Lee

News

First time: Science Cites Journal of Semiconductors

News

JOS has been indexed in ESCI database since 2016

Abstract

Abstract

Full Text

Full Text

PDF

Currently, the global 5G network, cloud computing, and data center industries are experiencing rapid development. The continuous growth of data center traffic has driven the vigorous progress in high-speed optical transceivers for optical interconnection within data centers. The electro-absorption modulated laser (EML), which is widely used in optical fiber communications, data centers, and high-speed data transmission systems, represents a high-performance photoelectric conversion device. Compared to traditional directly modulated lasers (DMLs), EMLs demonstrate lower frequency chirp and higher modulation bandwidth, enabling support for higher data rates and longer transmission distances. This article introduces the composition, working principles, manufacturing processes, and applications of EMLs. It reviews the progress on advanced indium phosphide (InP)-based EML devices from research institutions worldwide, while summarizing and comparing data transmission rates and key technical approaches across various studies.

PDF

Currently, the global 5G network, cloud computing, and data center industries are experiencing rapid development. The continuous growth of data center traffic has driven the vigorous progress in high-speed optical transceivers for optical interconnection within data centers. The electro-absorption modulated laser (EML), which is widely used in optical fiber communications, data centers, and high-speed data transmission systems, represents a high-performance photoelectric conversion device. Compared to traditional directly modulated lasers (DMLs), EMLs demonstrate lower frequency chirp and higher modulation bandwidth, enabling support for higher data rates and longer transmission distances. This article introduces the composition, working principles, manufacturing processes, and applications of EMLs. It reviews the progress on advanced indium phosphide (InP)-based EML devices from research institutions worldwide, while summarizing and comparing data transmission rates and key technical approaches across various studies.

Abstract

Abstract

Full Text

Full Text

PDF

Robotic computing systems play an important role in enabling intelligent robotic tasks through intelligent algorithms and supporting hardware. In recent years, the evolution of robotic algorithms indicates a roadmap from traditional robotics to hierarchical and end-to-end models. This algorithmic advancement poses a critical challenge in achieving balanced system-wide performance. Therefore, algorithm-hardware co-design has emerged as the primary methodology, which analyzes algorithm behaviors on hardware to identify common computational properties. These properties can motivate algorithm optimization to reduce computational complexity and hardware innovation from architecture to circuit for high performance and high energy efficiency. We then reviewed recent works on robotic and embodied AI algorithms and computing hardware to demonstrate this algorithm-hardware co-design methodology. In the end, we discuss future research opportunities by answering two questions: (1) how to adapt the computing platforms to the rapid evolution of embodied AI algorithms, and (2) how to transform the potential of emerging hardware innovations into end-to-end inference improvements.

PDF

Robotic computing systems play an important role in enabling intelligent robotic tasks through intelligent algorithms and supporting hardware. In recent years, the evolution of robotic algorithms indicates a roadmap from traditional robotics to hierarchical and end-to-end models. This algorithmic advancement poses a critical challenge in achieving balanced system-wide performance. Therefore, algorithm-hardware co-design has emerged as the primary methodology, which analyzes algorithm behaviors on hardware to identify common computational properties. These properties can motivate algorithm optimization to reduce computational complexity and hardware innovation from architecture to circuit for high performance and high energy efficiency. We then reviewed recent works on robotic and embodied AI algorithms and computing hardware to demonstrate this algorithm-hardware co-design methodology. In the end, we discuss future research opportunities by answering two questions: (1) how to adapt the computing platforms to the rapid evolution of embodied AI algorithms, and (2) how to transform the potential of emerging hardware innovations into end-to-end inference improvements.

Abstract

Abstract

Full Text

Full Text

PDF

The unique structure and exceptional properties of two-dimensional (2D) materials offer significant potential for transformative advancements in semiconductor industry. Similar to the reliance on wafer-scale single-crystal ingots for silicon-based chips, practical applications of 2D materials at the chip level needs large-scale, high-quality production of 2D single crystals. Over the past two decades, the size of 2D single-crystals has been improved to wafer or meter scale, where the nucleation control during the growth process is particularly important. Therefore, it is essential to conduct a comprehensive review of nucleation control in 2D materials to gain fundamental insights into the growth of 2D single-crystal materials. This review mainly focuses on two aspects: controlling nucleation density to enable the growth from a single nucleus, and controlling nucleation position to achieve the unidirectionally aligned islands and subsequent seamless stitching. Finally, we provide an overview and forecast of the strategic pathways for emerging 2D materials.

PDF

The unique structure and exceptional properties of two-dimensional (2D) materials offer significant potential for transformative advancements in semiconductor industry. Similar to the reliance on wafer-scale single-crystal ingots for silicon-based chips, practical applications of 2D materials at the chip level needs large-scale, high-quality production of 2D single crystals. Over the past two decades, the size of 2D single-crystals has been improved to wafer or meter scale, where the nucleation control during the growth process is particularly important. Therefore, it is essential to conduct a comprehensive review of nucleation control in 2D materials to gain fundamental insights into the growth of 2D single-crystal materials. This review mainly focuses on two aspects: controlling nucleation density to enable the growth from a single nucleus, and controlling nucleation position to achieve the unidirectionally aligned islands and subsequent seamless stitching. Finally, we provide an overview and forecast of the strategic pathways for emerging 2D materials.

Abstract

Abstract

Full Text

Full Text

PDF

Infrared and terahertz waves constitute pivotal bands within the electromagnetic spectrum, distinguished by their robust penetration capabilities and non-ionizing nature. These wavebands offer the potential for achieving high-resolution and non-destructive detection methodologies, thereby possessing considerable research significance across diverse domains including communication technologies, biomedical applications, and security screening systems. Two-dimensional materials, owing to their distinctive optoelectronic attributes, have found widespread application in photodetection endeavors. Nonetheless, their efficacy diminishes when tasked with detecting lower photon energies. Furthermore, as the landscape of device integration evolves, two-dimensional materials struggle to align with the stringent demands for device superior performance. Topological materials, with their topologically protected electronic states and non-trivial topological invariants, exhibit quantum anomalous Hall effects and ultra-high carrier mobility, providing a new approach for seeking photosensitive materials for infrared and terahertz photodetectors. This article introduces various types of topological materials and their properties, followed by an explanation of the detection mechanism and performance parameters of photodetectors. Finally, it summarizes the current research status of near-infrared to far-infrared photodetectors and terahertz photodetectors based on topological materials, discussing the challenges faced and future prospects in their development.

PDF

Infrared and terahertz waves constitute pivotal bands within the electromagnetic spectrum, distinguished by their robust penetration capabilities and non-ionizing nature. These wavebands offer the potential for achieving high-resolution and non-destructive detection methodologies, thereby possessing considerable research significance across diverse domains including communication technologies, biomedical applications, and security screening systems. Two-dimensional materials, owing to their distinctive optoelectronic attributes, have found widespread application in photodetection endeavors. Nonetheless, their efficacy diminishes when tasked with detecting lower photon energies. Furthermore, as the landscape of device integration evolves, two-dimensional materials struggle to align with the stringent demands for device superior performance. Topological materials, with their topologically protected electronic states and non-trivial topological invariants, exhibit quantum anomalous Hall effects and ultra-high carrier mobility, providing a new approach for seeking photosensitive materials for infrared and terahertz photodetectors. This article introduces various types of topological materials and their properties, followed by an explanation of the detection mechanism and performance parameters of photodetectors. Finally, it summarizes the current research status of near-infrared to far-infrared photodetectors and terahertz photodetectors based on topological materials, discussing the challenges faced and future prospects in their development.

WeChat ID

WeChat ID

Mobile Terminal

Mobile Terminal

Journal of Semiconductors © 2017 All Rights Reserved 京ICP备05085259号-2