Chemical mechanical polishing (CMP) serves as an indispensable process for achieving global planarization in semiconductor manufacturing, especially as integrated circuit (IC) technology advances to sub-7 nm nodes, where atomic-level surface flatness becomes crucial. Silica abrasives, which account for over 90% of the abrasive market in advanced CMP processes, operate not through simple mechanical grinding but through a key "chemical-mechanical synergistic" mechanism: chemically softening the wafer surface, then mechanically removing the softened layer to expose a new surface, which is further softened and removed, repeating this cycle to produce a smooth wafer. Despite their prevalence, conventional silica abrasives still face challenges, including relatively low material removal rate (MRR), a tendency to agglomerate, leading to poor dispersion and surface defects, and limitations in achieving ultimate surface uniformity. Significant progress has been made to address these issues. Development has progressed from simple spherical particles to complex structural designs (such as mesoporous, hollow, and raspberry-shaped structures) to enhance slurry transport and mechanical action. Surface chemical modifications (e.g., using amino or polymer groups) can improve dispersion stability and reduce scratching. Furthermore, composites with other materials (e.g., ceria, polymers) and precise control of particle size distribution are key to enhancing performance. These innovative approaches have yielded significant performance gains. State-of-the-art slurries have demonstrated the ability to achieve surface roughness below 0.1 nm RMS. The development of silica abrasives is increasingly focused on sustainability and smart manufacturing. A prominent direction is the design of biodegradable abrasives that disintegrate after use, thereby simplifying post-chemical mechanical polishing (CMP) cleanup and minimizing environmental impact—an approach fully aligned with green manufacturing principles. This review systematically summarizes the progress of silica abrasives for CMP over the past 60 years. This summary provides theoretical insights and forward-looking strategies to overcome the current limitations of abrasive technology. We believe this review will be helpful in advancing the field of CMP abrasives towards next-generation semiconductor manufacturing.

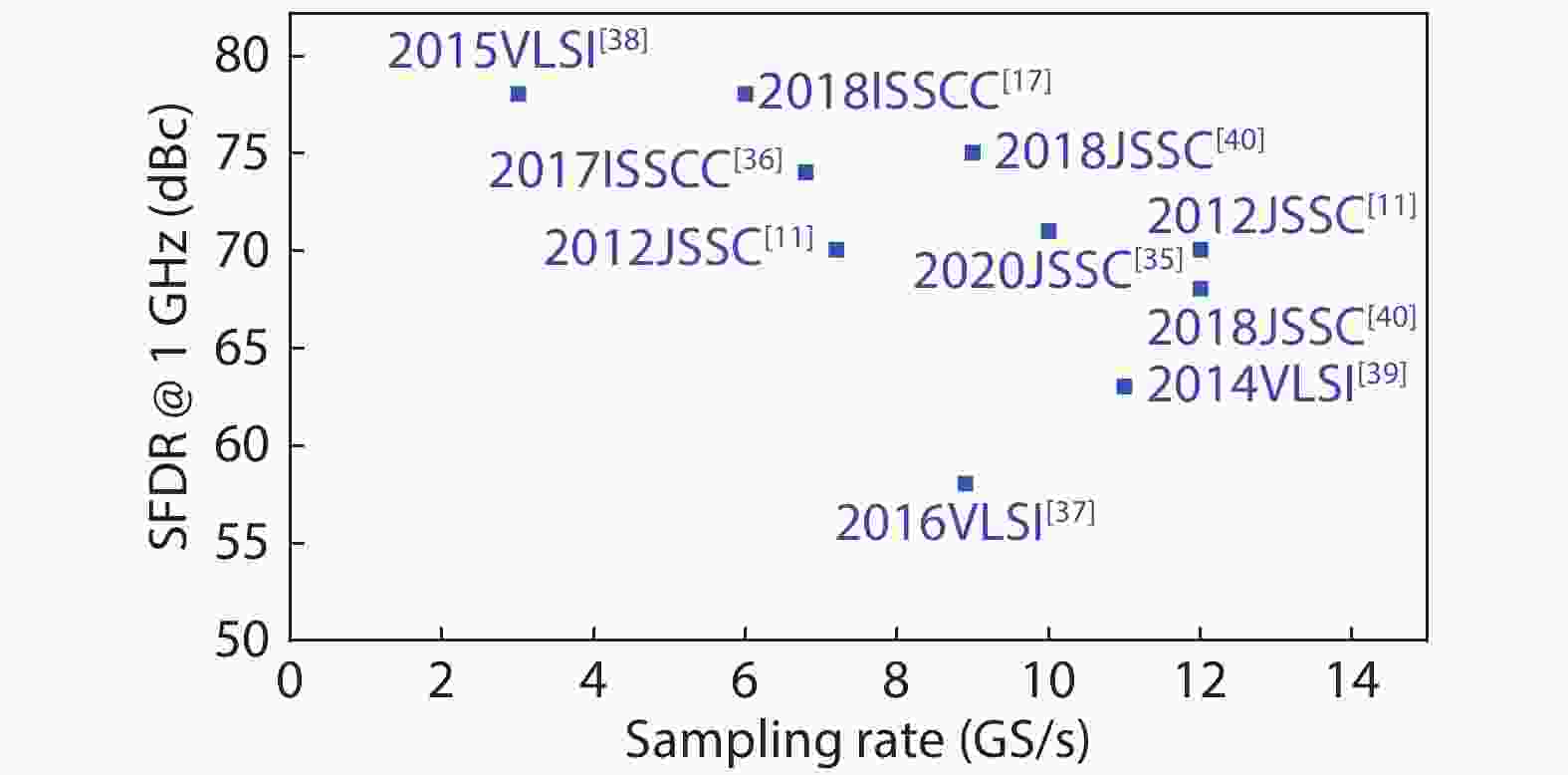

Digital to analog converters (DAC) play an important role as a bridge connecting the analog world and the digital world. With the rapid development of wireless communication, wideband digital radar, and other emerging technologies, better performing high-speed high-resolution DACs are required. In those applications, signal bandwidth and high-frequency linearity often limited by data converters are the bottleneck of the system. This article reviews the state-of-the-art technologies of high-speed and high-resolution DACs reported in recent years. Comparisons are made between different architectures, circuit implementations and calibration techniques along with the figure of merit (FoM) results.

Al-rich AlxGa1−xN (x ≥ 0.8) is promising for power and deep-ultraviolet (DUV) optoelectronic applications, owing to its ultra-wide bandgap and excellent thermal stability. However, forming low-resistivity contacts on n-type Al-rich AlGaN remains a significant challenge. In this work, we utilized an Au-free Ti/Al/Ti metal stack contact on n-type Al-rich AlGaN without graded layers. Record-low contact resistivities were achieved after annealing: 1.52 × 10−6 Ω·cm2 for n-Al0.8Ga0.2N, 3.56 × 10−6 Ω·cm2 for n-Al0.86Ga0.14N, and 5.79 × 10−5 Ω·cm2 for n-Al0.9Ga0.1N. These results demonstrate a significant advancement in forming low-resistance contacts directly on Al-rich n-AlGaN, offering a viable path forward for next-generation power electronics and DUV optoelectronic devices.

Currently, the global 5G network, cloud computing, and data center industries are experiencing rapid development. The continuous growth of data center traffic has driven the vigorous progress in high-speed optical transceivers for optical interconnection within data centers. The electro-absorption modulated laser (EML), which is widely used in optical fiber communications, data centers, and high-speed data transmission systems, represents a high-performance photoelectric conversion device. Compared to traditional directly modulated lasers (DMLs), EMLs demonstrate lower frequency chirp and higher modulation bandwidth, enabling support for higher data rates and longer transmission distances. This article introduces the composition, working principles, manufacturing processes, and applications of EMLs. It reviews the progress on advanced indium phosphide (InP)-based EML devices from research institutions worldwide, while summarizing and comparing data transmission rates and key technical approaches across various studies.

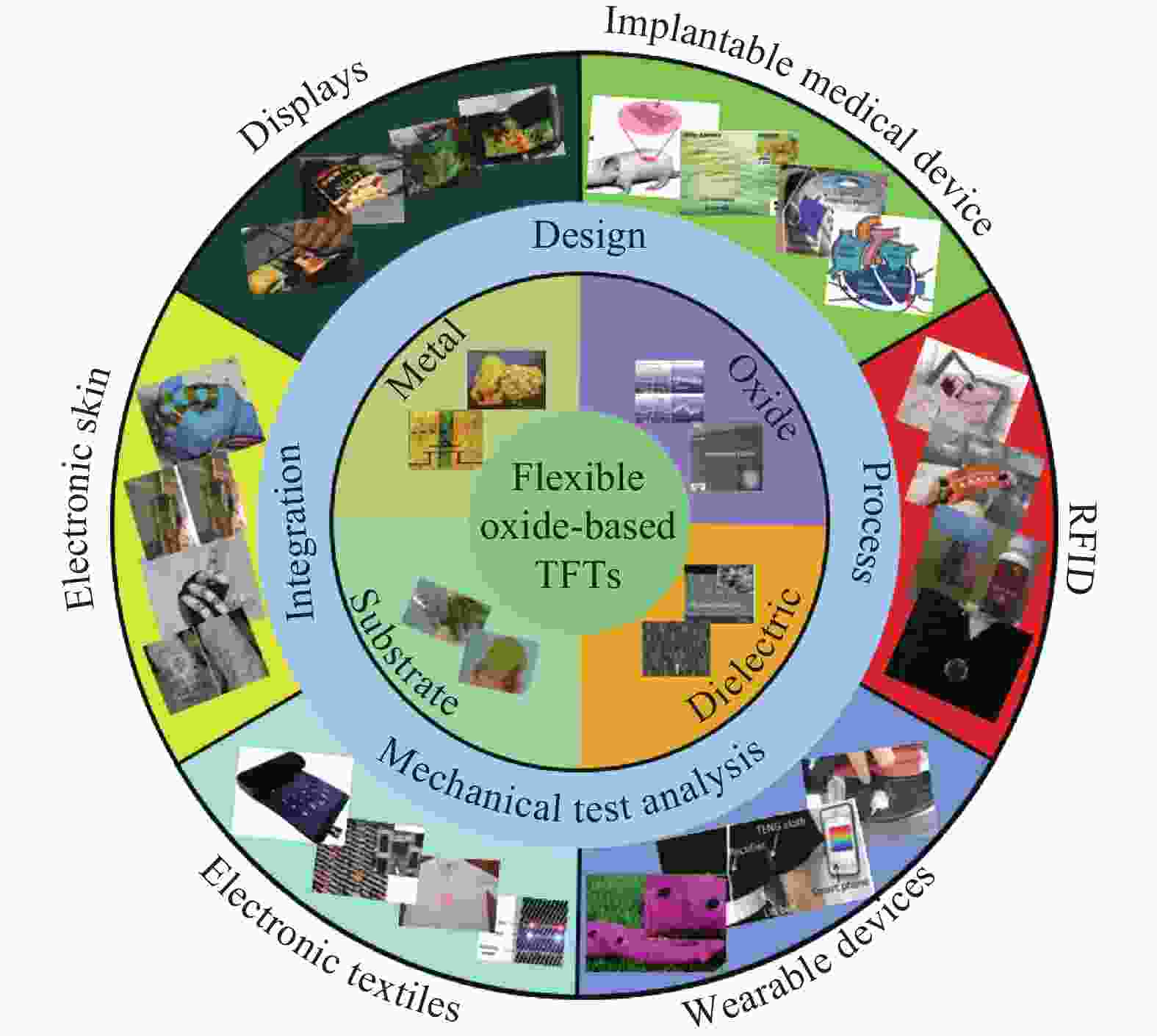

The continuous progress in thin film materials and devices has greatly promoted the development in the field of flexible electronics. As one of the most common thin film devices, thin film transistors (TFTs) are significant building blocks for flexible platforms. Flexible oxide-based TFTs are well compatible with flexible electronic systems due to low process temperature, high carrier mobility, and good uniformity. The present article is a review of the recent progress and major trends in the field of flexible oxide-based thin film transistors. First, an introduction of flexible electronics and flexible oxide-based thin film transistors is given. Next, we introduce oxide semiconductor materials and various flexible oxide-based TFTs classified by substrate materials including polymer plastics, paper sheets, metal foils, and flexible thin glass. Afterwards, applications of flexible oxide-based TFTs including bendable sensors, memories, circuits, and displays are presented. Finally, we give conclusions and a prospect for possible development trends.

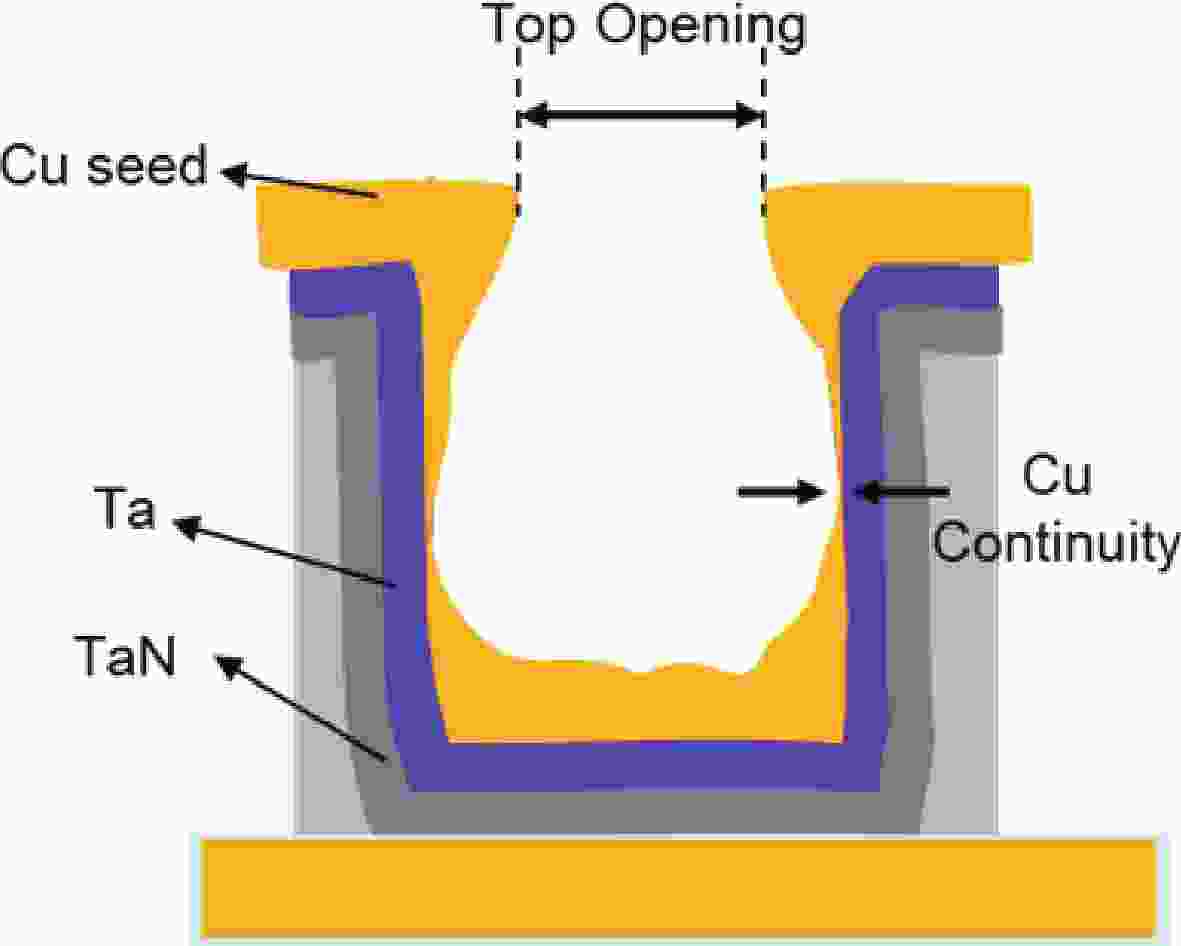

The downscaling of logic devices has posed numerous engineering and manufacturing challenges in copper (Cu) interconnections. The primary failure modes of Cu filling defects are narrow top openings and discontinuous Cu seeds on sidewalls. This study investigates the influence and mechanism of layout on Cu filling defects. Dense line wires with uneven local layouts are prone to defects, which is attributed to the altered distribution of additives in electrochemical plating (ECP), leading to differences in bottom-up filling behavior. It is demonstrated that large-sized metal conductor regions adjacent to dense line wires adsorb substantial amounts of suppressor, resulting in sparse current density in these areas. Given the fixed total local current density, the sparseness of current density in adjacent regions inevitably diverts more current lines to the dense line wire areas. The excessive current density exceeds the local redistribution capacity of additives, causing premature sealing of trench tops and the formation of void defects. A low-current plating process significantly mitigates these defects but may compromise the protective capability of the Cu seed. Additionally, the perimeter density of the layout serves as an effective evaluation index.

The computational cost of TCAD simulations is becoming prohibitively high with the complexity of advanced process technologies, making simulation acceleration a critical research priority. While end-to-end surrogate models mapping process recipes to device structures and characteristics offer a promising alternative, their application is often limited by poor generalizability and explainability. In this work, we present MPNet, a modular deep learning surrogate modeling framework for process TCAD. MPNet comprises distinct surrogate models for individual process modules, which are assembled into an integrated framework. These modular models employ a novel UNet-attention feature evolution method to capture the complex evolutions of device geometry and doping profiles. Each module can be trained separately on its individual process, after which the modules are cascaded and jointly fine-tuned to minimize error accumulation throughout the cascade. The efficacy of the proposed MPNet framework is demonstrated through a MOSFET integrated process TCAD case study. Results show that MPNet achieves a computational speedup of over 103 times compared to conventional TCAD, while maintaining predictive fidelity exceeding 98%. Finally, to illustrated the application of the proposed framework, MPNet is coupled with a PSO algorithm, showcasing its utility for fast process optimization to meet specific process targets.

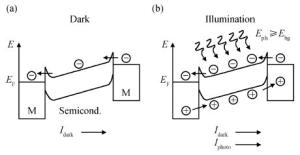

In a recent article, Chen et al. [Electrochimica Acta, 2014, 130: 279] presented their fabrication and characterization results on a graphene/n-Si solar cell where the Au nanoparticles were inserted in graphene to increase its optical and electrical properties. The higher efficiency of the device was attributed to increased conductivity of graphene after doping with Au nanoparticles. However, the knowledge in the field of Schottky diode solar cells relates this to increased band bending at the junction. Also, to explain the instability behaviour, they concluded that the growth of silicon oxide on the Si surface or oxygen adsorption on the window layer resulted in the device performance increasing initially and decreasing in the end. However, this instability seems to be due to variation in series resistance reduced at the beginning because of slightly lowered Fermi level and increased at the end by the self-compensation by deep in-diffusion of Au nanoparticles into n-Si layer. We also propose that inserting a very thin p-type layer at the junction will enhance the carrier collection and performance of this device.

Two-dimensional (2D) materials with unique properties have received a great deal of attention in recent years. This family of materials has rapidly established themselves as intriguing building blocks for versatile nanoelectronic devices that offer promising potential for use in next generation optoelectronics, such as photodetectors. Furthermore, their optoelectronic performance can be adjusted by varying the number of layers. They have demonstrated excellent light absorption, enabling ultrafast and ultrasensitive detection of light in photodetectors, especially in their single-layer structure. Moreover, due to their atomic thickness, outstanding mechanical flexibility, and large breaking strength, these materials have been of great interest for use in flexible devices and strain engineering. Toward that end, several kinds of photodetectors based on 2D materials have been reported. Here, we present a review of the state-of-the-art in photodetectors based on graphene and other 2D materials, such as the graphene, transition metal dichalcogenides, and so on.