| Citation: |

Yuxiao Lu, Lu Sun, Zhe Li, Jianjun Zhou. A single-channel 10-bit 160 MS/s SAR ADC in 65 nm CMOS[J]. Journal of Semiconductors, 2014, 35(4): 045009. doi: 10.1088/1674-4926/35/4/045009

****

Y X Lu, L Sun, Z Li, J J Zhou. A single-channel 10-bit 160 MS/s SAR ADC in 65 nm CMOS[J]. J. Semicond., 2014, 35(4): 045009. doi: 10.1088/1674-4926/35/4/045009.

|

A single-channel 10-bit 160 MS/s SAR ADC in 65 nm CMOS

DOI: 10.1088/1674-4926/35/4/045009

More Information

-

Abstract

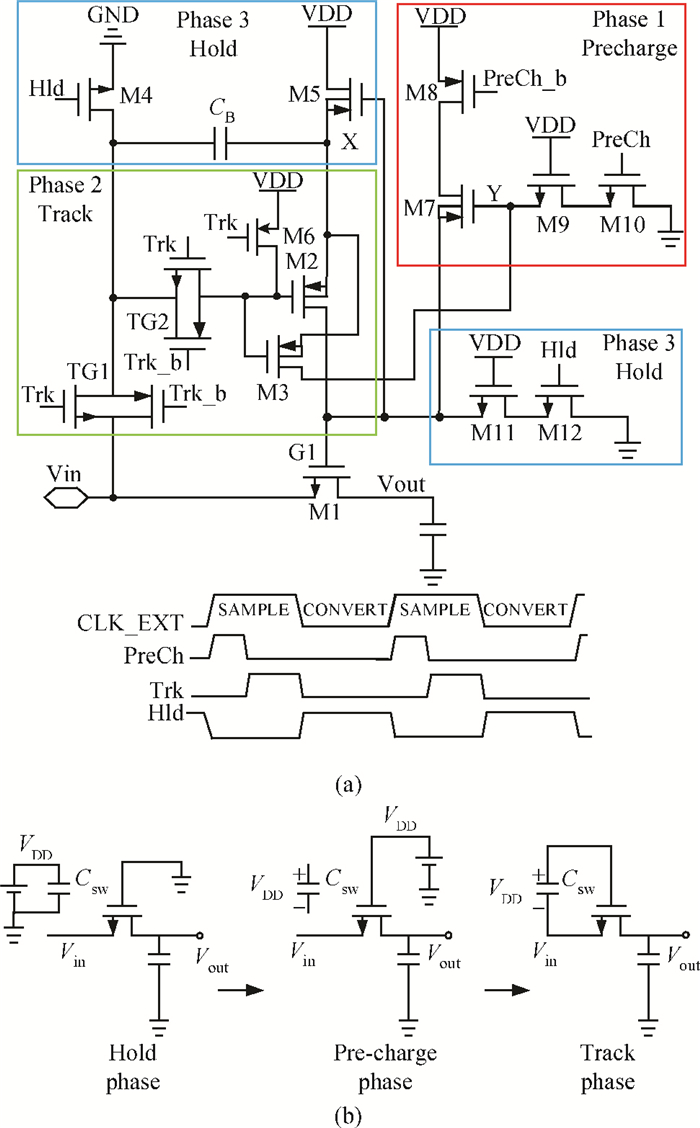

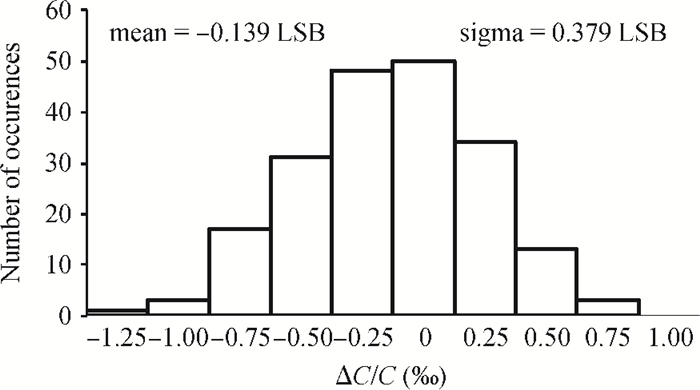

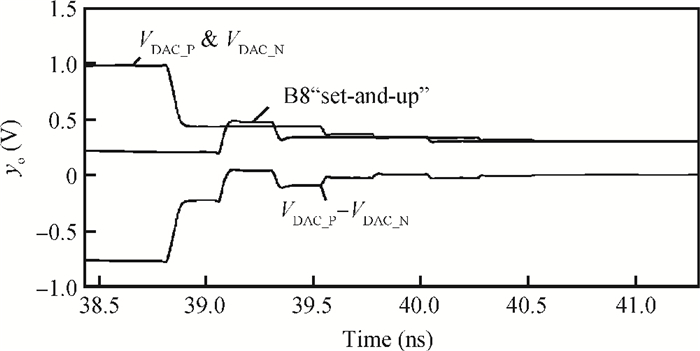

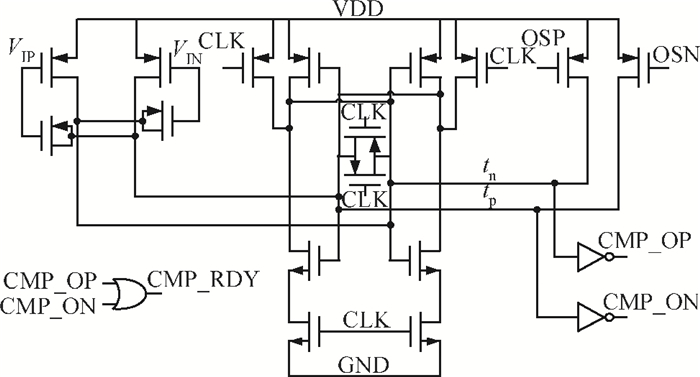

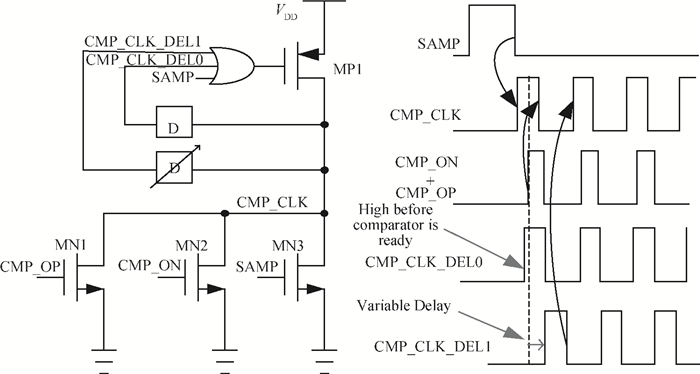

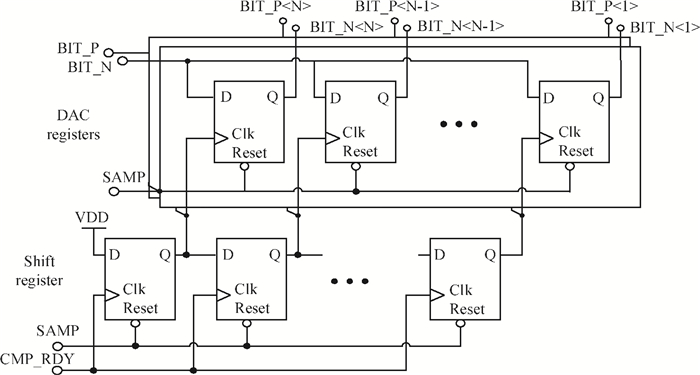

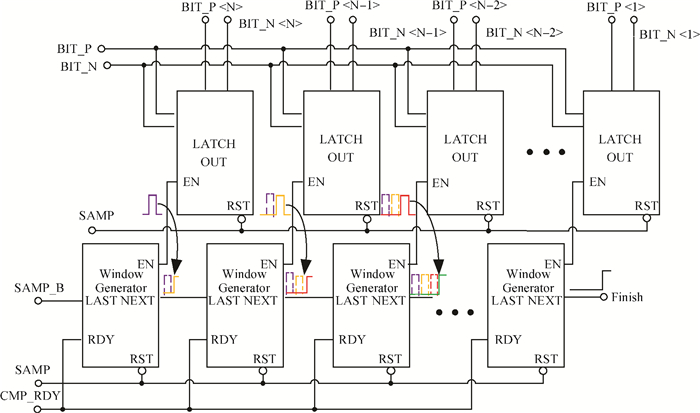

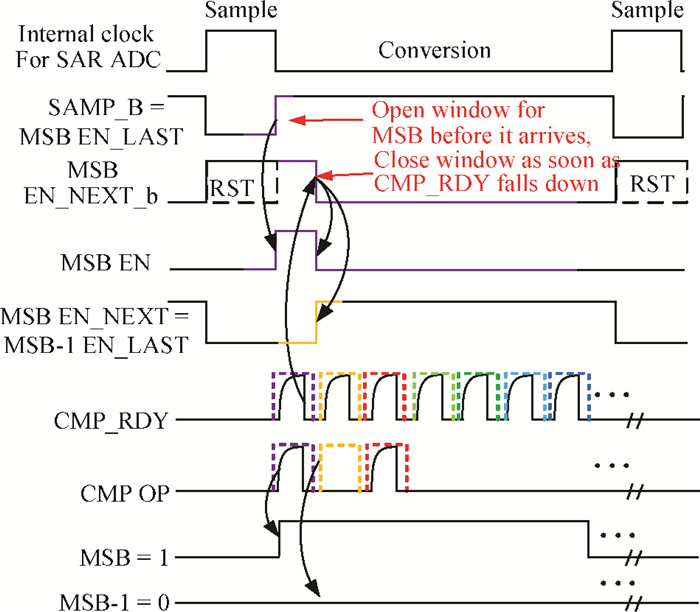

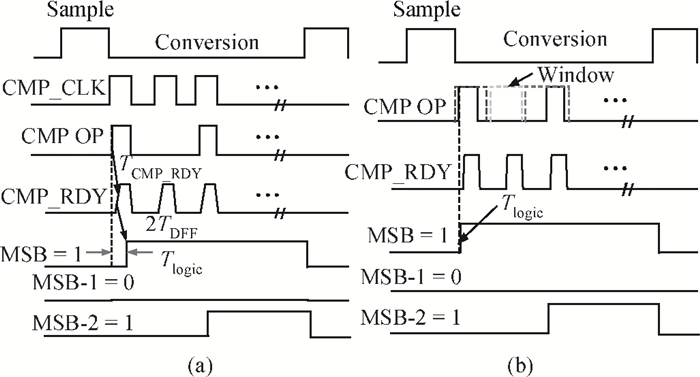

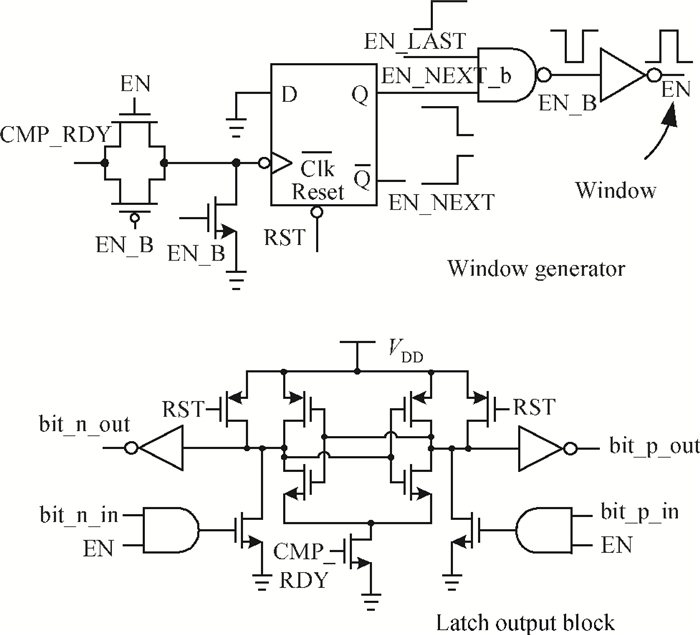

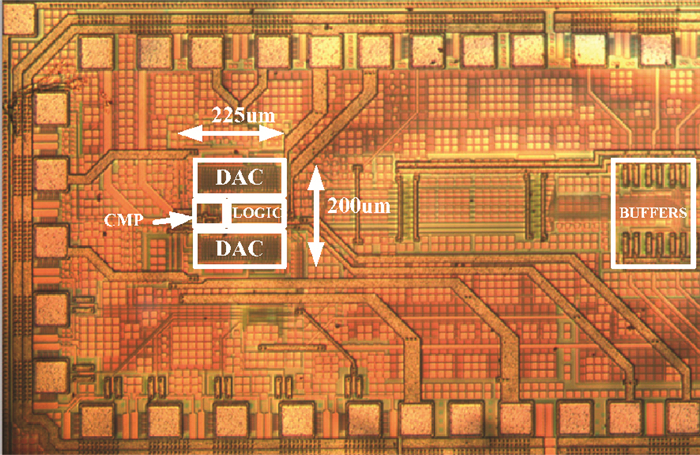

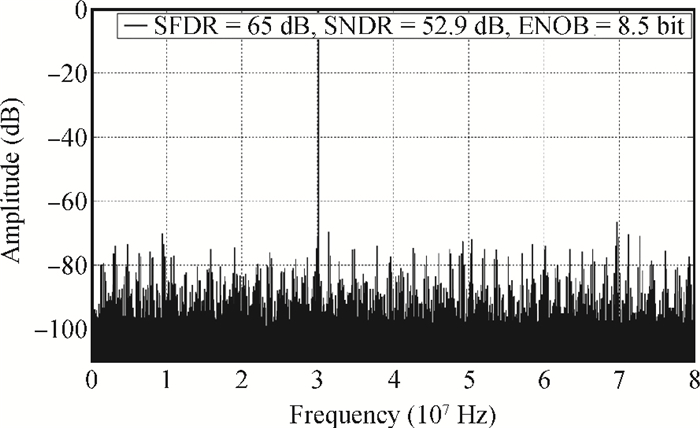

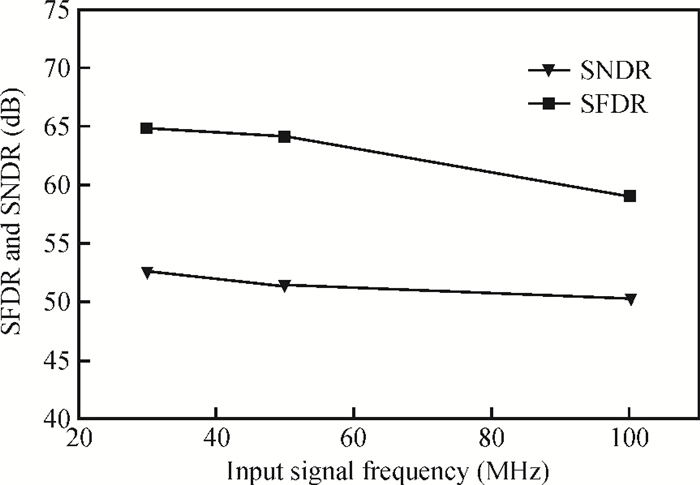

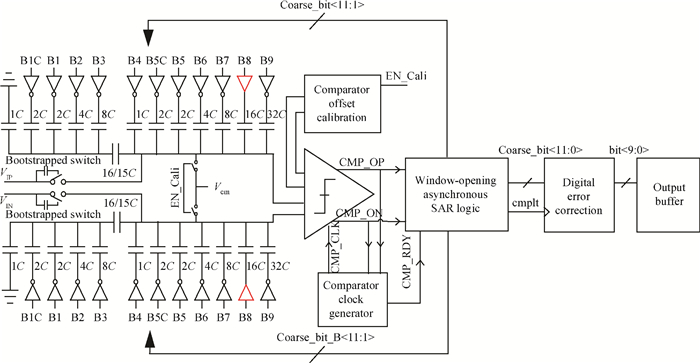

This paper demonstrates a single-channel 10-bit 160 MS/s successive-approximation-register (SAR) analog-to-digital converter (ADC) in 65 nm CMOS process with a 1.2 V supply voltage. To achieve high speed, a new window-opening logic based on the asynchronous SAR algorithm is proposed to minimize the logic delay, and a partial set-and-down DAC with binary redundancy bits is presented to reduce the dynamic comparator offset and accelerate the DAC settling. Besides, a new bootstrapped switch with a pre-charge phase is adopted in the track and hold circuits to increase speed and reduce area. The presented ADC achieves 52.9 dB signal-to-noise distortion ratio and 65 dB spurious-free dynamic range measured with a 30 MHz input signal at 160 MHz clock. The power consumption is 9.5 mW and a core die area of 250×200 μm2 is occupied.-

Keywords:

- SAR ADC,

- asynchronous clock,

- SAR logic,

- Bootstrapped switch

-

References

[1] Kull L, Toifl T, Schmatz M, et al. A 3.1 mW 8 b 1.2 GS/s single-channel asynchronous SAR ADC with alternate comparators for enhanced speed in 32nm digital SOI CMOS. IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013:468 http://ieeexplore.ieee.org/document/6607254/[2] Lien Y C. A 4.5-mW 8-b 750-MS/s 2-b/step asynchronous subranged SAR ADC in 28-nm CMOS technology. Symposium on VLSI Circuits (VLSIC), 2012:88 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=6243803[3] Tao J, Wing L, Zhong F Y, et al. A single-channel, 1.25-GS/s, 6-bit, 6.08-mW asynchronous successive-approximation ADC with improved feedback delay in 40-nm CMOS. IEEE J Solid-State Circuits, 2012, 47(10):2444 doi: 10.1109/JSSC.2012.2204543[4] Liu C C, Chang S J, Huang G Y, et al. A 10 b 100 MS/s 1.13 mW SAR ADC with binary-scaled error compensation. IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2010:386 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=5433970[5] Kuttner F. A 1.2 V 10 b 20 MSample/s non-binary successive approximation ADC in 0.13μm CMOS. IEEE International Solid-State Circuits Conference (ISSCC), 2002, 1:176 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=992181[6] Liu W, Huang P, Chiu Y. A 12 b 22.5/45 MS/s 3.0 mW 0.059 mm2 CMOS SAR ADC achieving over 90 dB SFDR. IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2010:380 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=5433830[7] Hong H K, Kim W, Park S J, et al. A 7 b 1 GS/s 7.2 mW nonbinary 2b/cycle SAR ADC with register-to-DAC direct control. IEEE Custom Integrated Circuits Conference (CICC), 2012:1 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?arnumber=6330609&filter%3DAND(p_IS_Number%3A6330557)[8] Wei H, Chan C H, Chio U F, et al. An 8-b 400-MS/s 2-b-per-cycle SAR ADC with resistive DAC. IEEE J Solid-State Circuits, 2012, 47(11):2763 doi: 10.1109/JSSC.2012.2214181[9] Saberi M, Lotfi R. Segmented architecture for successive approximation analog-to-digital converters. IEEE Trans Very Large Scale Integration (VLSI) Systems, 2013, PP(99):1 http://ieeexplore.ieee.org/document/6490419/[10] Alpman E, Lakdawala H, Carley L R, et al. A 1.1V 50mW 2.5GS/s 7b time-interleaved C-2C SAR ADC in 45nm LP digital CMOS. IEEE International Solid-State Circuits Conference Digest of Technical Papers, 2009:76, 77a http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=4977315[11] Cao Z, Yan S, Li Y. A 32mW 1.25GS/s 6b 2b/step SAR ADC in 0.13μm CMOS. IEEE International Solid-State Circuits Conference Digest of Technical Papers, 2008:542. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=4523297[12] Doris K, Janssen E, Nani C, et al. A 480 mW 2.6 GS/s 10b time-interleaved ADC with 48.5 dB SNDR up to Nyquist in 65 nm CMOS. IEEE J Solid-State Circuits, 2011, 46(12):2821 doi: 10.1109/JSSC.2011.2164961[13] Huber D J, Chandler R J, Abidi A A. A 10b 160 MS/s 84 mW 1 V Subranging ADC in 90nm CMOS. IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2007:454 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=4242461[14] Jeon Y D, Cho Y K, Nam J W, et al. A 9.15mW 0.22 mm2 10b 204MS/s pipelined SAR ADC in 65nm CMOS. IEEE Custom Integrated Circuits Conference (CICC), 2010:1 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=5617457[15] Zhu Y, Chan C H, Sin S W, et al. A 50-fJ 10-b 160-MS/s pipelined-SAR ADC decoupled flip-around MDAC and self-embedded offset cancellation. IEEE J Solid-State Circuits, 2012, 47(11):2614 doi: 10.1109/JSSC.2012.2211695[16] Ma Jun, Guo Yawei, Wu Yue, et al. A 1-V 10-bit 80-MS/s 1.6-mW SAR ADC in 65-nm GP CMOS. Journal of Semiconductors, 2013, 34(8):085014 doi: 10.1088/1674-4926/34/8/085014 -

Proportional views

DownLoad:

DownLoad: