| Citation: |

Wenwei He, Qiao Meng, Yi Zhang, Kai Tang. A 2 GS/s 8-bit folding and interpolating ADC in 90 nm CMOS[J]. Journal of Semiconductors, 2014, 35(8): 085004. doi: 10.1088/1674-4926/35/8/085004

****

W W He, Q Meng, Y Zhang, K Tang. A 2 GS/s 8-bit folding and interpolating ADC in 90 nm CMOS[J]. J. Semicond., 2014, 35(8): 085004. doi: 10.1088/1674-4926/35/8/085004.

|

A 2 GS/s 8-bit folding and interpolating ADC in 90 nm CMOS

DOI: 10.1088/1674-4926/35/8/085004

More Information

-

Abstract

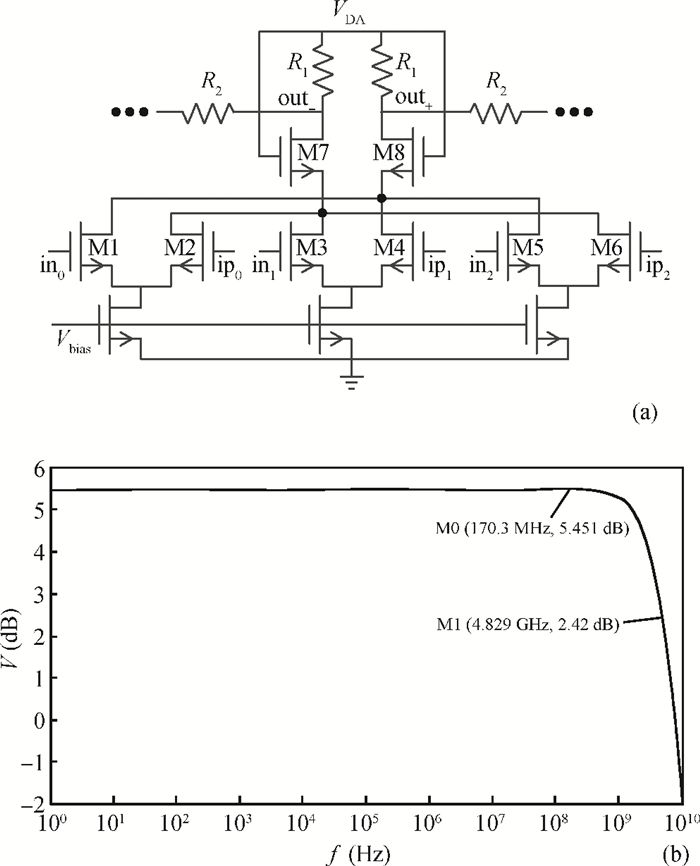

A single-channel 2 GS/s 8-bit analog-to-digital converter in 90 nm CMOS process technology is presented. It utilizes cascade folding architecture, which incorporates an additional inter-stage sample-and-hold amplifier between the folding circuits to enhance the quantization time. It also uses the foreground on-chip digital-assisted calibration circuit to improve the linearity of the circuit. The post simulation results demonstrate that it has a differential nonlinearity < ±0.3 LSB and an integral nonlinearity < ±0.25 LSB at the Nyquist frequency. Moreover, 7.338 effective numbers of bits can be achieved at 2 GSPS. The whole chip area is 0.88×0.88 mm2 with the pad. It consumes 210 mW from a 1.2 V single supply. -

References

[1] Taft R C, Menkus C A, Tursi M R, et al. A 1.8-V 1.6 GSample/s 8-b self-calibrating folding ADC with 7.26 ENOB at Nyquist frequency. IEEE J Solid-State Circuits, 2004, 39(12):2107 doi: 10.1109/JSSC.2004.836242[2] Zhang Yi, Meng Qiao, Huang Qing, et al. A track-and-hold amplifier for 1 GSps 8 bit ADC in 0. 18μm CMOS process. International Conference on Advanced Technologies for Communication (ATC), Hanoi, Vietnam, 2012: 5[3] Plassche R. Integrated analog-to-digital and digital-to-analog converters. Boston, MA: Kluwer, 1994[4] Allen P E, Holberg D R. CMOS analog circuit design. 2nd ed. New York Oxford University Press, 2002[5] Park S, Flynn M P. Design techniques for high performance CMOS flash analog-to-digital converters. Proceedings of the 2005 European Conference on Circuit Theory and Design, 2005:131 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=1522927[6] Figueiredo P M, Vital J C. Offset reduction techniques in high-speed analog-to-digital converters. Springer, 2009[7] Nikolic B, Oklobdzija V G, Stojanovic V, et al. Improved sense-amplifier-based flip-flop:design and measurements. IEEE J Solid-State Circuits, 2010, 35(6):876 http://ieeexplore.ieee.org/document/845191/[8] Lee J, Choi M B, Park H J, et al. A 7 b 1 GS/s 60 mW folding ADC in 65 nm CMOS. International Digital Object Identifier SoC Design Conference (ISOCC), 2010:338[9] Taft R C, Francese P A, Tursi M R, et al. A 1.8 V 1.0 GS/s 10 b self-calibrating unified-folding-interpolating ADC with 9.1 ENOB at Nyquist frequency. IEEE J Solid-State Circuits, 2009, 44(12):3294 doi: 10.1109/JSSC.2009.2032634[10] Nakajima Y, Sakaguchi A, Ohkido T, et al. A background self-calibrated 6 b 2.7 GS/s ADC with cascade-calibrated folding-interpolating architecture. IEEE J Solid-State Circuits, 2010, 45(4):707 doi: 10.1109/JSSC.2010.2042249 -

Proportional views

DownLoad:

DownLoad: