| Citation: |

Songren Huang, Hong Zhang, Zhenhai Chen, Shuang Zhu, Zongguang Yu, Hongwen Qian, Yue Hao. A 10-bit 250 MSPS charge-domain pipelined ADC with replica controlled PVT insensitive BCT circuit[J]. Journal of Semiconductors, 2015, 36(5): 055012. doi: 10.1088/1674-4926/36/5/055012

****

S R Huang, H Zhang, Z H Chen, S Zhu, Z G Yu, H W Qian, Y Hao. A 10-bit 250 MSPS charge-domain pipelined ADC with replica controlled PVT insensitive BCT circuit[J]. J. Semicond., 2015, 36(5): 055012. doi: 10.1088/1674-4926/36/5/055012.

|

A 10-bit 250 MSPS charge-domain pipelined ADC with replica controlled PVT insensitive BCT circuit

DOI: 10.1088/1674-4926/36/5/055012

More Information

-

Abstract

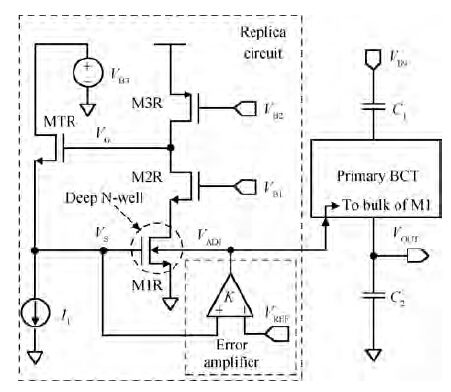

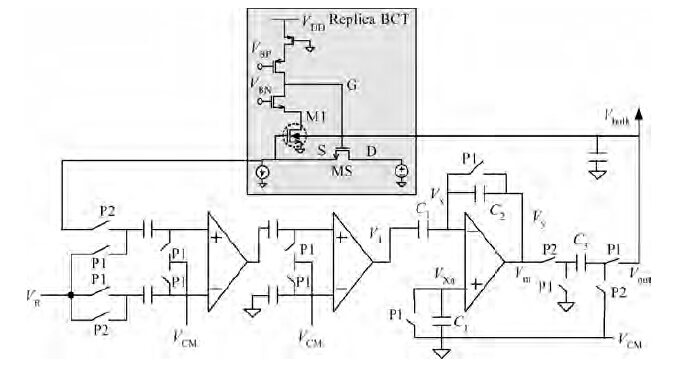

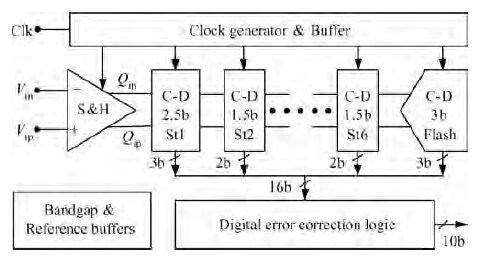

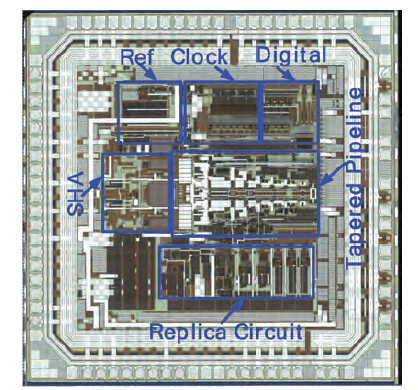

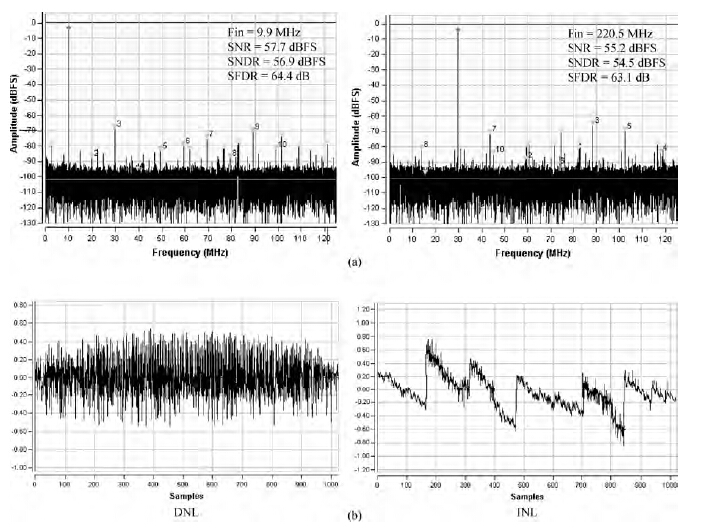

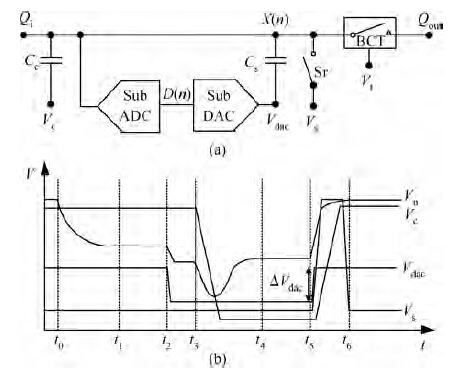

A low power 10-bit 250 MSPS charge-domain (CD) pipelined analog-to-digital converter (ADC) is introduced. The ADC is implemented in MOS bucket-brigade devices (BBDs) based CD pipelined architecture. A replica controlled boosted charge transfer (BCT) circuit is introduced to reject the influence of PVT variations on the charge transfer process. Based on replica controlled BCT, the CD pipelined ADC is designed and realized in a 1P6M 0.18 μ m CMOS process. The ADC achieves the SFDR of 64.4 dB, the SNDR of 56.9 dBFS and the ENOB of 9.2 for a 9.9 MHz input; and the SFDR of 63.1 dB, the SNR of 55.2 dBFS, the SNDR of 54.5 dBFS and the ENOB of 8.7 for a 220.5 MHz input at full sampling rate. The DNL is +0.5/-0.55 LSB and INL is +0.8/-0.85 LSB. The power consumption of the prototype ADC is only 45 mW at 1.8 V supply and it occupies an active die area of 1.56 mm2. -

References

[1] [2] [3] [4] [5] [6] [7] [8] -

Proportional views

DownLoad:

DownLoad: