| Citation: |

Yiluan Guo, Guilei Wang, Chao Zhao, Jun Luo. Simulation and characterization of stress in FinFETs using novel LKMC and nanobeam diffraction methods[J]. Journal of Semiconductors, 2015, 36(8): 086001. doi: 10.1088/1674-4926/36/8/086001

****

Y L Guo, G L Wang, C Zhao, J Luo. Simulation and characterization of stress in FinFETs using novel LKMC and nanobeam diffraction methods[J]. J. Semicond., 2015, 36(8): 086001. doi: 10.1088/1674-4926/36/8/086001.

|

Simulation and characterization of stress in FinFETs using novel LKMC and nanobeam diffraction methods

DOI: 10.1088/1674-4926/36/8/086001

More Information

-

Abstract

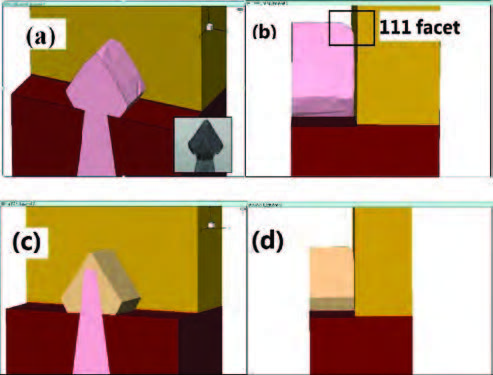

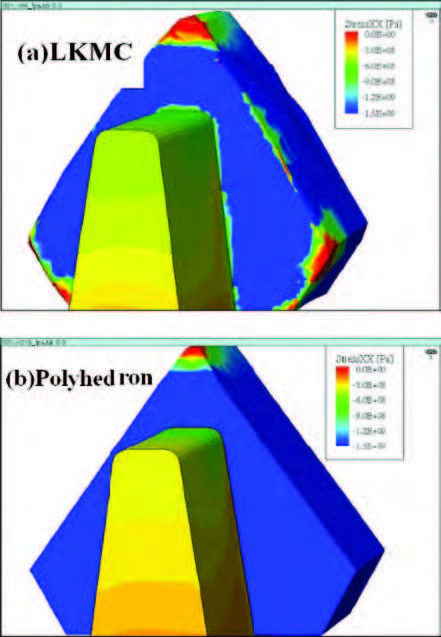

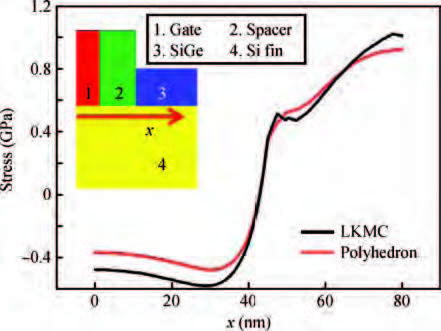

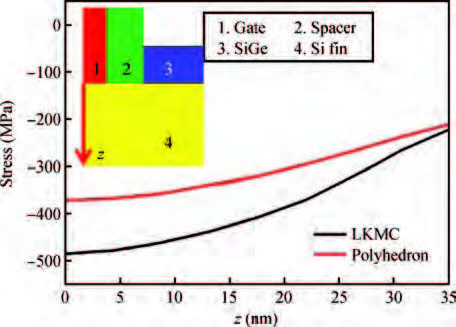

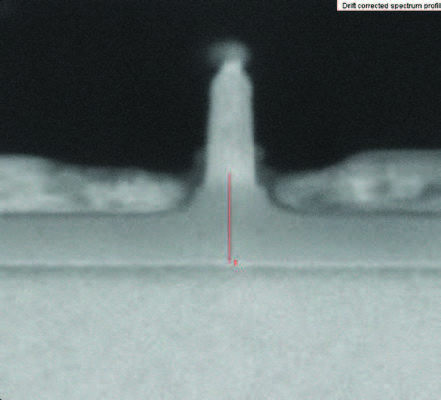

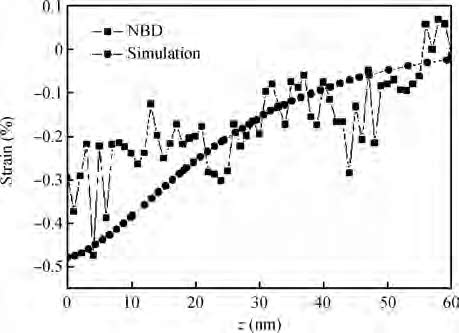

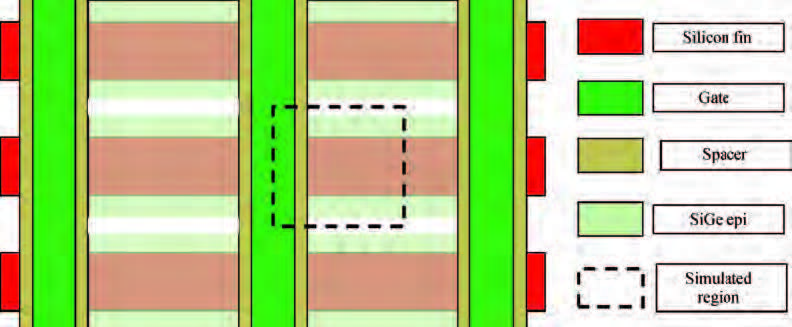

A new simulation method and test instrument has been adopted to verify the traditional stress simulation in FinFET. First, a new algorithm named lattice kinetic Monte Carlo (LKMC) is used to simulate the SiGe epitaxy in source/drain regions and the stress distribution is consequently extracted after the LKMC simulation. Systematic comparison between the traditional polyhedron method and the LKMC method is carried out. The results confirm that extracted stress from both methods is consistent, which verifies the validity of traditional polyhedron method for the purpose of simulating stress in FinFET. In the following experiment, p-type FinFETs with SiGe stressors in source/drain regions are fabricated. The nano beam diffraction (NBD) method is employed to characterize the strain in Si fin. The strain value from the NBD test agrees well with the value extracted from traditional polyhedron simulation.-

Keywords:

- stress,

- simulation,

- FinFET,

- NBD,

- verification

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] -

Proportional views

DownLoad:

DownLoad: