| Citation: |

Yuwei Cai, Zhaohao Zhang, Qingzhu Zhang, Jinjuan Xiang, Gaobo Xu, Zhenhua Wu, Jie Gu, Huaxiang Yin. Investigation of time domain characteristics of negative capacitance FinFET by pulse-train approaches[J]. Journal of Semiconductors, 2021, 42(11): 114101. doi: 10.1088/1674-4926/42/11/114101

Y W Cai, Z H Zhang, Q Z Zhang, J J Xiang, G B Xu, Z H Wu, J Gu, H X Yin, Investigation of time domain characteristics of negative capacitance FinFET by pulse-train approaches[J]. J. Semicond., 2021, 42(11): 114101. doi: 10.1088/1674-4926/42/11/114101.

Export: BibTex EndNote

|

Investigation of time domain characteristics of negative capacitance FinFET by pulse-train approaches

doi: 10.1088/1674-4926/42/11/114101

More Information-

Abstract

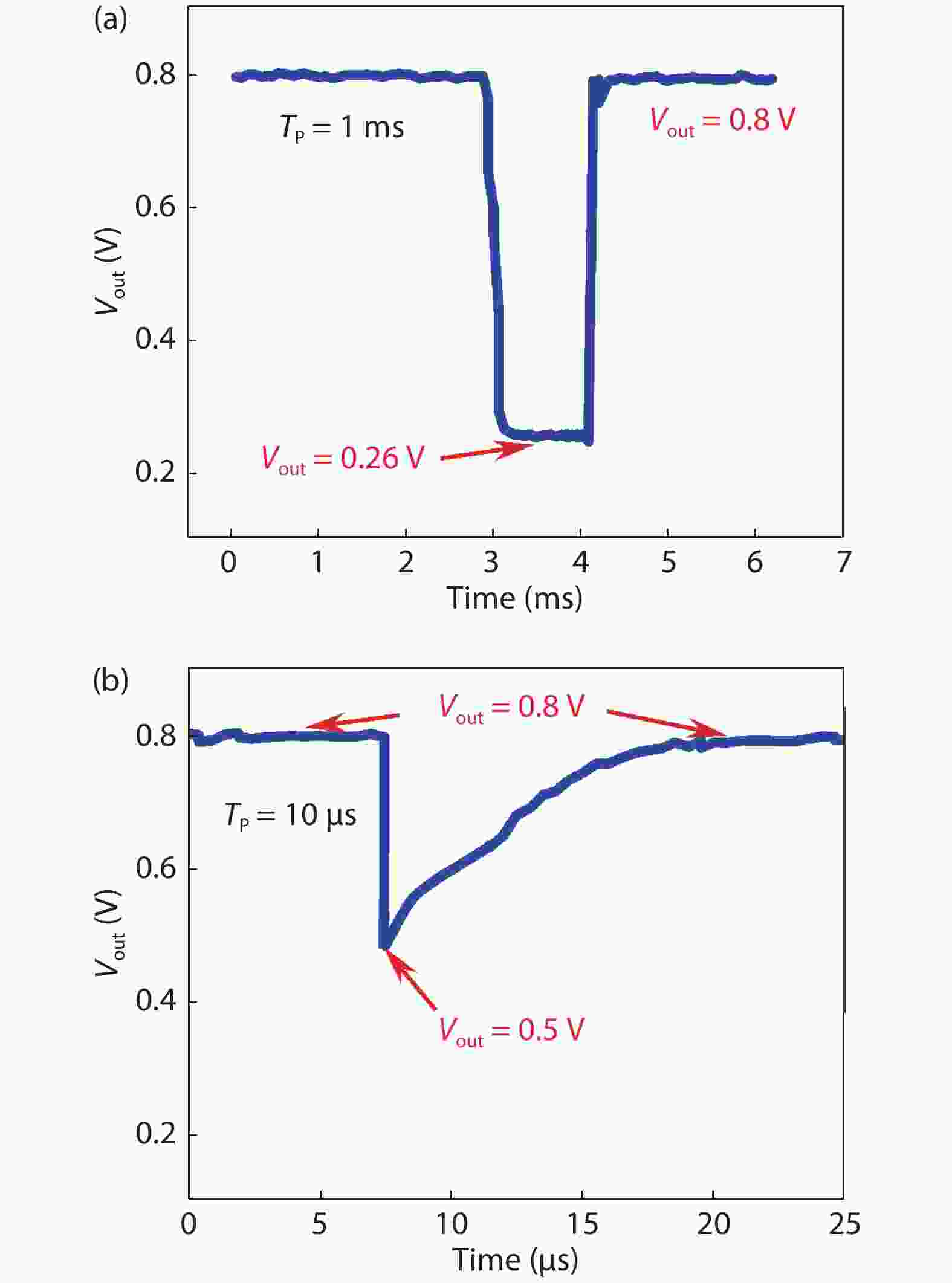

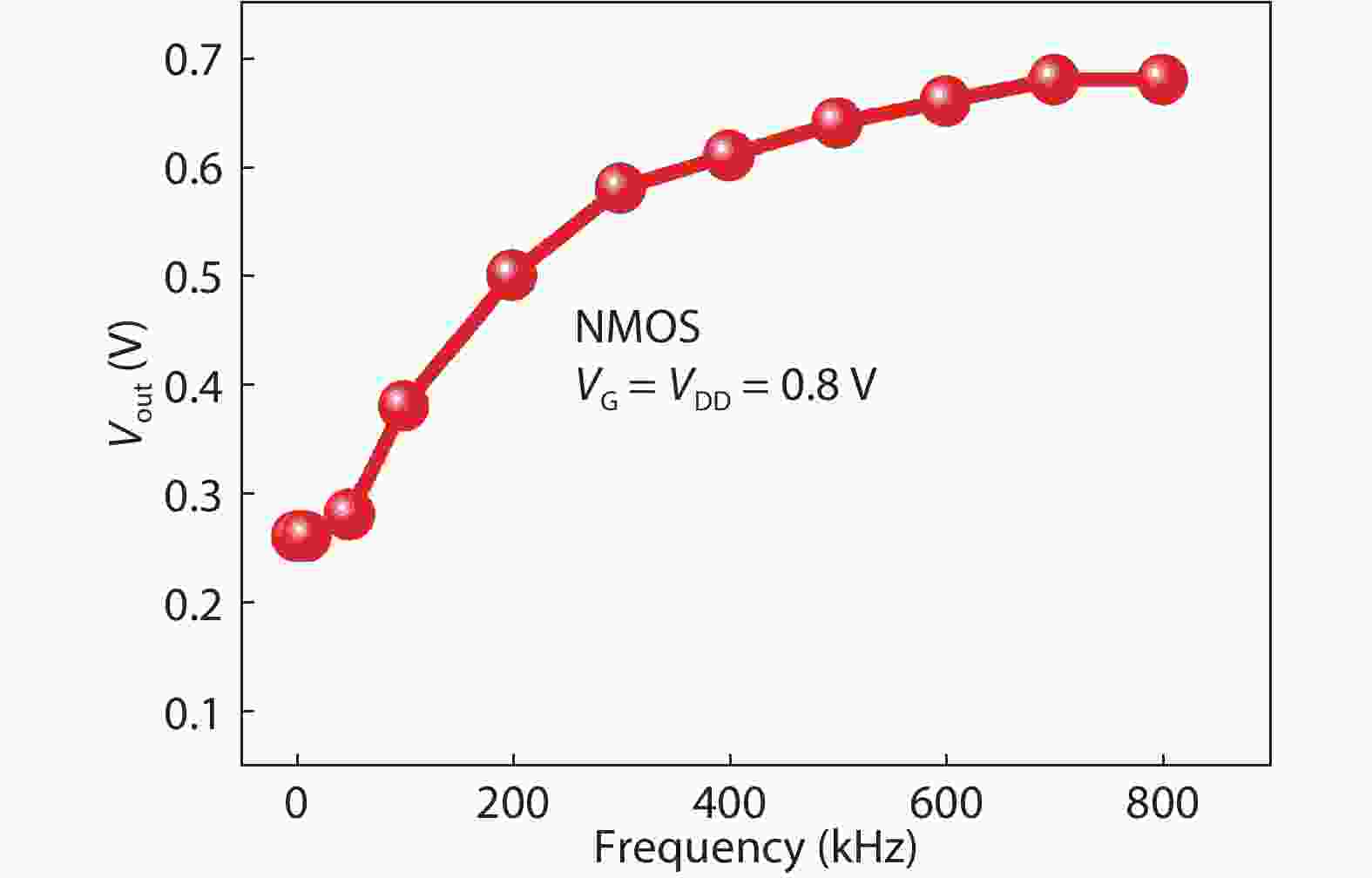

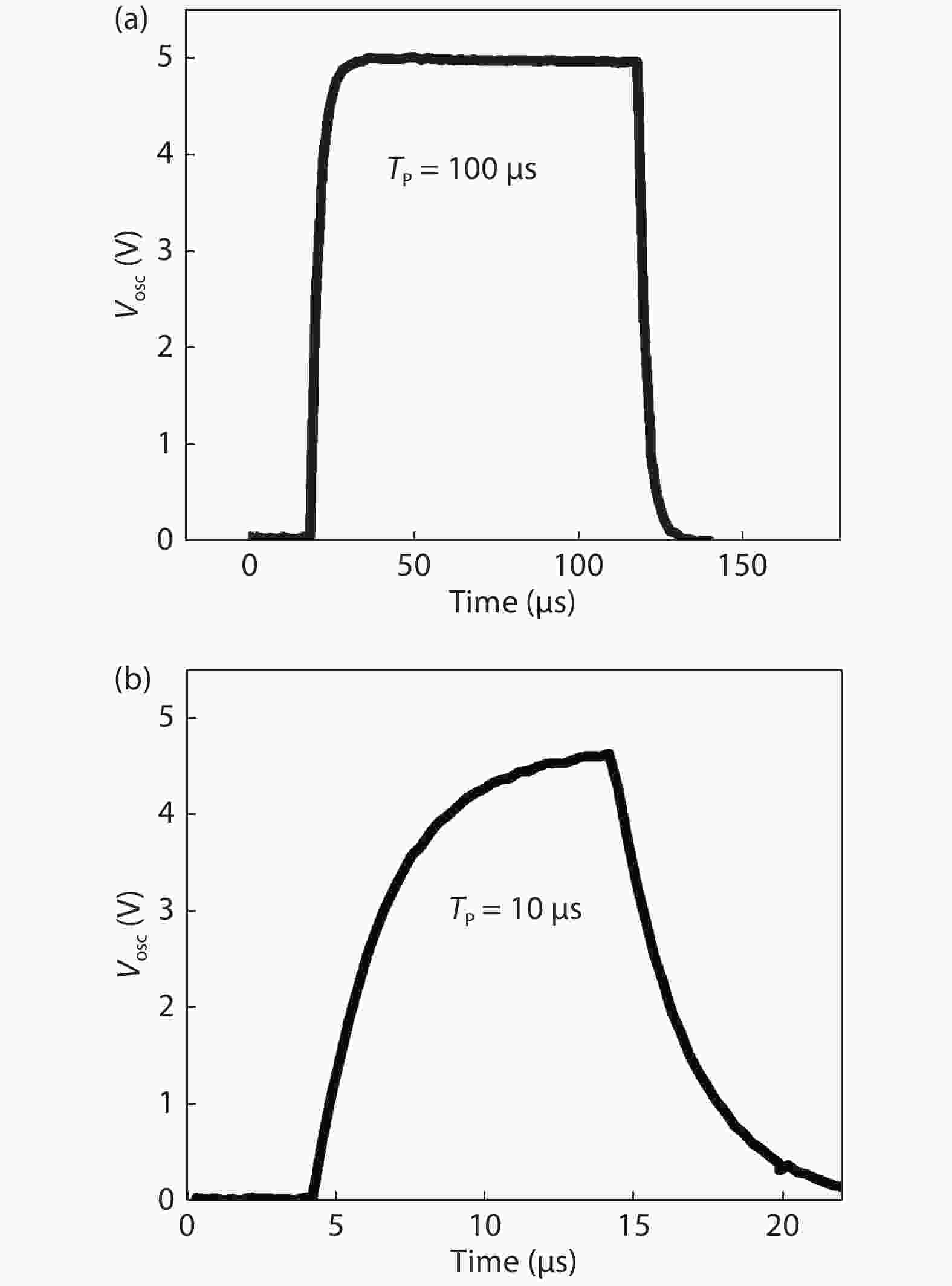

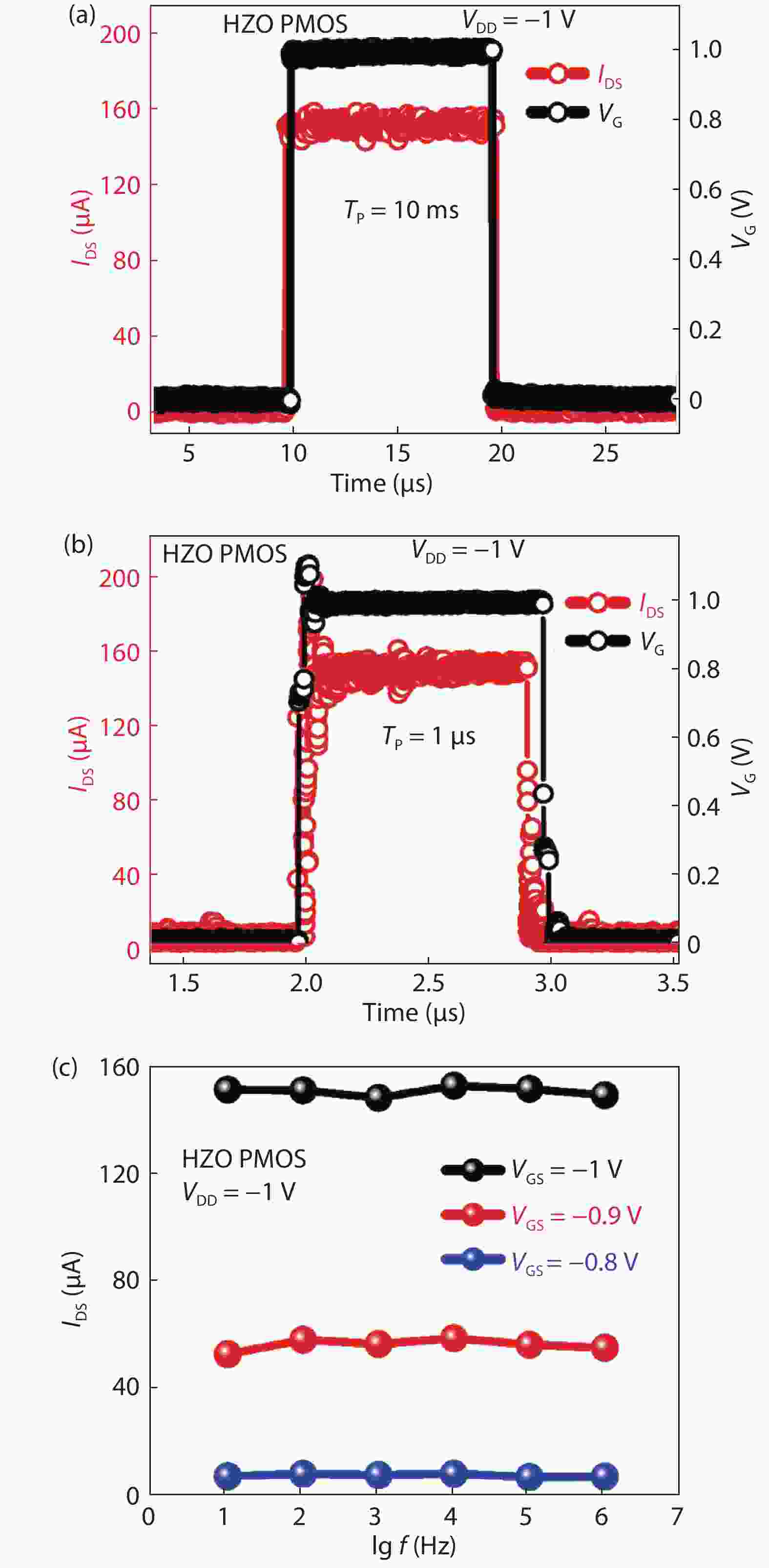

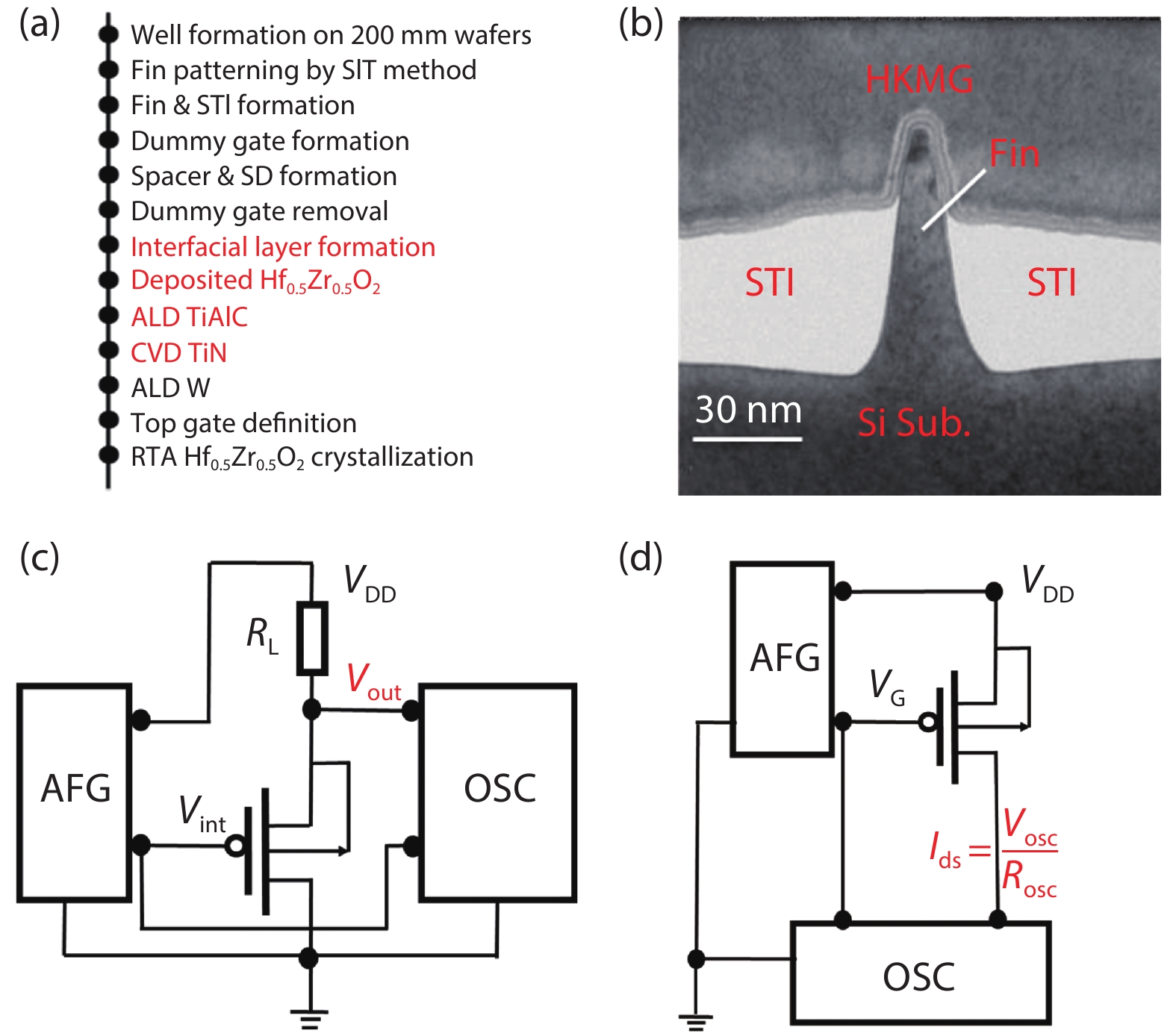

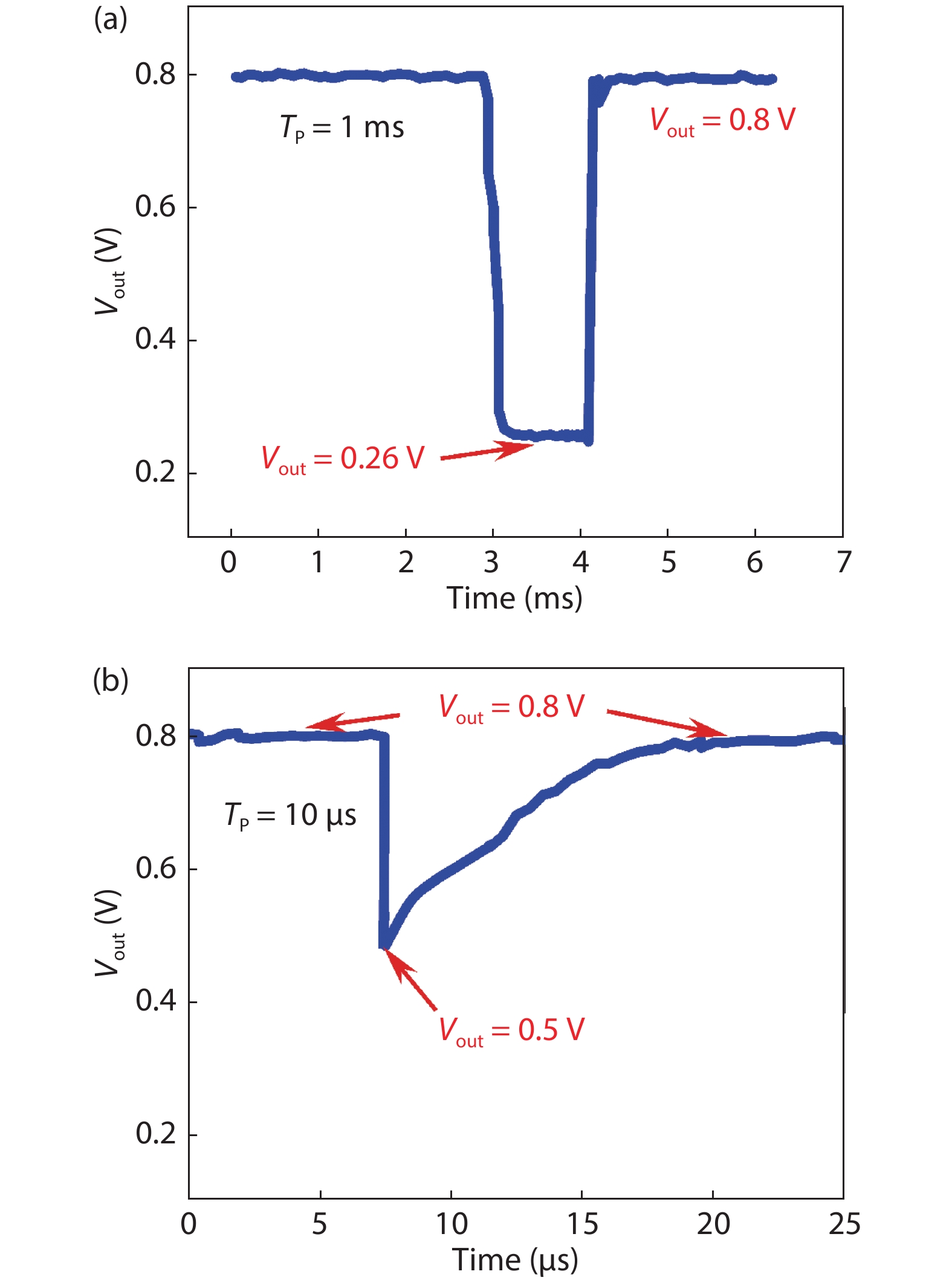

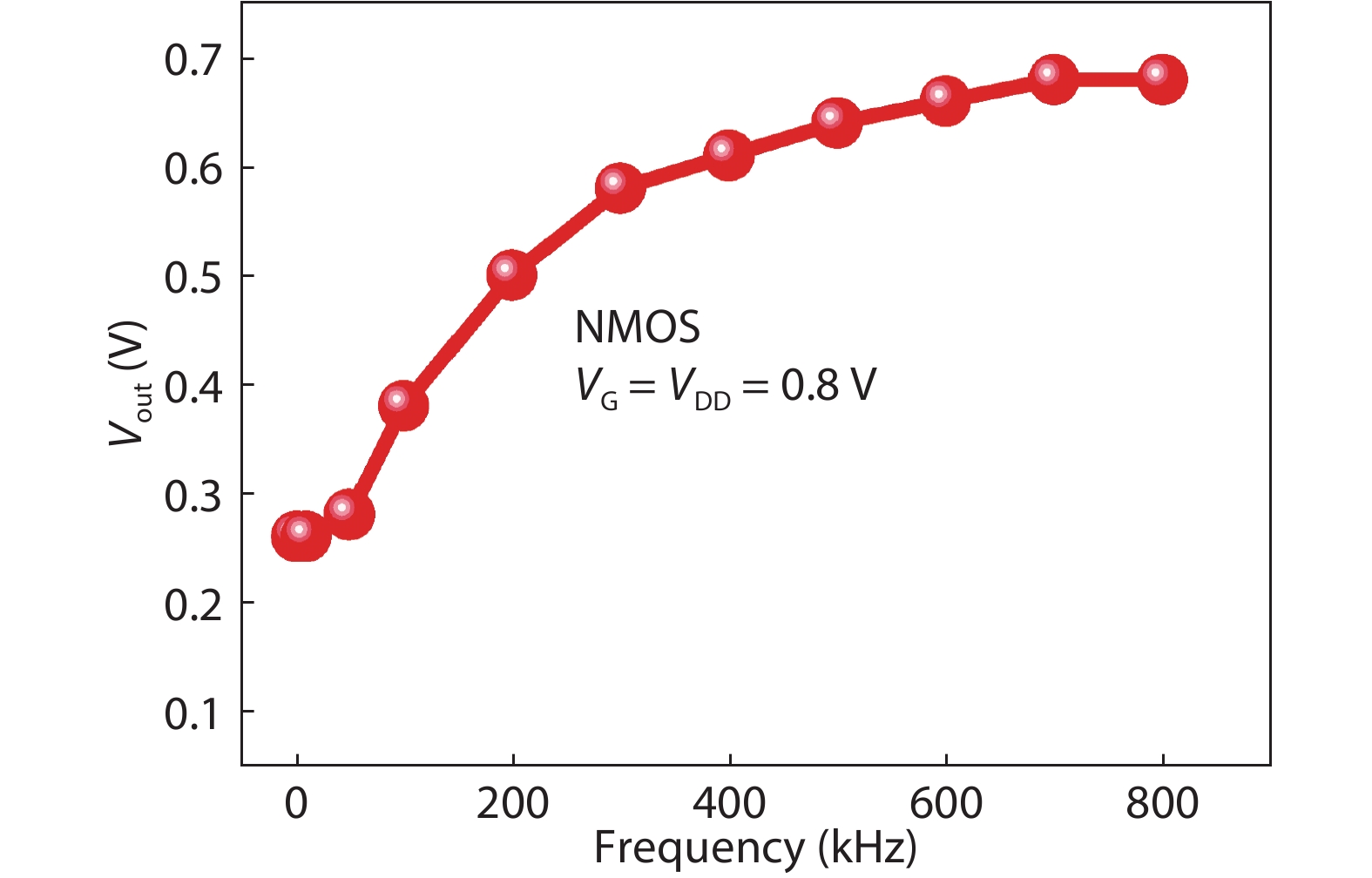

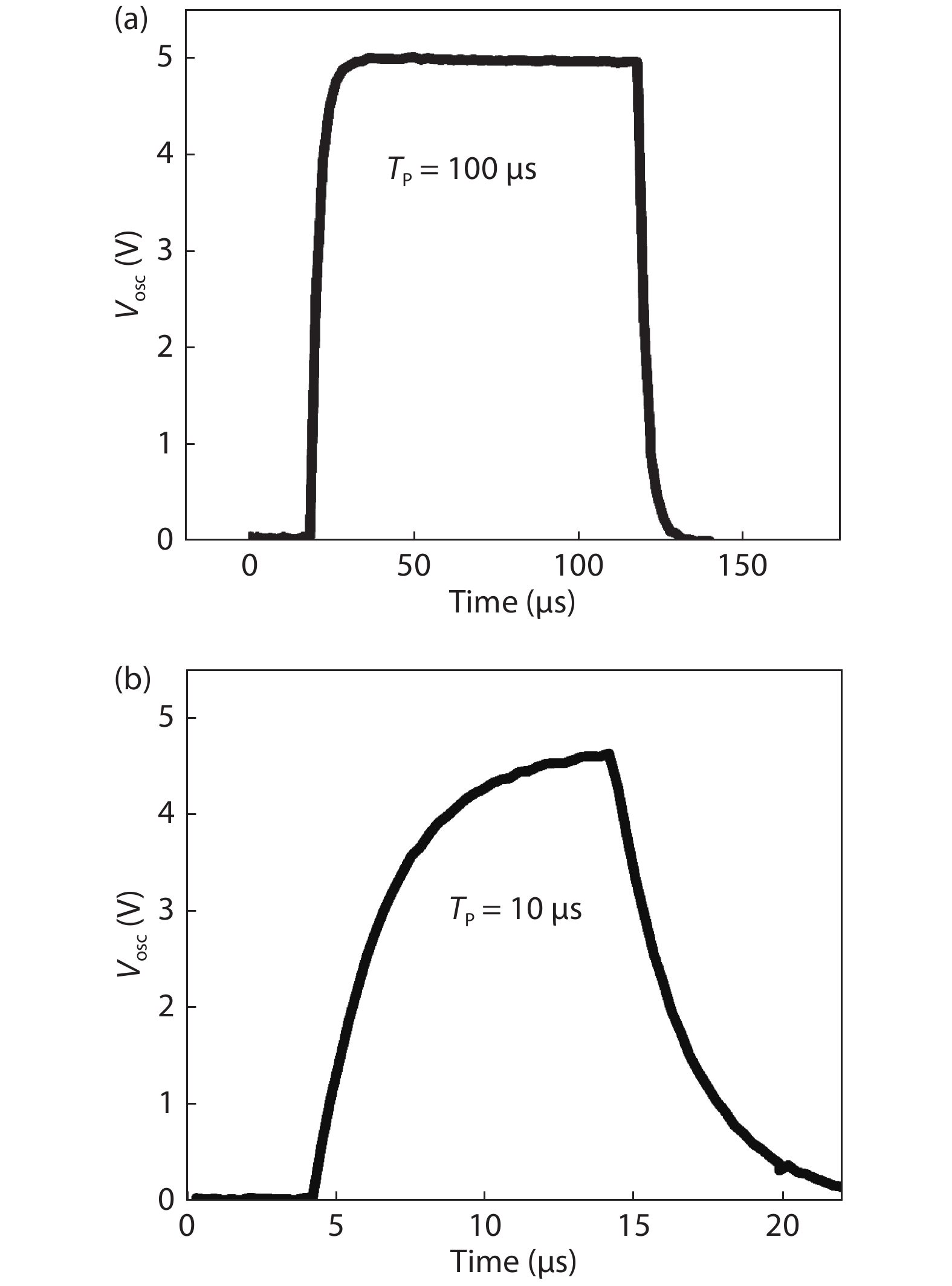

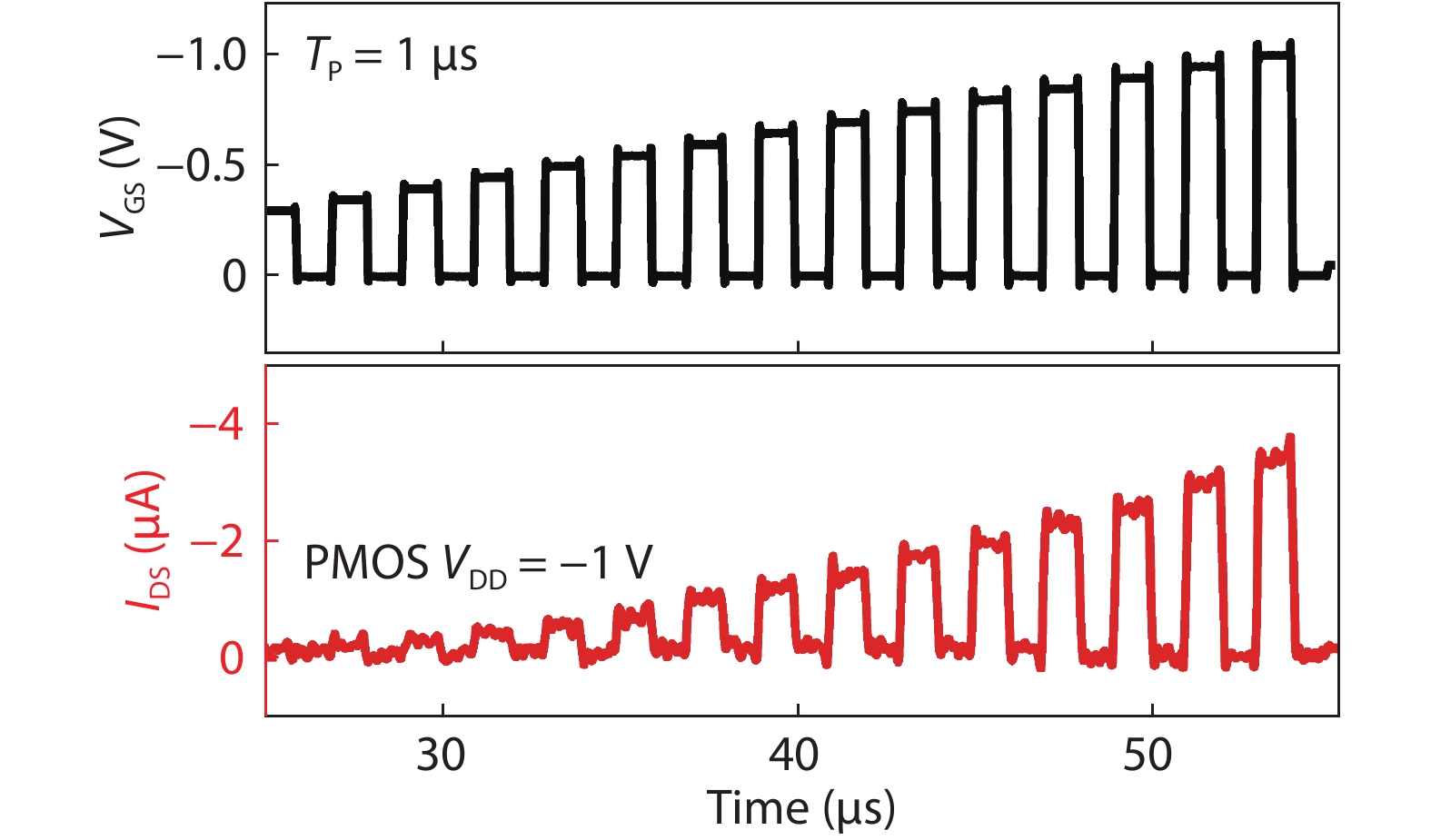

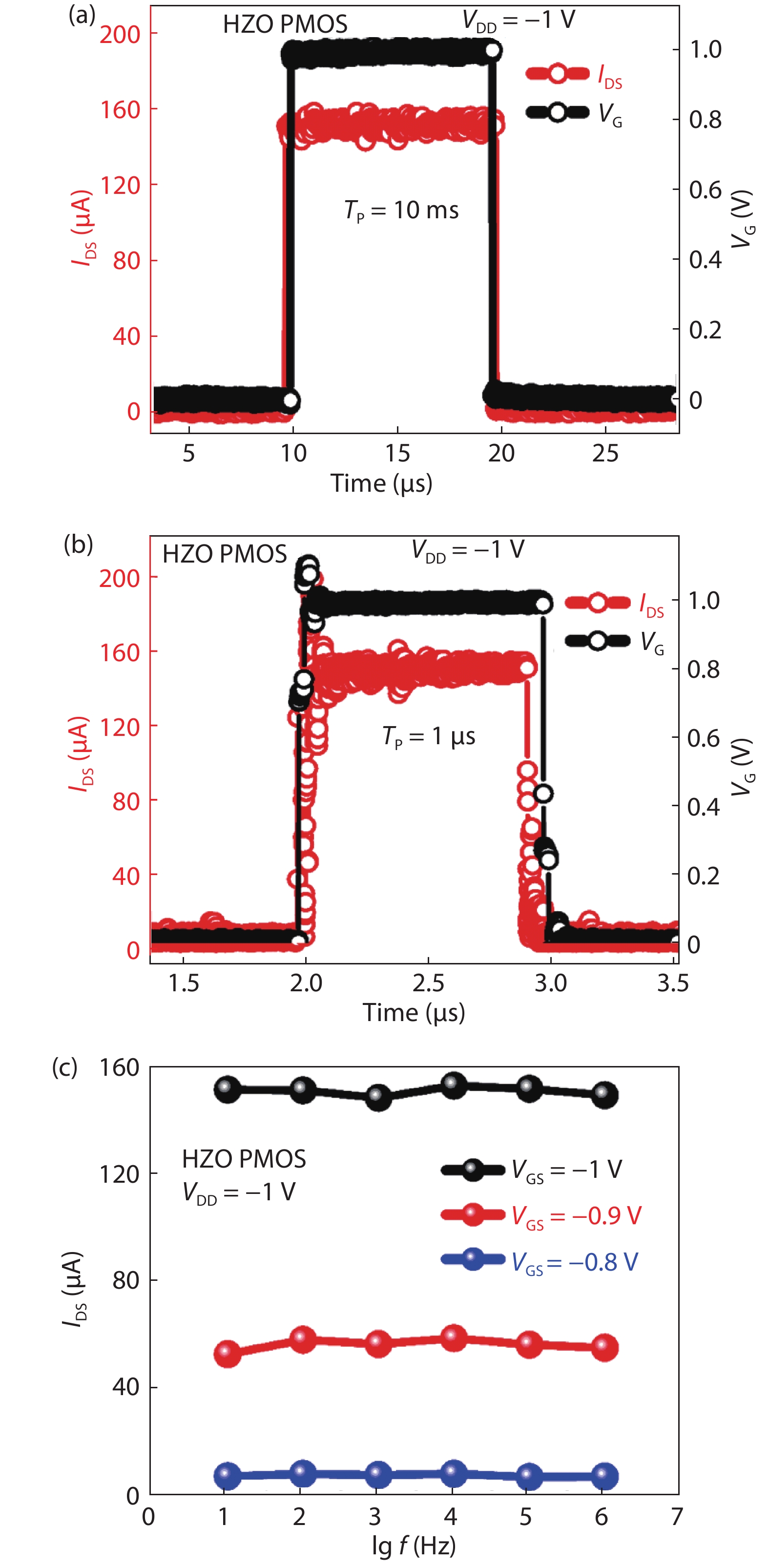

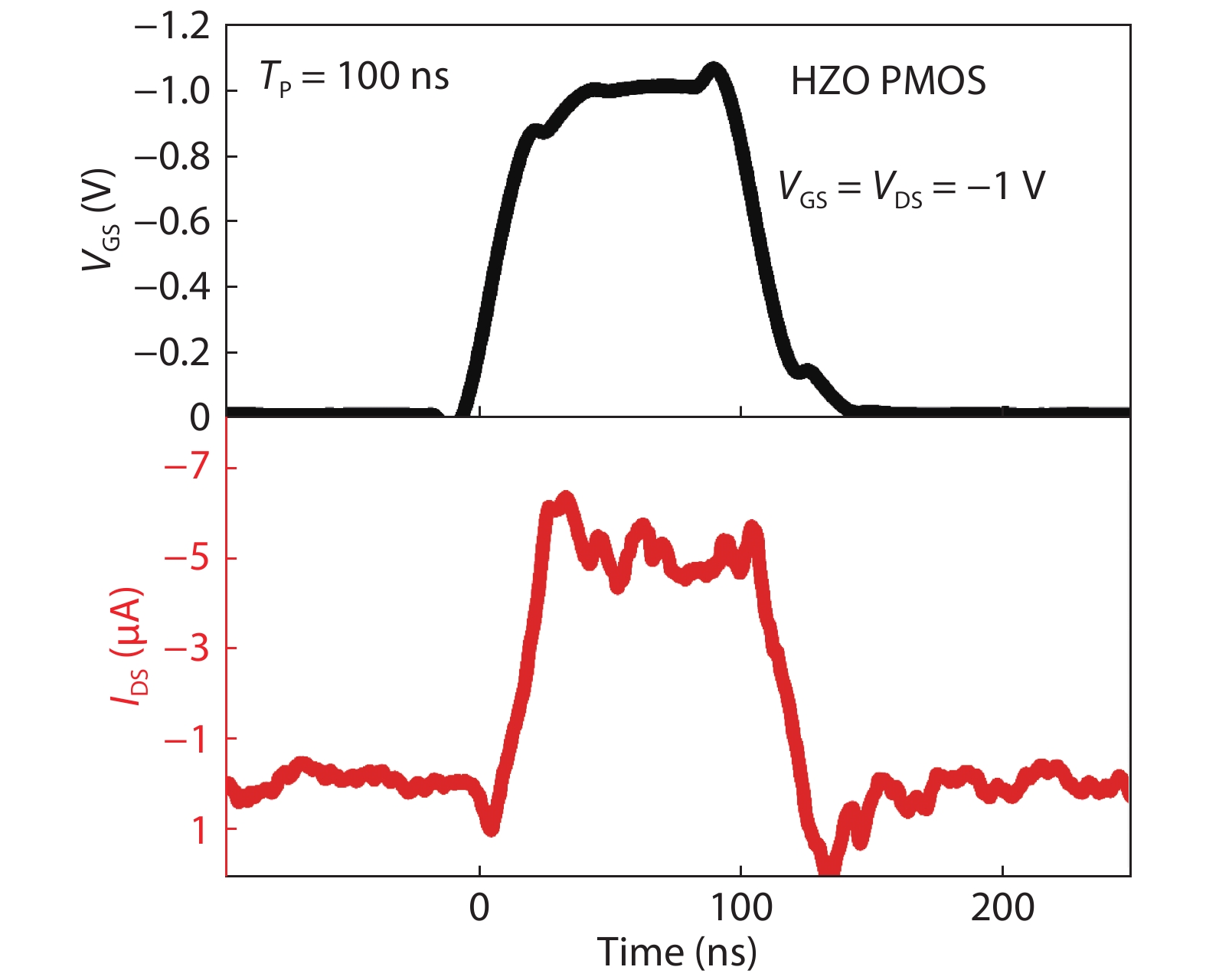

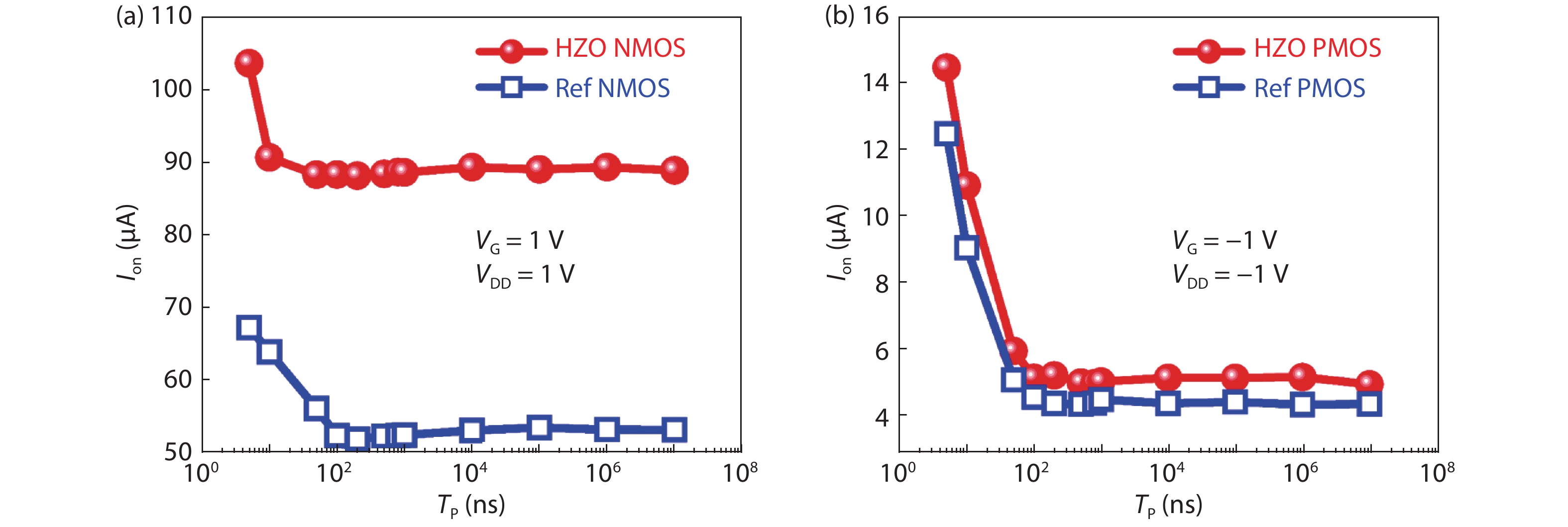

The HfO2-based ferroelectric field effect transistors (FeFET) have been widely studied for their ability in breaking the Boltzmann limit and the potential to be applied to low-power circuits. This article systematically investigates the transient response of negative capacitance (NC) fin field-effect transistors (FinFETs) through two kinds of self-built test schemes. By comparing the results with those of conventional FinFETs, we experimentally demonstrate that the on-current of the NC FinFET is not degraded in the MHz frequency domain. Further test results in the higher frequency domain show that the on-state current of the prepared NC FinFET increases with the decreasing gate pulse width at pulse widths below 100 ns and is consistently greater (about 80% with NC NMOS) than the on-state current of the conventional transistor, indicating the great potential of the NC FET for future high-frequency applications.-

Keywords:

- transient response,

- pulse train,

- NC FET,

- measurement,

- charge trapping

-

References

[1] Salahuddin S, Datta S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett, 2008, 8, 405 doi: 10.1021/nl071804g[2] Rusu A, Salvatore G A, Jiménez D, et al. Metal-ferroelectric-meta-oxide-semiconductor field effect transistor with sub-60mV/decade subthreshold swing and internal voltage amplification. 2010 Int Electron Devices Meet, 2010, 16.3.1[3] Zhou J R, Han G Q, Xu N, et al. Experimental validation of depolarization field produced voltage gains in negative capacitance field-effect transistors. IEEE Trans Electron Devices, 2019, 66, 4419 doi: 10.1109/TED.2019.2931402[4] Huang Q Q, Wang H M, Zhao Y, et al. New understanding of negative capacitance devices for low-power logic applications. 2019 China Semiconductor Technology International Conference (CSTIC), 2019, 1[5] Zhang Y J, Wang H Y, Zhang L, et al. Field-effect transistor memories based on ferroelectric polymers. J Semicond, 2017, 38, 111001 doi: 10.1088/1674-4926/38/11/111001[6] Xu H F. Two dimensional analytical model for a negative capacitance double gate tunnel field effect transistor with ferroelectric gate dielectric. J Semicond, 2018, 39, 104004 doi: 10.1088/1674-4926/39/10/104004[7] Zhang Z H, Xu G B, Zhang Q Z, et al. FinFET with improved subthreshold swing and drain current using 3-nm ferroelectric Hf0.5Zr0.5O2. IEEE Electron Device Lett, 2019, 40, 367 doi: 10.1109/LED.2019.2891364[8] Zhou J R, Han G Q, Li Q L, et al. Ferroelectric HfZrOx Ge and GeSn PMOSFETs with sub-60 mV/decade subthreshold swing, negligible hysteresis, and improved Ids. 2016 IEEE Int Electron Devices Meet IEDM, 2016, 12.2.1[9] Cai Y W, Zhang Q Z, Zhang Z H, et al. Endurance characteristics of negative capacitance FinFETs with negligible hysteresis. IEEE Electron Device Lett, 2021, 42, 260 doi: 10.1109/LED.2020.3048349[10] Li Y X, Liang R R, Wang J B, et al. Negative capacitance oxide thin-film transistor with sub-60 mV/decade subthreshold swing. IEEE Electron Device Lett, 2019, 40, 826 doi: 10.1109/LED.2019.2907988[11] Wang J L, Wang D, Li Q, et al. Excellent ferroelectric properties of Hf0.5Zr0.5O2 thin films induced by Al2O3 dielectric layer. IEEE Electron Device Lett, 2019, 40, 1937 doi: 10.1109/LED.2019.2950916[12] Liao J J, Zeng B J, Sun Q, et al. Grain size engineering of ferroelectric Zr-doped HfO2 for the highly scaled devices applications. IEEE Electron Device Lett, 2019, 40, 1868 doi: 10.1109/LED.2019.2944491[13] Tsai M J, Chen P J, Peng P Y, et al. Atomic-level Analysis by synchrotron radiation and characterization of 2 nm, 3 nm, and 5 nm-thick Hf0.5Zr0.5O2 negative capacitance FinFET. 2019 Silicon Nanoelectronics Workshop (SNW), 2019, 1[14] Nowak E J, Aller I, Ludwig T, et al. Turning silicon on its edge [double gate CMOS/FinFET technology]. IEEE Circuits Devices Mag, 2004, 20, 20 doi: 10.1109/MCD.2004.1263404[15] Suh D, Fossum J G. A physical charge-based model for non-fully depleted SOI MOSFET's and its use in assessing floating-body effects in SOI CMOS circuits. IEEE Trans Electron Devices, 1995, 42, 728 doi: 10.1109/16.372078[16] Kerber M A. Methodology for electrical characterization of MOS devices with alternative gate dielectrics. PhD Thesis, Tech. University Darmstadt, 2003[17] Chatterjee K, Rosner A J, Salahuddin S. Intrinsic speed limit of negative capacitance transistors. IEEE Electron Device Lett, 2017, 38, 1328 doi: 10.1109/LED.2017.2731343[18] Kwon D, Liao Y H, Lin Y K, et al. Response speed of negative capacitance FinFETs. 2018 IEEE Symposium on VLSI Technology, 2018, 49[19] Krivokapic Z, Rana U, Galatage R, et al. 14 nm Ferroelectric FinFET technology with steep subthreshold slope for ultra low power applications. 2017 IEEE Int Electron Devices Meet IEDM, 2017, 15.1.1[20] Li K S, Wei Y J, Chen Y J, et al. Negative-capacitance FinFET inverter, ring oscillator, SRAM cell, and ft. 2018 IEEE Int Electron Devices Meet IEDM, 2018, 31.7.1[21] Kobayashi M, Ueyama N, Jang K, et al. Experimental study on polarization-limited operation speed of negative capacitance FET with ferroelectric HfO2. 2016 IEEE Int Electron Devices Meet IEDM, 2016, 12.3.1[22] Yuan Z, Rizwan S, Wong M, et al. Switching-speed limitations of ferroelectric negative-capacitance FETs. IEEE Trans Electron Devices, 2016, 63, 4046 doi: 10.1109/TED.2016.2602209[23] Zhou J R, Wu J B, Han G Q, et al. Frequency dependence of performance in Ge negative capacitance PFETs achieving sub-30 mV/decade swing and 110 mV hysteresis at MHz. 2017 IEEE Int Electron Devices Meet IEDM, 2017, 15.5.1[24] B1542A 10 ns Pulsed IV Parametric Test Solution, Keysight, Santa Rosa, CA, USA[25] Instruments 4225-PMU Ultrafast-Fast I-V Module, Keithley, Cleveland, OH, USA[26] B1530A Waveform Generator/Fast Measurement Unit, Keysight, Santa Rosa, CA, USA[27] Yu X, Chen B, Cheng R, et al. Fast-trap characterization in Ge CMOS using sub-1 ns ultra-fast measurement system. 2016 IEEE International Electron Devices Meeting (IEDM), 2016, 31.3.1[28] Wong J C, Salahuddin S. Negative capacitance transistors. Proc IEEE, 2019, 107, 49 doi: 10.1109/JPROC.2018.2884518 -

Proportional views

DownLoad:

DownLoad: