| Citation: |

Bo Zhang, Wentong Zhang, Ming Qiao, Zhenya Zhan, Zhaoji Li. Concept and design of super junction devices[J]. Journal of Semiconductors, 2018, 39(2): 021001. doi: 10.1088/1674-4926/39/2/021001

B Zhang, W T Zhang, M Qiao, Z Y Zhan, Z J Li. Concept and design of super junction devices[J]. J. Semicond., 2018, 39(2): 021001. doi: 10.1088/1674-4926/39/2/021001.

Export: BibTex EndNote

|

-

Abstract

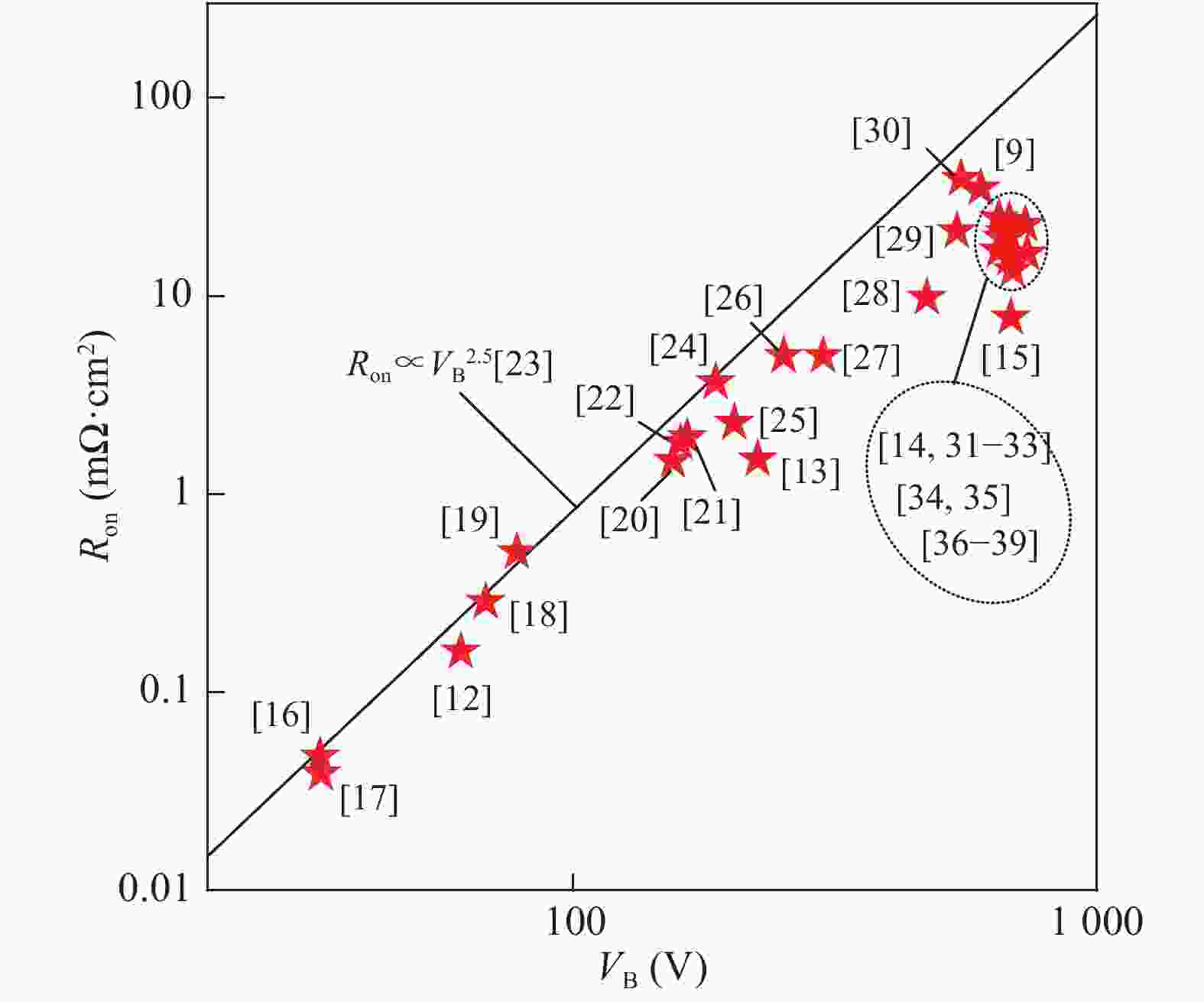

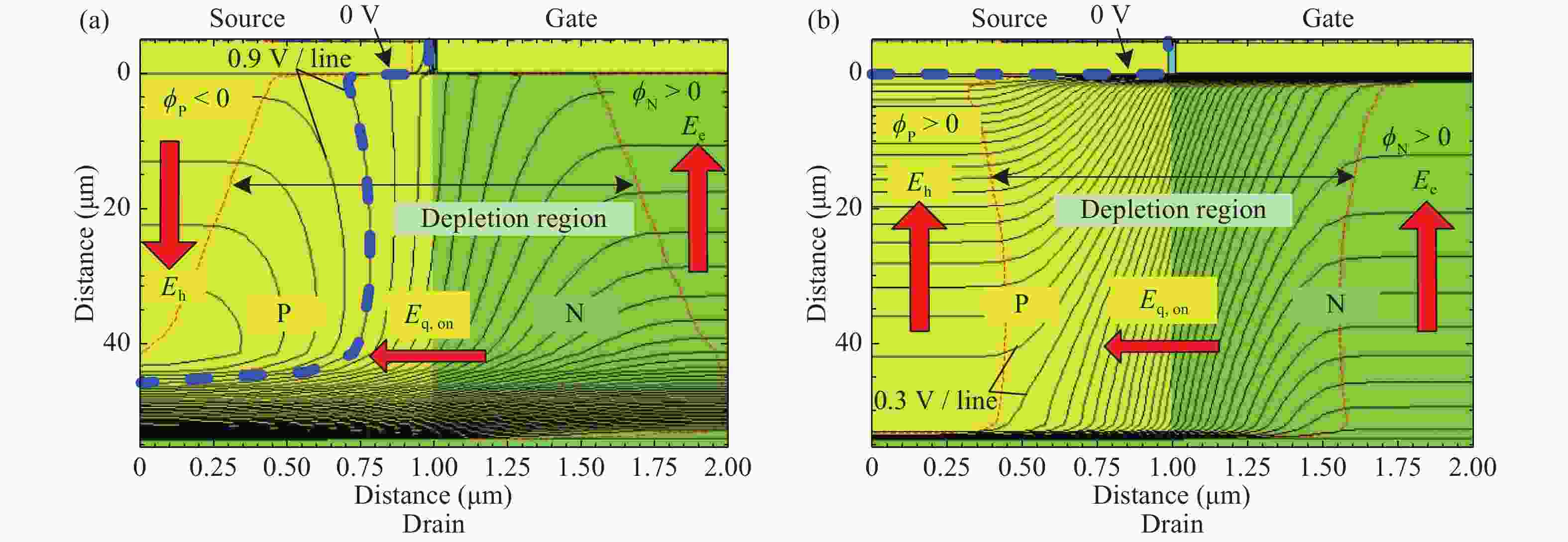

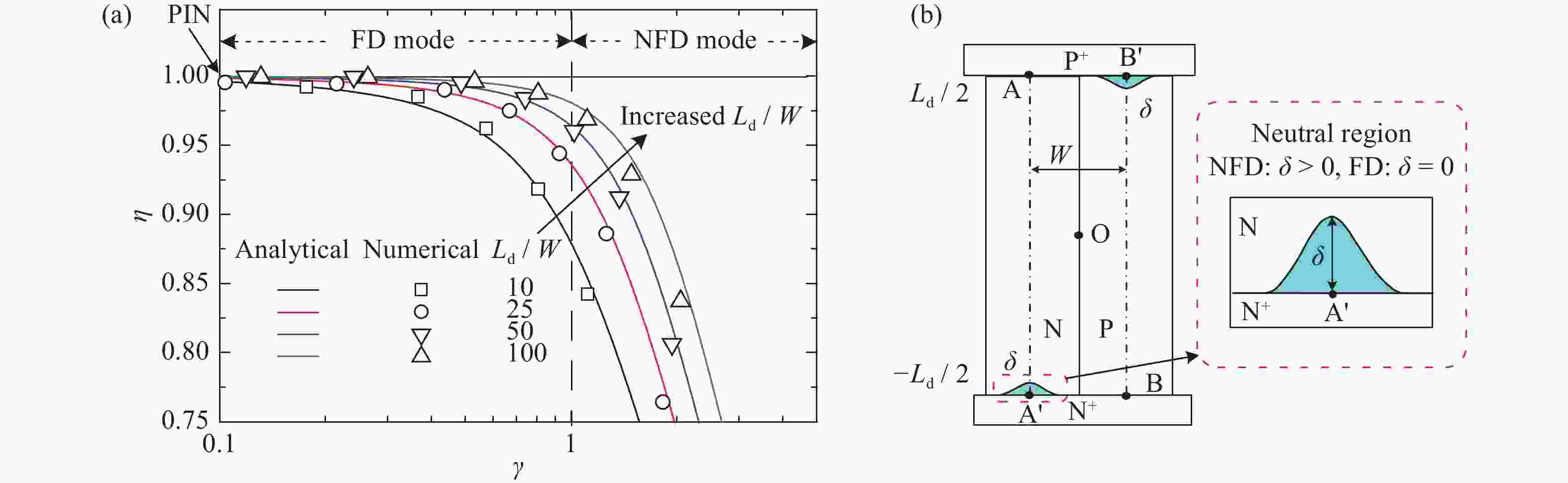

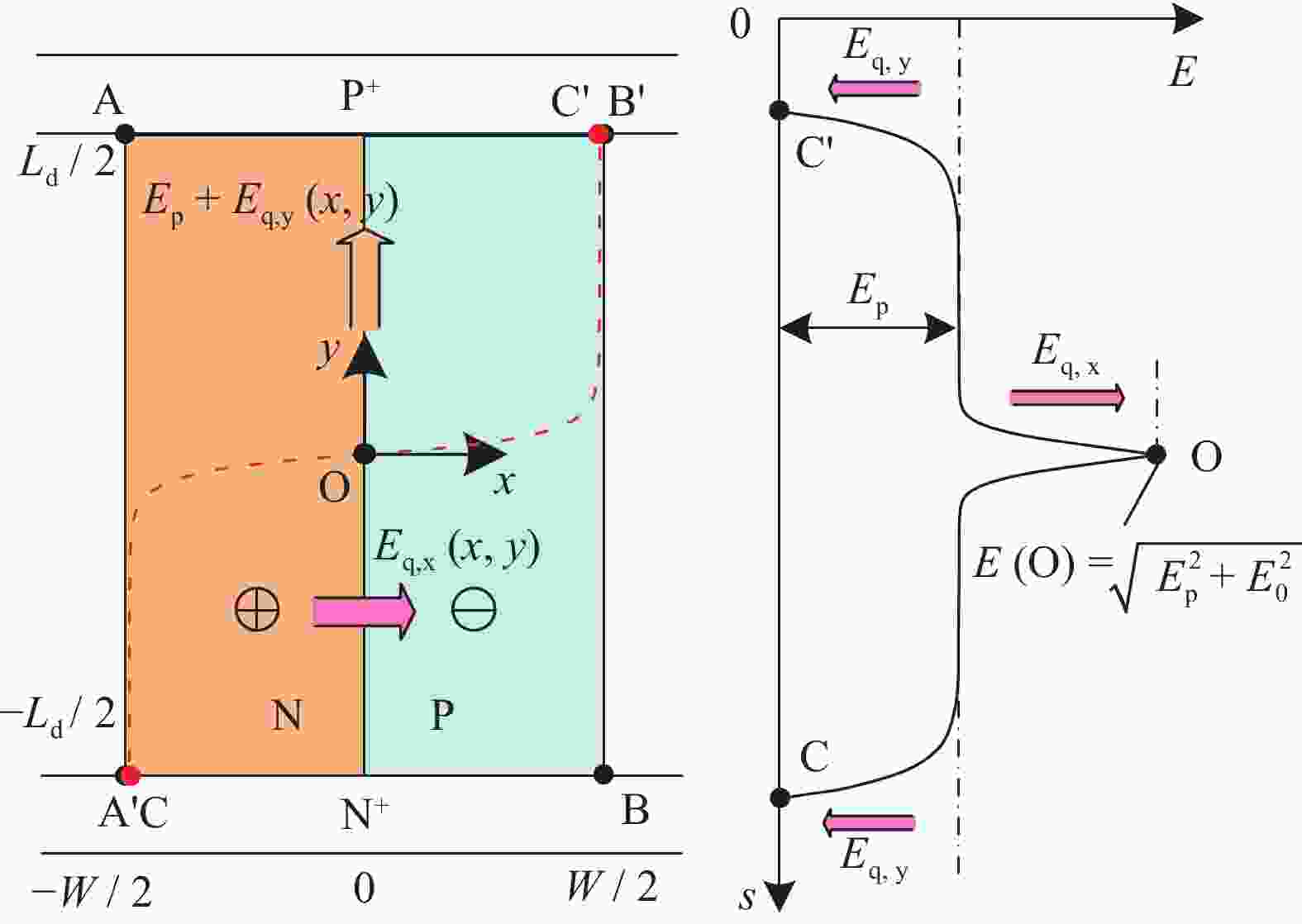

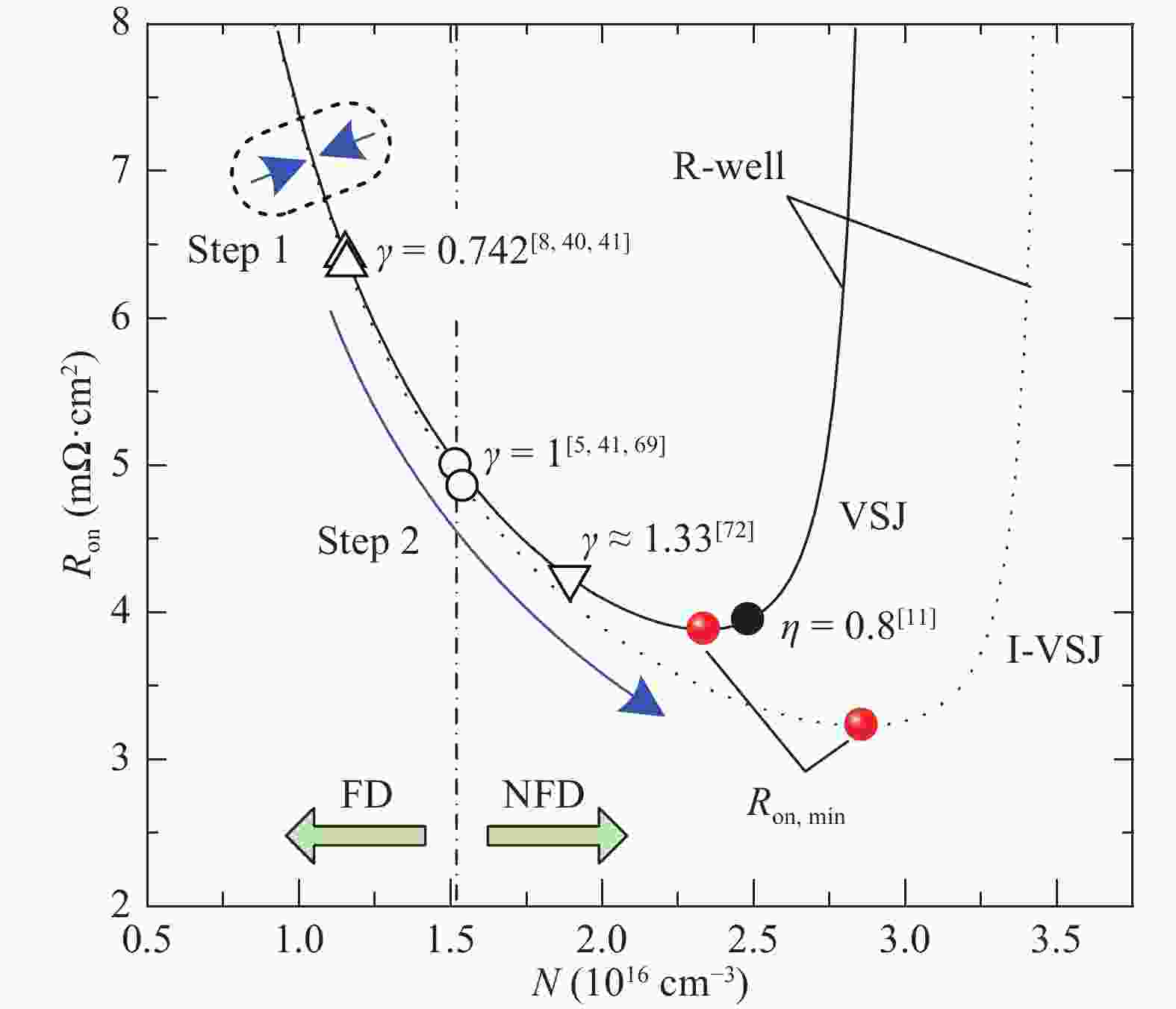

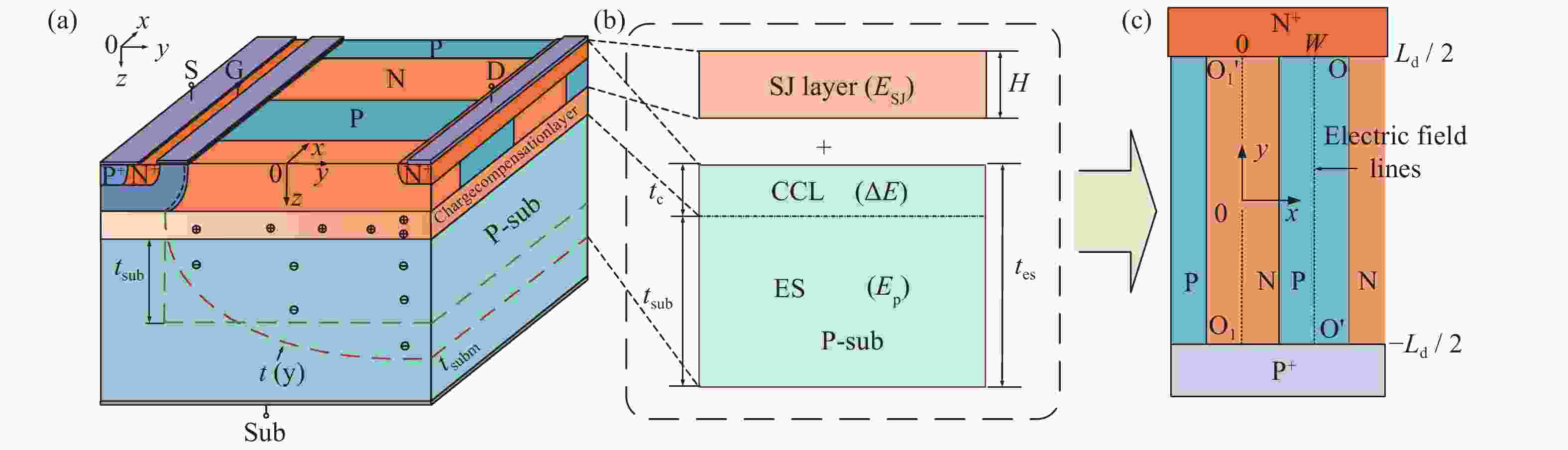

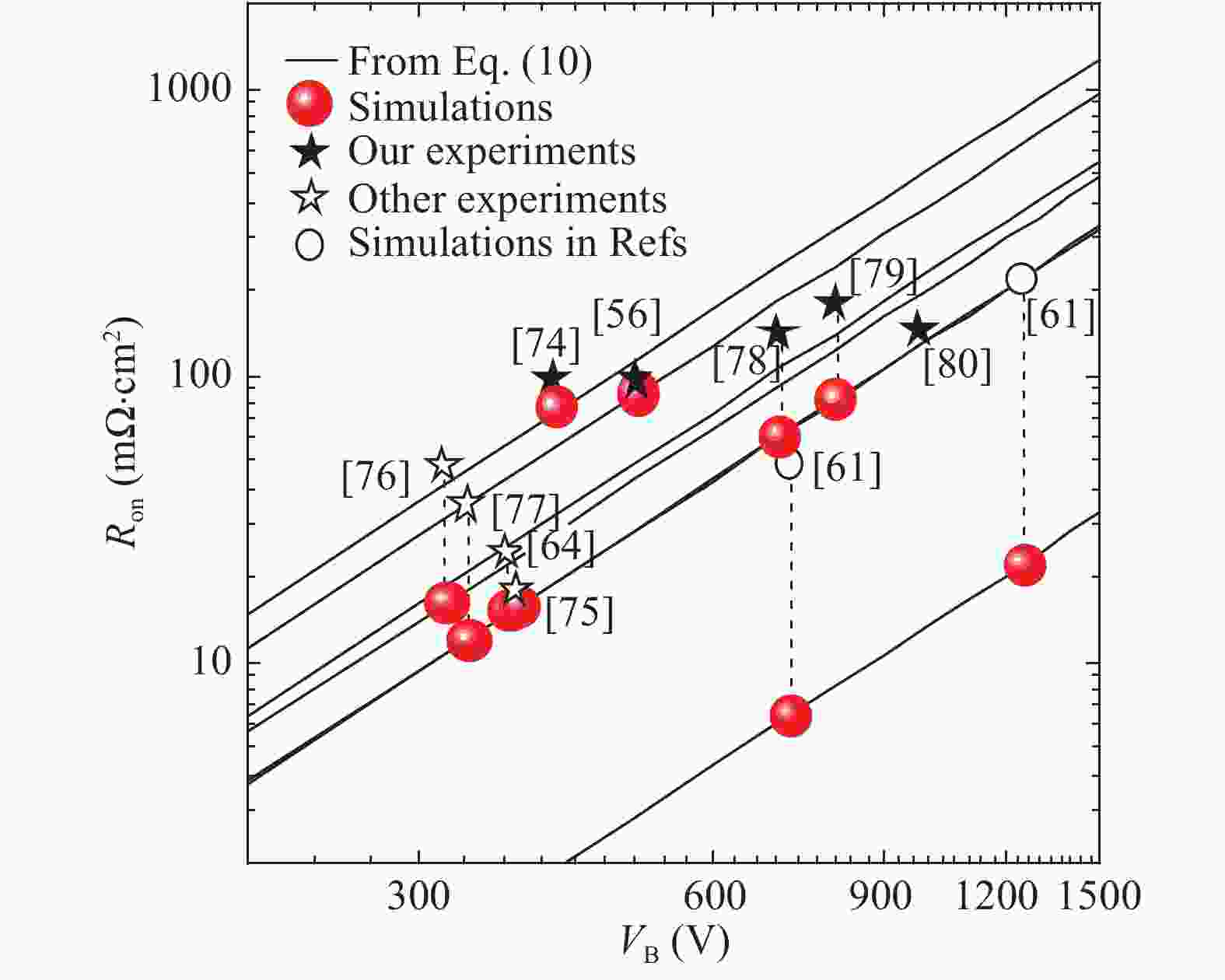

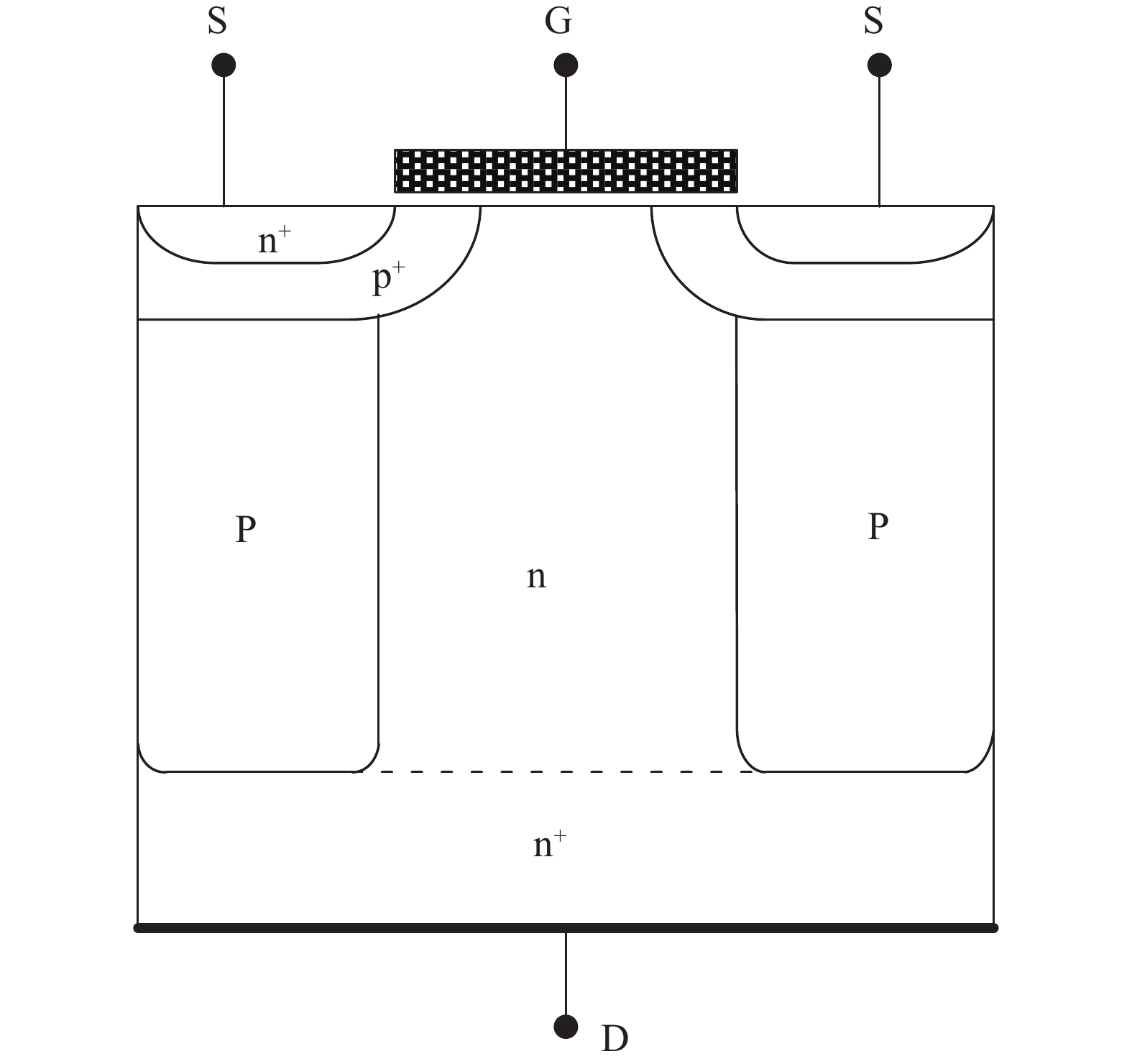

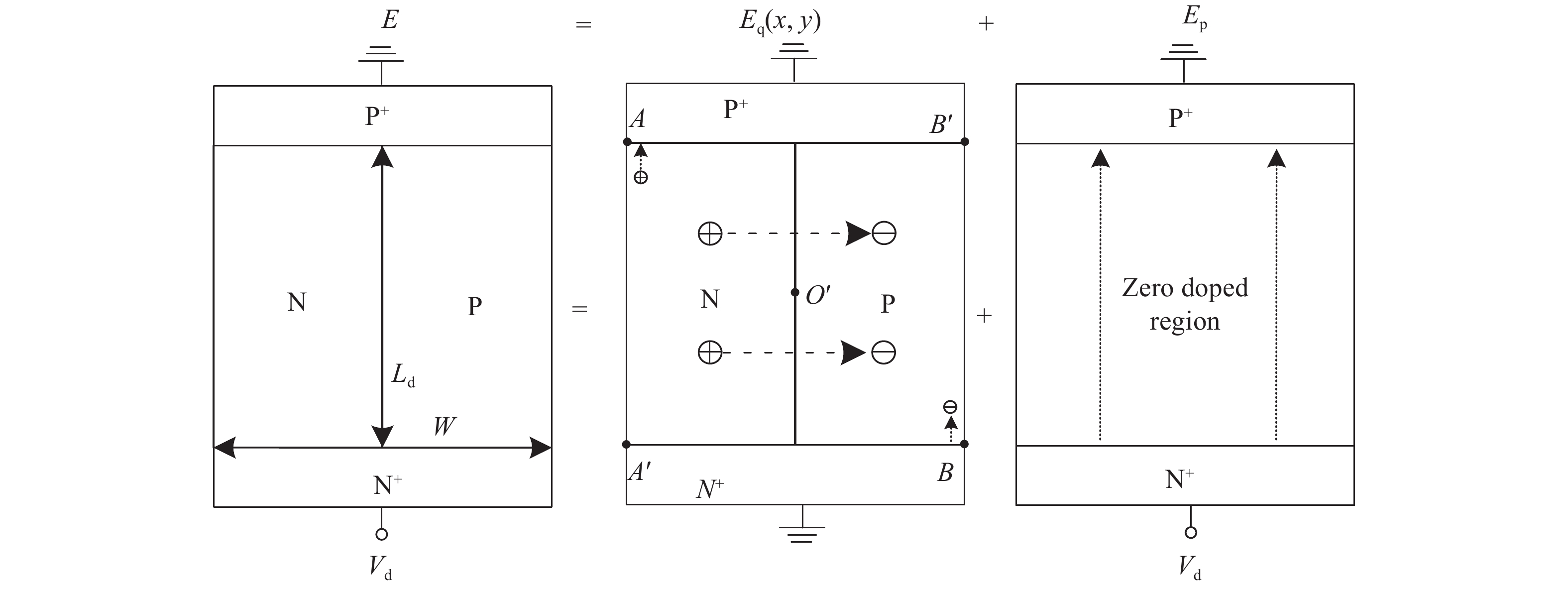

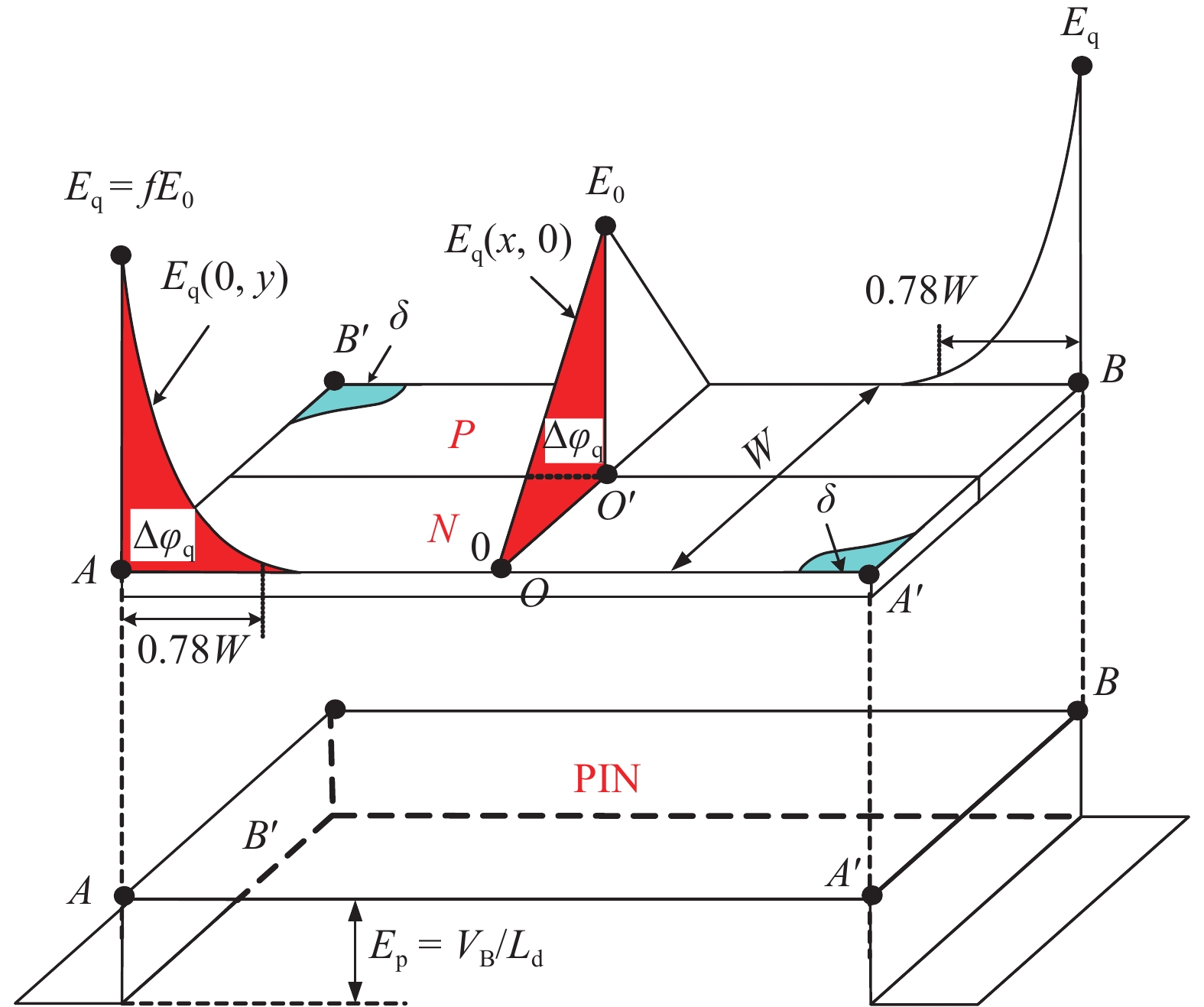

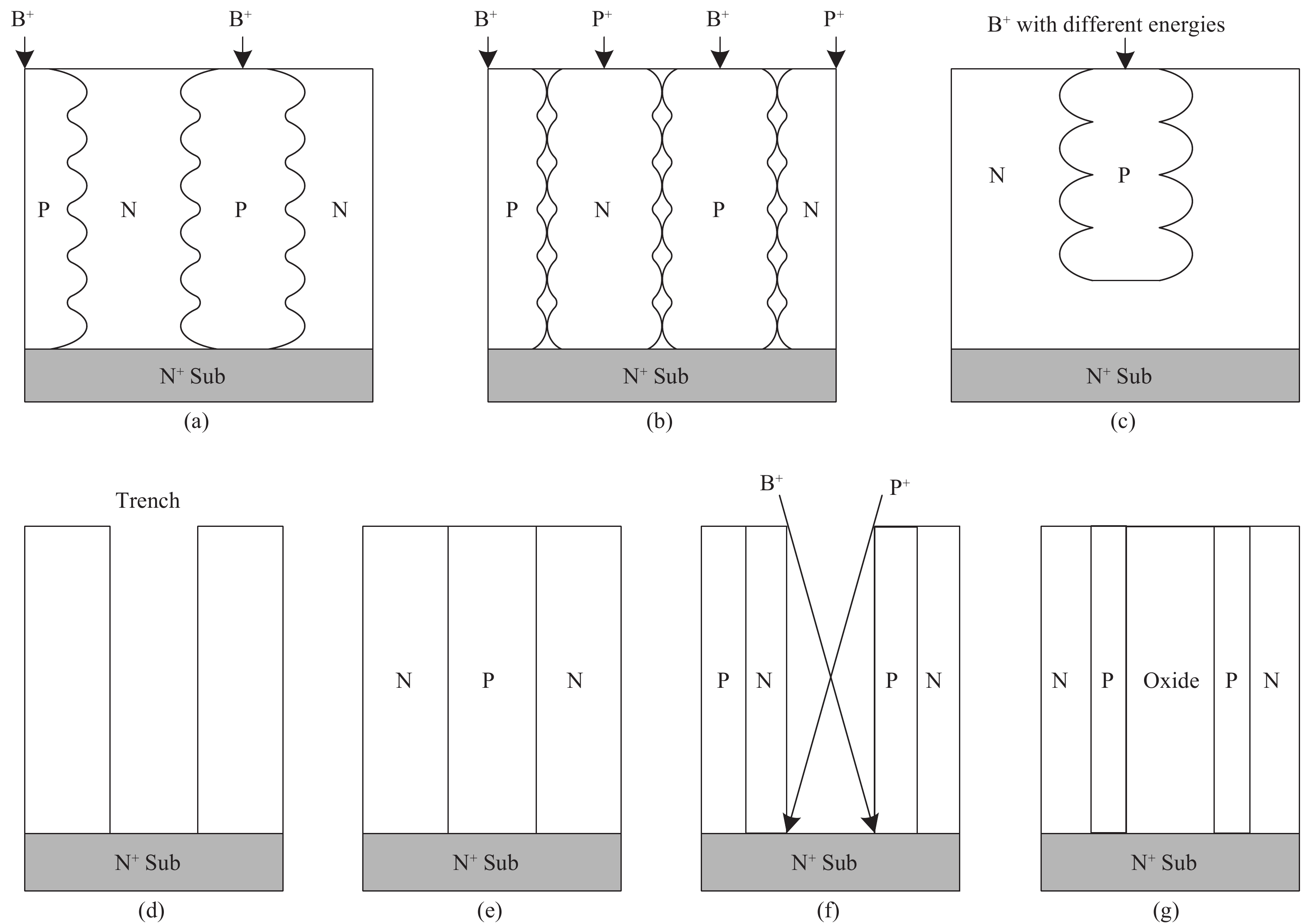

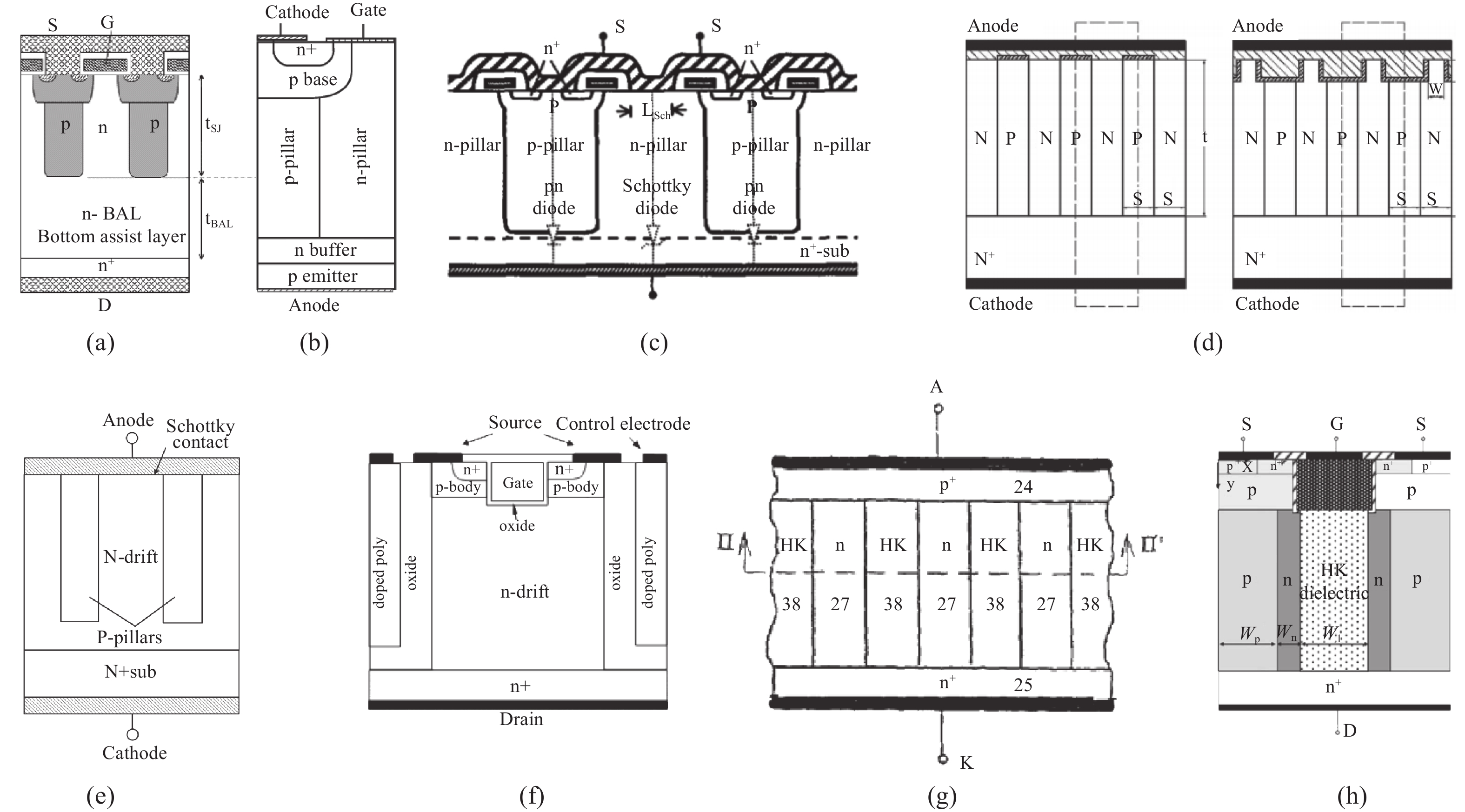

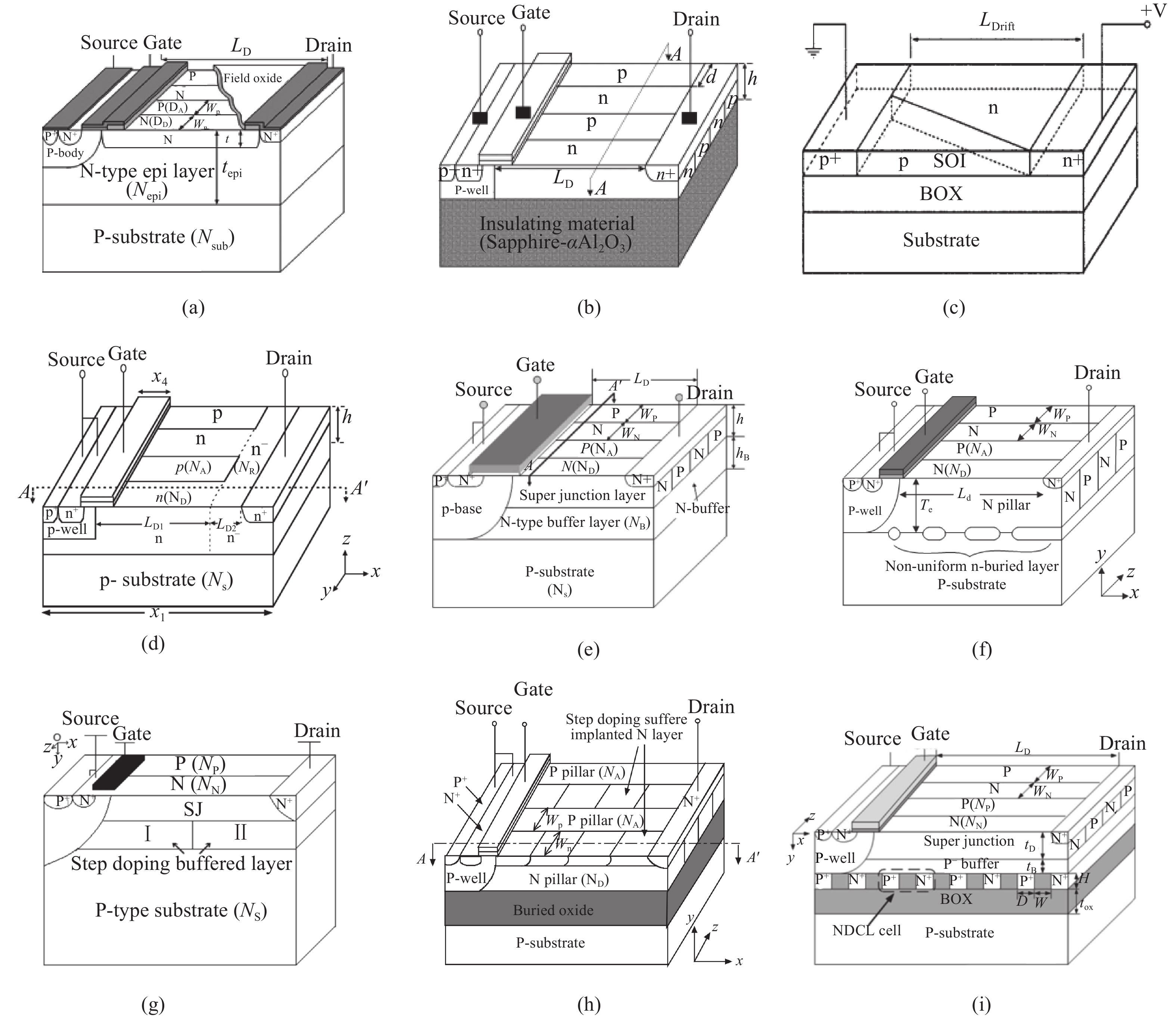

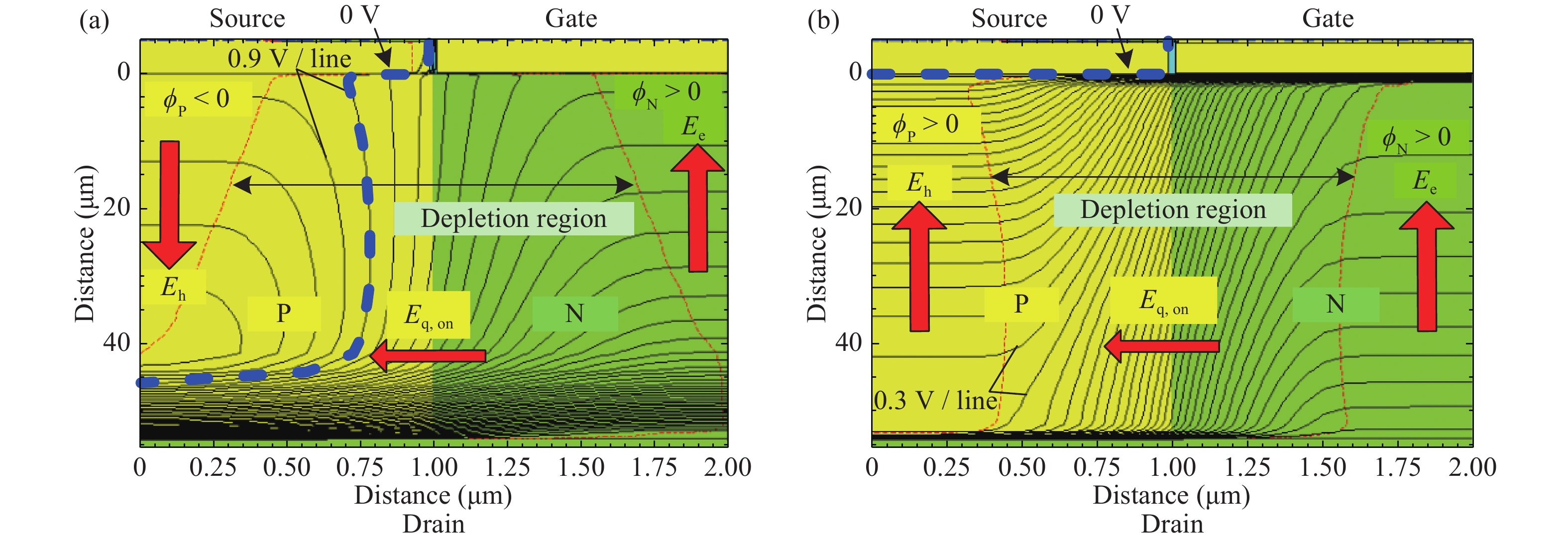

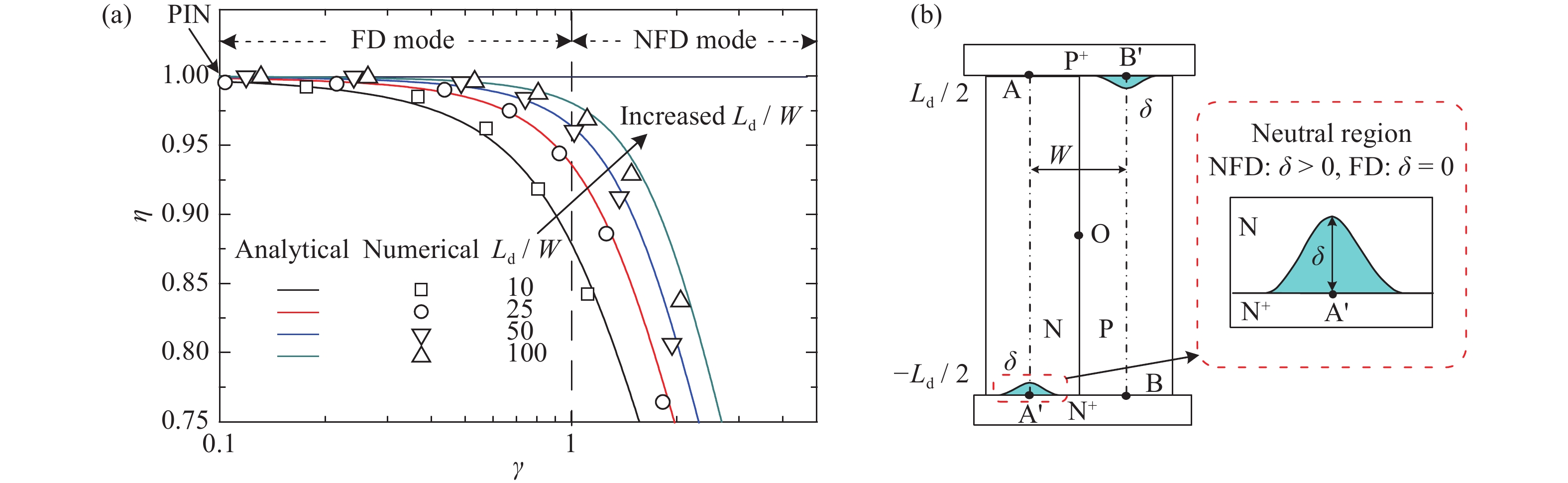

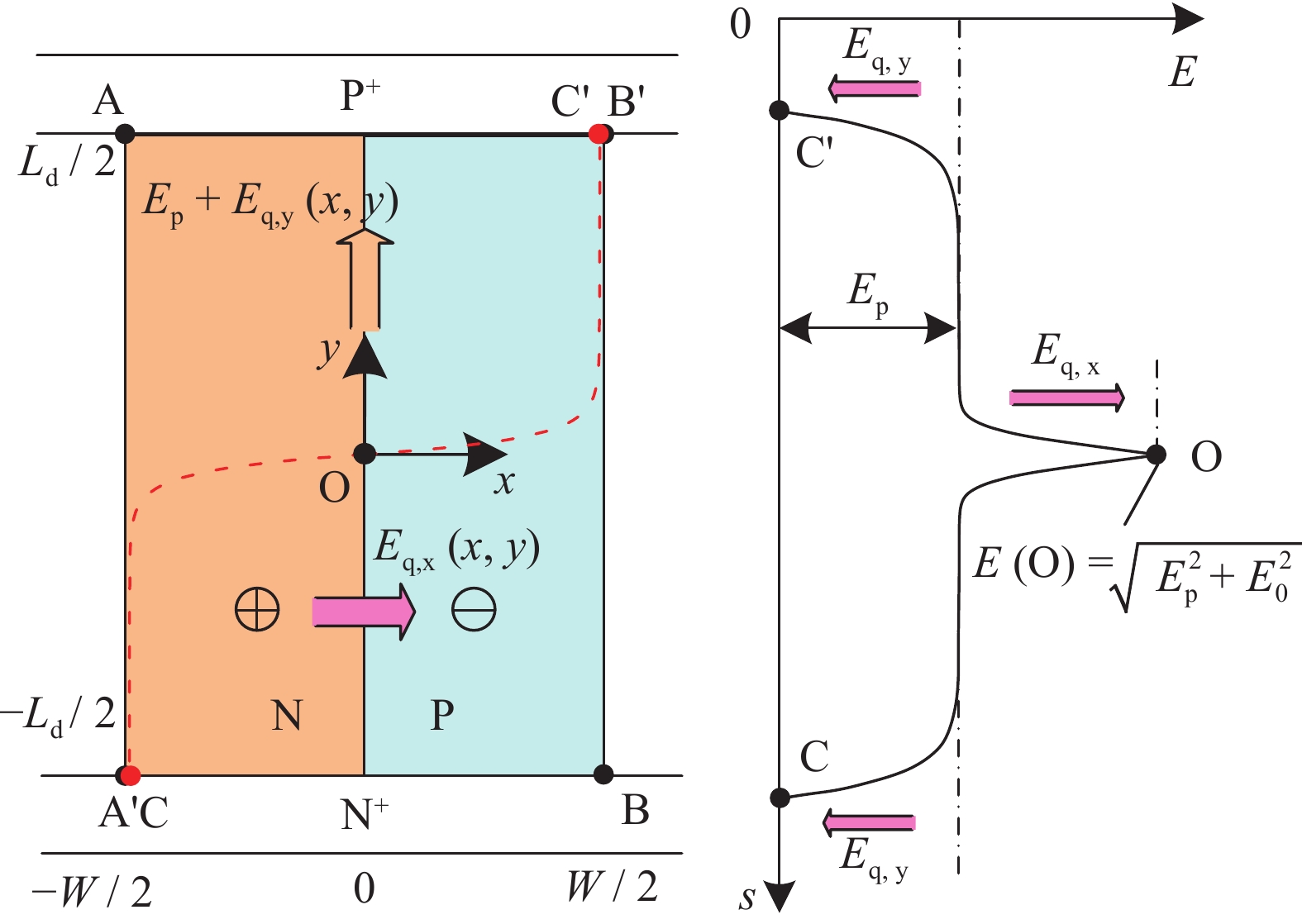

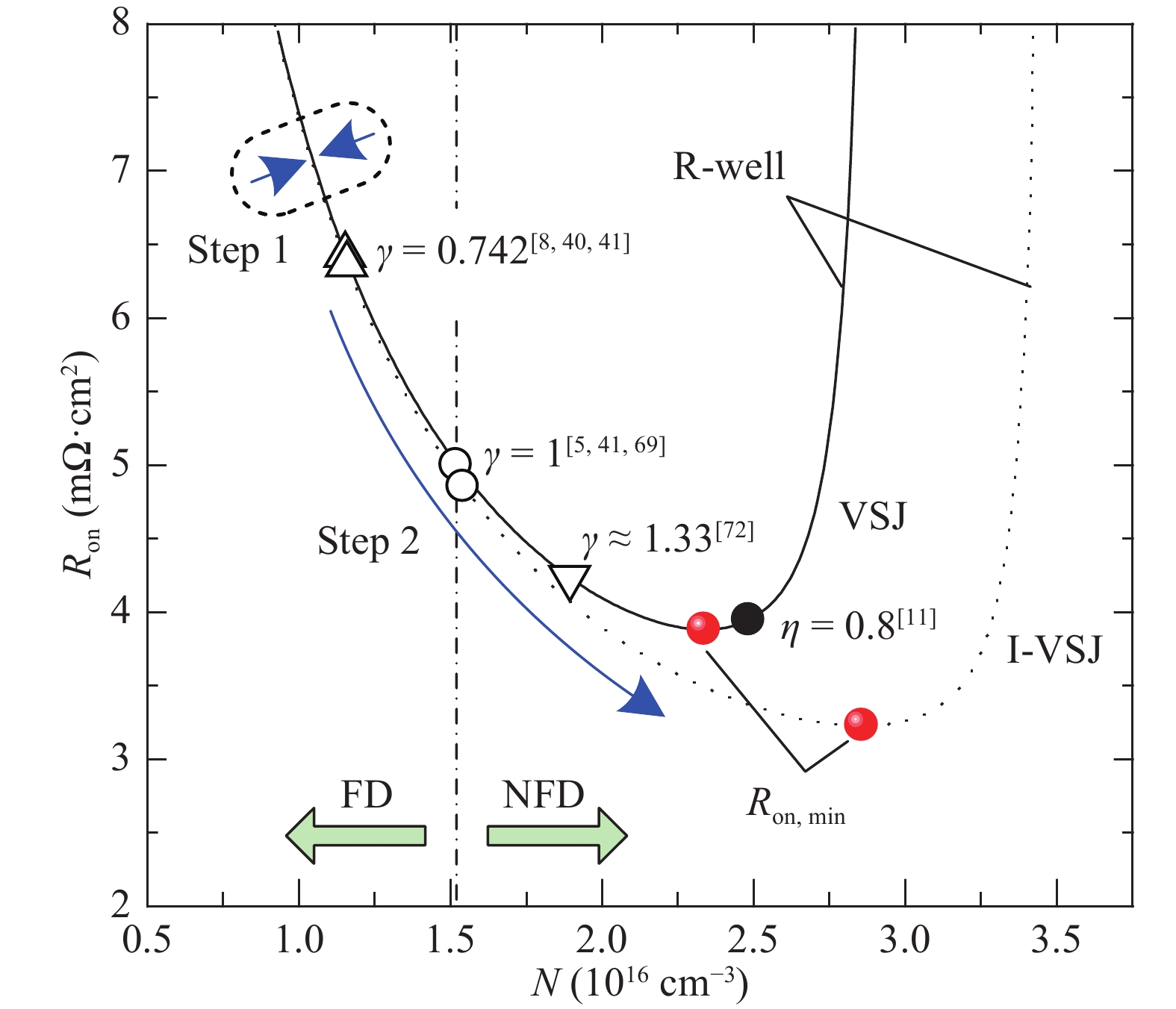

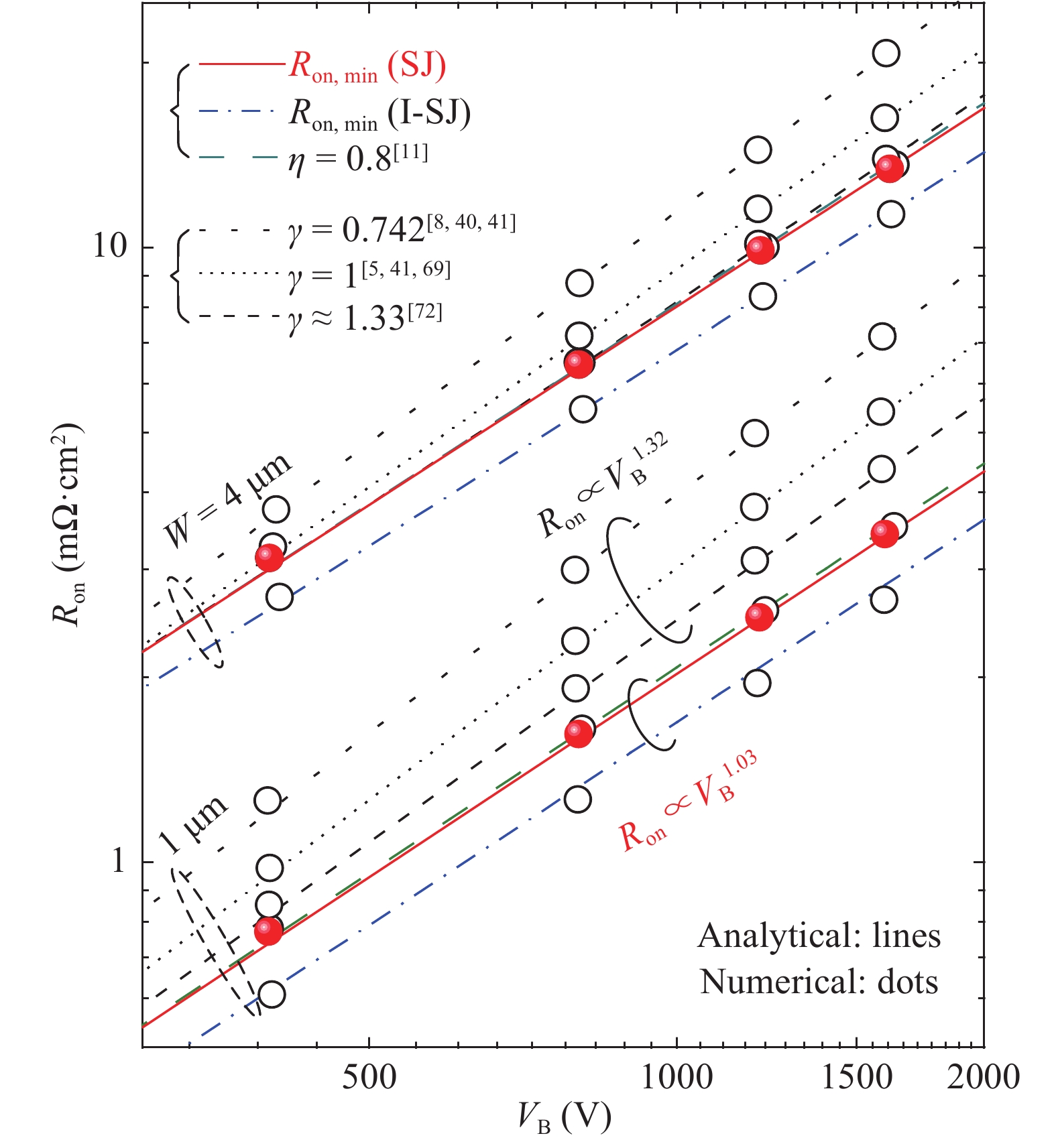

The super junction (SJ) has been recognized as the " milestone” of the power MOSFET, which is the most important innovation concept of the voltage-sustaining layer (VSL). The basic structure of the SJ is a typical junction-type VSL (J-VSL) with the periodic N and P regions. However, the conventional VSL is a typical resistance-type VSL (R-VSL) with only an N or P region. It is a qualitative change of the VSL from the R-VSL to the J-VSL, introducing the bulk depletion to increase the doping concentration and optimize the bulk electric field of the SJ. This paper firstly summarizes the development of the SJ, and then the optimization theory of the SJ is discussed for both the vertical and the lateral devices, including the non-full depletion mode, the minimum specific on-resistance optimization method and the equivalent substrate model. The SJ concept breaks the conventional " silicon limit” relationship of Ron∝VB2.5, showing a quasi-linear relationship of Ron∝VB1.03. -

References

[1] Zhang B, Zhang W T, Qiao M, et al. Theory and optimization of the power super junction device. Sci Sin-Phys Mech Astron, 2016, 46: 107302 (in Chinese)[2] Zhang B, Luo X R, Li Z J. Electric field optimization technology for power semiconductor devices. Chengdu: UESTC Press, 2016 (in Chinese)[3] Chen X B. Superjunction device. Power Electron, 2008, 42(12): 2 (in Chinese)[4] Chen X B. Semiconductor power devices with alternating conductivity type high-voltage breakdown region. US Patient, US5216275, 1993[5] Chen X B, Mawby P A, Board K, et al. Theory of a novel voltage-sustaining layer for power devices. Microelectron J, 1998, 29(12): 1005 doi: 10.1016/S0026-2692(98)00065-2[6] Coe D J. High voltage semiconductor device. USA Patent, US4754310, 1988[7] Tihanyi J. Power MOSFET. USA Patent, US5438215, 1995[8] Fujihira T. Theory of semiconductor superjunction devices. Jpn J Appl Phys, 1997, 36(10): 6254[9] Deboy G, Marz M, Stengl J P, et al. A new generation of high voltage MOSFETs breaks the limit line of silicon. IEEE International Electron Devices Meeting (IEDM), 1998: 683[10] Lorenz L, Deboy G, Knapp A, et al. CooLMOSTM: a new milestone in high voltage power MOS. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 1999: 3[11] Zhang W T, Zhang B. Theory of superjunction with NFD and FD modes based on normalized breakdown voltage. IEEE Trans Electron Devices, 2015, 62(12): 4114 doi: 10.1109/TED.2015.2491360[12] Kawashima Y, Inomata H, Murakawa K, et al. Narrow-pitch n-channel superjunction UMOSFET for 40–60 V automotive application. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2010: 329[13] Yamauchi S, Shibata T, Nogami S, et al. 200 V super junction MOSFET fabricated by high aspect ratio trench filling. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2006: 1[14] Saito W, Omura I, Aida S, et al. A 15.5 mΩ·cm2 680 V superjunction MOSFET reduced on-resistance by lateral pitch narrowing. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2006: 1[15] Sakakibara J, Noda Y, Shibata T, et al. 600 V-class super junction MOSFET with high aspect ratio P/N columns structure. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2008: 299[16] Rutter P, Peake S T. Low voltage trenchMOS combining low specific RDS (on) and QG FOM. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2010: 325[17] Okubo H, Kobayashi K, Kawashima Y. Ultralow on-resistance 30–40 V UMOSFET by 2-D scaling of ion-implanted superjunction structure. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2013: 87[18] Miura Y, Ninomiya H, Kobayashi K. High performance superjunction UMOSFETs with split P-columns fabricated by multi-ion-implantations. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2005: 39[19] Ninomiya H, Miura Y, Kobayashi K. Ultra-low on-resistance 60–100 V superjunction UMOSFETs fabricated by multiple ion-implantation. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2004: 177[20] Dalen R, Rochefort C. Electrical characterisation of vertical vapor phase doped (VPD) RESURF MOSFETs. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2004: 451[21] Dalen R, Rochefort C. Vertical multi-RESURF MOSFETs exhibiting record low specific resistance. IEEE International Electron Devices Meeting (IEDM), 2003: 31.1.1[22] Rochefort C, Dalen R. Vertical RESURF diodes manufactured by deep-trench etch and vapor-phase doping. IEEE Electron Device Lett, 2004, 25(2): 73 doi: 10.1109/LED.2003.822649[23] Hu C M. Optimum doping profile for minimum ohmic resistance and high-breakdown voltage. IEEE Trans Electron Devices, 1979, 26(3): 243 doi: 10.1109/T-ED.1979.19416[24] Gan K P, Yang X, Liang Y C, et al. A simple technology for superjunction device fabrication: polyflanked VDMOSFET. IEEE Electron Device Letters, 2002, 23(10): 627 doi: 10.1109/LED.2002.803770[25] Hattori Y, Nakashima K, Kuwahara M, et al. Design of a 200 V super junction MOSFET with n-buffer regions and its fabrication by trench filling. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2004: 189[26] Kurosaki T, Shishido H, Kitada M, et al. 200 V multi RESURF trench MOSFET (MR-TMOS). IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2003: 211[27] Nitta T, Minato T, Yano M, et al. Experimental results and simulation analysis of 250 V super trench power MOSFET (STM). IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2000: 77[28] Rochefort C, Dalen R. A scalable trench etch based process for high voltage vertical RESURF MOSFETs. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2005: 35[29] Iwamoto S, Takahashi K, Kuribayashi H, et al. Above 500 V class superjunction MOSFETs fabricated by deep trench etching and epitaxial growth. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2005: 31[30] Rüb M, Bär M, Deboy G, et al. 550 V superjunction 3.9 Ω·mm2 transistor formed by 25 MeV masked boron implantation. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2004: 455[31] Lee SC, Oh K H, Kim S S, et al. 650 V superjunction MOSFET using universal charge balance concept through drift region. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2014: 83[32] Onishi Y, Iwamoto S, Sato T, et al. 24 mΩ·cm2 680 V silicon superjunction MOSFET. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2002: 241[33] Saito W, Omura L, Aida S, et al. A 20 mΩ·cm2 600 V-class superjunction MOSFET. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2004: 459[34] Takahashi K, Kuribayashi H, Kawashima T, et al. 20 mΩ·cm2 660 V super junction MOSFETs fabricated by deep trench etching and epitaxial growth. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2006: 1[35] Moens P, Bogman F, Ziad H, et al. UltiMOS: a local charge-balanced trench-based 600 V super-junction device. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2011: 304[36] Sugi A, Takei M, Takahashi K, et al. Super junction MOSFETs above 600 V with parallel gate structure fabricated by deep trench etching and epitaxial growth. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2008: 165[37] Tamaki T, Nakazawa Y, Kanai H, et al. Vertical charge imbalance effect on 600 V-class trench-filling superjunction power MOSFETs. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2011: 308[38] Kagata Y, Oda Y, Hayashi K, et al. 600 V-class trench-filling super junction power MOSFETs for low loss and low leakage current. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2013: 225[39] Jung E S, Kyoung S S, Kang E G. Design and fabrication of super junction MOSFET based on trench filling and bottom implantation process. J Electr Eng Technol, 2014, 9(3): 964 doi: 10.5370/JEET.2014.9.3.964[40] Shenoy P M, Bhalla A, Dolny G. Analysis of the effect of charge imbalance on the static and dynamic characteristics of the super junction MOSFET. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 1999: 99[41] Chen X B, Sin J K O. Optimization of the specific on-resistance of the COOLMOSTM. IEEE Trans Electron Devices, 2001, 48(2): 344 doi: 10.1109/16.902737[42] Buzzo M, Rub M, Ciappa M, et al. Characterization of 2D dopant profiles for the design of proton implanted high-voltage super junction. International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), 2005: 285[43] Saito W, Omura I, Aida S, et al. A 15.5 mΩ·cm2 680 V superjunction MOSFET reduced on-resistance by lateral pitch narrowing. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2006: 1[44] Onishi Y, Iwamoto S, Sato T, et al. 24 mΩ·cm2 680 V silicon superjunction MOSFET. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2002: 241[45] Saito W, Omura L, Aida S, et al. A 20 mΩ·cm2 600 V-class superjunction MOSFET. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2004: 459[46] Minato T, Nitta T, Uenisi A, et al. Which is cooler, trench or multi-epitaxy cutting edge approach for the silicon limit by the super trench power MOS-FET (STM). IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2000: 73[47] Saito W, Omura I, Aida S, et al. Over 1000 V semi-superjunction MOSFET with ultra-low on-resistance blow the Si-limit. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2005: 27[48] Saito W, Omura I, Aida S, et al. Semisuperjunction MOSFETs: new design concept for lower on-resistance and softer reverse-recovery body diode. IEEE Trans Electron Devices, 2003, 50(8): 1801 doi: 10.1109/TED.2003.815126[49] Chen W J, Zhang B, Li Z J, et al. Optimum design of PSJ for high-voltage devices. Chin J Electron, 2006, 27(6): 1089[50] Antoniou M, Udrea F, Bauer F. The superjunction insulated gate bipolar transistor optimization and modeling. IEEE Trans Electron Devices, 2010, 57(3): 594 doi: 10.1109/TED.2009.2039260[51] Cheng X, Liu X M, Sin J K, et al. Improving the CoolMOSTM body-diode switching performance with integrated Schottky contacts. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2003: 304[52] Wang Y, Xu L K, Miao Z K. A superjunction schottky barrier diode with trench metal–oxide–semiconductor structure. IEEE Electron Device Lett, 2012, 33(12): 1744 doi: 10.1109/LED.2012.2220117[53] Chen Y , Liang Y C, Samudra G S. Design of gradient oxide-bypassed superjunction power MOSFET devices. IEEE Trans Power Electronics, 2007, 22(4): 1303 doi: 10.1109/TPEL.2007.900559[54] Chen X B. Super-junction voltage sustaining layer with alternating semiconductor and high-k dielectric regions.US Patient, US7230310, 2007[55] Luo X R, Jiang Y H, Zhou K, et al. Ultralow specific on-resistance superjunction vertical DMOS with high-k dielectric pillar. IEEE Electron Device Lett, 2012, 33(7): 1042 doi: 10.1109/LED.2012.2196969[56] Zhang B, Wang W L, Chen W J, et al. High-voltage LDMOS with charge-balanced surface low on-resistance path layer. IEEE Electron Device Lett, 2009, 30(8): 849 doi: 10.1109/LED.2009.2023541[57] Zhang B, Chen L, Wu J, et al. SLOP-LDMOS – a novel super-junction concept LDMOS and its experimental demonstration. IEEE International Conference on Communications, Circuits and Systems, 2005: 1402[58] Zhang B, Zhang W T, Li Z H, et al. Equivalent substrate model for lateral super junction device. IEEE Trans Electron Devices, 2014, 61(2): 525 doi: 10.1109/TED.2013.2295091[59] Nassif-khalil S G, Salama C A T. Super junction LDMOST in silicon-on-sapphire technology (SJ-LDMOST). IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2002: 81[60] Ng R, Udrea F, Sheng K, et al. Lateral unbalanced super junction (USJ)/3D-RESURF for high breakdown voltage on SOI. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2001: 395[61] Nassif-khalil S G, Li H Z, Salama C A T. SJ/RESURF LDMOST. IEEE Trans Electron Devices, 2004, 51(7): 1185 doi: 10.1109/TED.2004.829876[62] Park I Y, Salama C A T. CMOS compatible super junction LDMOST with N-buffer layer. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2005: 163[63] Chen W J, Zhang B, Li Z H. SJ-LDMOS with high breakdown voltage and ultra-low on-resistance. Electronics Letters, 2006, 42(22): 1314 doi: 10.1049/el:20062751[64] Duan B X, Cao Z, Yuan X N, et al. New superjunction LDMOS breaking silicon limit by electric field modulation of buffered step doping. IEEE Electron Device Letters, 2015, 36(1): 47 doi: 10.1109/LED.2014.2366298[65] Chen W J, Zhang B, Li Z J. Optimization of super-junction SOI-LDMOS with a step doping surface-implanted layer. Semicondr Sci Technol, 2007, 22(5): 464 doi: 10.1088/0268-1242/22/5/002[66] Wang W L, Zhang B, Li Z J, et al. High-voltage SOI SJ-LDMOS with a nondepletion compensation layer. IEEE Electron Device Lett, 2009, 30(1): 68 doi: 10.1109/LED.2008.2008208[67] Chen X B. Theory of the switching response of CBMOST. Chin J Electron, 2001, 10: 1[68] Zhang W T, Zhang B, Qiao M, et al. Optimization of lateral superjunction based on the minimum specific ON-resistance. IEEE Trans Electron Devices, 2016, 63(5): 1984 doi: 10.1109/TED.2016.2542263[69] Strollo A G M, Napoli E. Optimal ON-resistance versus breakdown voltage tradeoff in superjunction power devices: a novel analytical model. IEEE Trans Electron Devices, 2001, 48(9): 2161 doi: 10.1109/16.944211[70] Zhang W T, Zhang B, Qiao M, et al. Optimization and new structure of superjunction with isolator layer. IEEE Trans Electron Devices, 2017, 64(1): 217 doi: 10.1109/TED.2016.2628056[71] Zhang W T, Zhang B, Qiao M, et al. The RON,min of balanced symmetric vertical super junction based on R-well model. IEEE Trans Electron Devices, 2017, 64(1): 224 doi: 10.1109/TED.2016.2632113[72] Huang H M, Chen X B. Optimization of specific on-resistance of balanced symmetric superjunction MOSFETs based on a better approximation of ionization integral. IEEE Trans Electron Devices, 2012, 59(10): 2742 doi: 10.1109/TED.2012.2207961[73] Disney D, Dolny G. JFET depletion in superjunction devices. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2008: 160[74] Duan B X, Yang Y T, Zhang B. New superjunction LDMOS with N-type charges’ compensation layer. IEEE Electron Device Lett, 2009, 30(3): 305 doi: 10.1109/LED.2009.2012396[75] Duan B X, Cao Z, Yuan S, et al. Complete 3D-reduced surface field superjunction lateral double-diffused MOSFET breaking silicon limit. IEEE Electron Device Lett, 2015, 36(12): 1348 doi: 10.1109/LED.2015.2493080[76] Honarkhah S, Nassif-Khalil S, Salama C A T. Back-etched super-junction LDMOST on SOI. Solid-State Device Research Conference, 2004: 117[77] Lin M J, Lee T H, Chang F L, et al. Lateral superjunction reduced surface field structure for the optimization of breakdown and conduction characteristics in a high-voltage lateral double diffused metal oxide field effect transistor. Jpn J Appl Phys, 2003, 42(12): 7227[78] Qiao M, Hu X, Wen H J, et al. A novel substrate-assisted RESURF technology for small curvature radius junction. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2011: 16[79] Qiao M, Wu W J, Zhang B, et al. A novel substrate termination technology for lateral double-diffused MOSFET based on curved junction extension. Semicond Sci Technol, 2014, 29(4): 045002 doi: 10.1088/0268-1242/29/4/045002[80] Zhang W T, Zhan Z Y, Yu Y, et al. Novel superjunction LDMOS (> 950 V) with a thin layer SOI. IEEE Electron Device Lett, 2017, 38: 1555 doi: 10.1109/LED.2017.2751571[81] Kosugi R, Sakuma Y, Kojima K, et al. Development of SiC super-junction (SJ) device bydeep trench-filling epitaxial growth. Mater Sci Forum, 2013, 740-742: 785 doi: 10.4028/www.scientific.net/MSF.740-742[82] Zhong X, Wang B, Sheng K. Design and experimental demonstration of 1.35 kV SiC super junction Schottky diode. IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2016: 231[83] Li Z, Chow T P. Design and simulation of 5–20-kV GaN enhancement-mode vertical superjunction HEMT. IEEE Trans Electron Devices, 2013, 60(10): 3230 doi: 10.1109/TED.2013.2266544[84] Ishida H, Shibata D, Matsuo H, et al. GaN-based natural super junction diodes with multichannel structures. Proc Int Electron Devices Meeting (IEDM), 2008: 1 -

Proportional views

DownLoad:

DownLoad: