Achieving aluminum nitride (AlN) epilayers with dislocation densities below 107 cm−2 on sapphire remains critical for ultraviolet (UV) optoelectronics applications. However, the lattice and thermal mismatches inherent to heteroepitaxial growth hinder the simultaneous suppression of threading dislocations and surface cracking. In this work, a 10.2-μm-thick, 4-inch AlN film was fabricated on an AlN/sapphire substrate. A strain-modulated buffer was embedded beneath the AlN epilayer to pre-introduce a well-balanced compressive strain, which counteracts tensile strain accumulation during thick-layer growth while maintaining continuous two-dimensional epitaxy for effective defect suppression. This strain management strategy, combined with progressive dislocation annihilation as the layer thickness increases, yielded a surface dislocation density of 7.6 × 106 cm−2 and limited cracking to within approximately 2 mm from the wafer edge. This scalable and cost-effective approach enables the growth of crack-suppressed, high-quality AlN epilayers on sapphire, offering a practical pathway for UV optoelectronic devices in light of the current limitations of bulk AlN substrates.

- • Uncorrected proofs: articles that have been copy edited and formatted, but have not been finalized yet. They still need to be proof-read and corrected by the author(s) and the text could still change before final publication.

- • Corrected proofs: articles that contain the authors' corrections. Final citation details, e.g. volume and/or issue number, publication year and page numbers, still need to be added and the text might change before final publication.

There are two types in Press articles:

With the widespread application of artificial intelligence (AI) computing in low-temperature scenarios such as deep space and deep sea, RRAM-based edge computing has gradually attracted attention. In this paper, an adaptive reference conductance algorithm (ARCA) is proposed to improve the inference accuracy in low-temperature scenarios due to the conduction drift. The RRAM CIM chips with high read cycles are fabricated based on 28 nm CMOS logic technology, and the read times could reach 1012. By studying the influence of conductance drifting on inference accuracy in low temperature, a model of temperature and optimal reference conductance is proposed. Furthermore, by this model, adaptive selecting optimal reference conductance of analog-to-digital converters (ADCs) to quantize column current of RRAM array under different temperatures. At −40 ℃, the reference accuracy could increase from 75.43% to 86.8%.

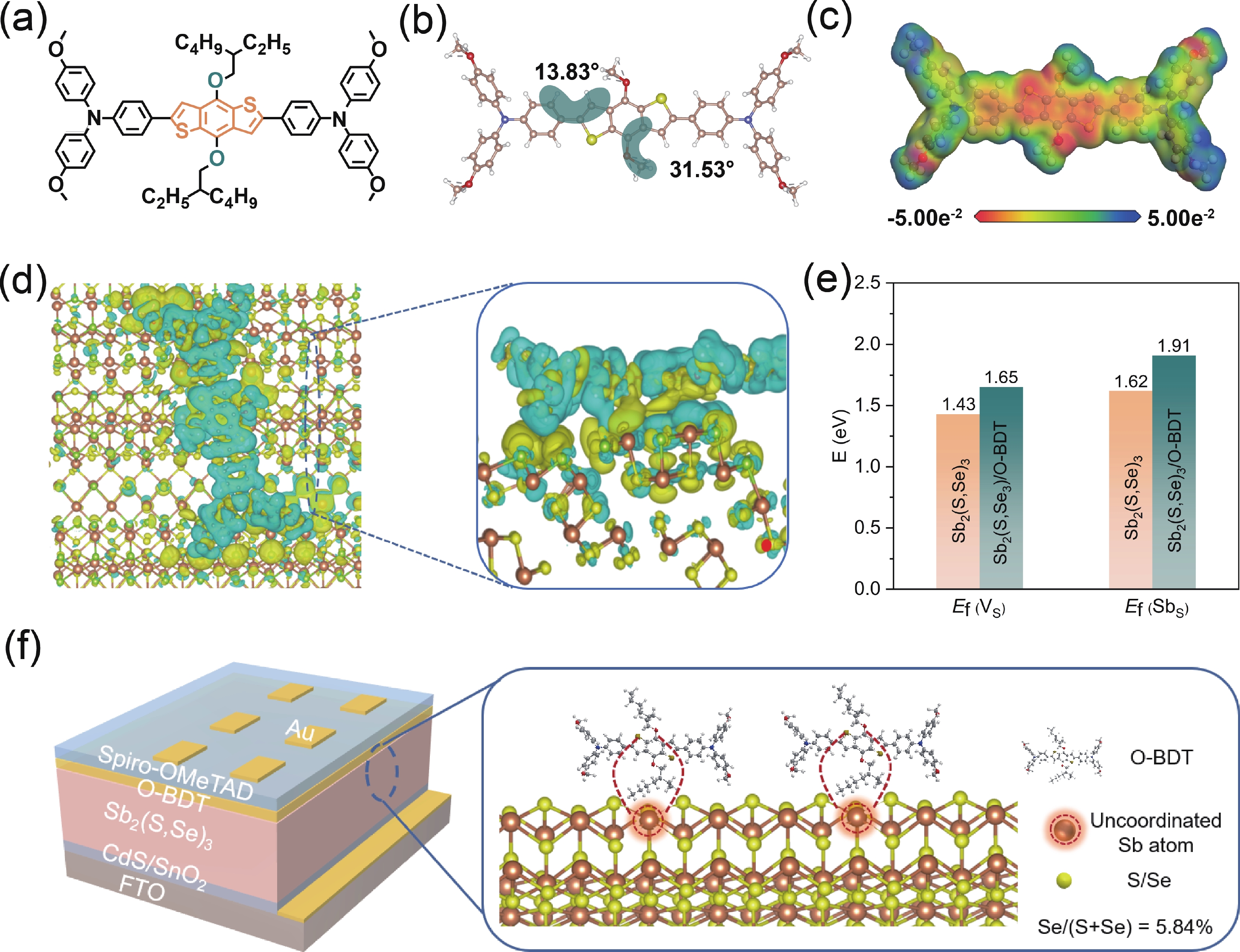

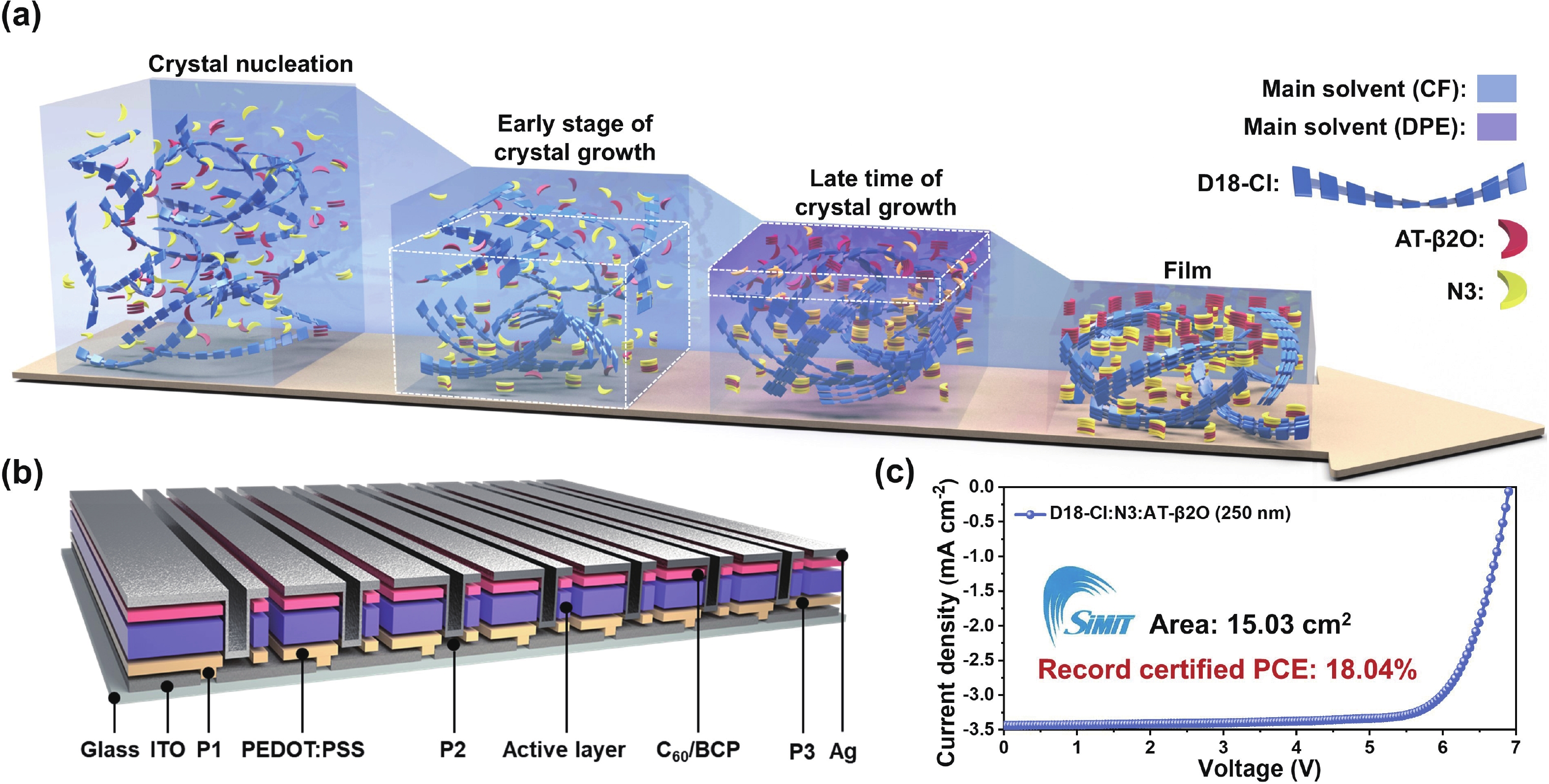

Antimony selenosulfide (Sb2(S,Se)3) is a promising photovoltaic absorber material for both outdoor and indoor application scenarios. Nevertheless, the performance of Sb2(S,Se)3 solar cells remains constrained by the severe interface trap-induced nonradiative recombination. Interface engineering has been recognized as an effective approach to suppress recombination and boost charge transport. In this work, we introduce an organic modifier (O-BDT) between Sb2(S,Se)3 absorber and hole transport layer. The theoretical and experimental results evidence that O-BDT can simultaneously passivates interface defects and optimizes the energy-level alignment, leading to a significantly reduced voltage loss. Finally, the O-BDT modified solar cell achieves a power conversion efficiency (PCE) of 8.01% under AM 1.5G illumination. Moreover, the device delivers a PCE of 19.04% under 1000 lux, 3312 K LED lighting, among the best list of IPVs based on antimony chalcogenide compounds.

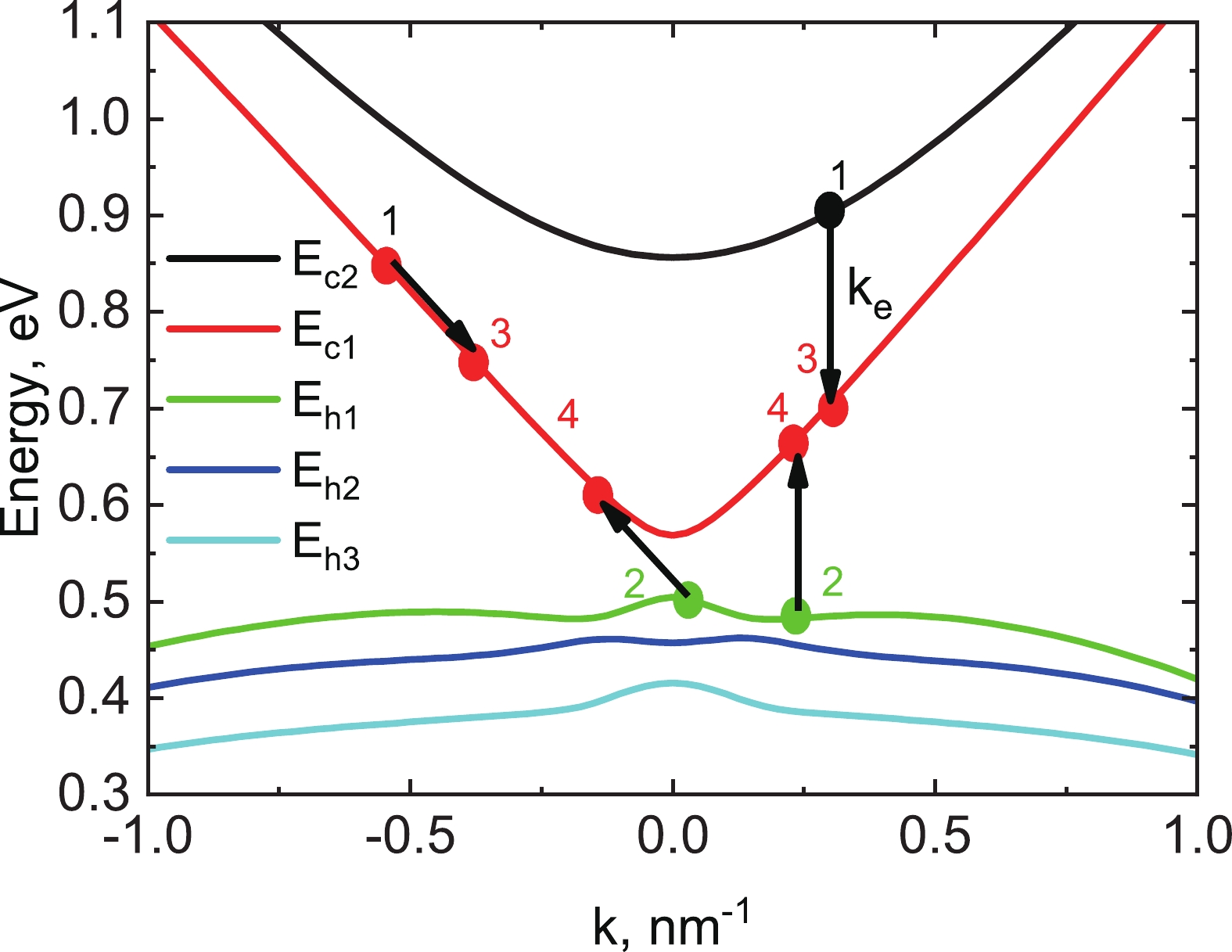

Impact ionization probabilities were calculated in a CdHgTe quantum well, where the distance between electron subbands is close to the band gap energy. This band structure enables impact ionization with small momentum transfer for electrons in the second subband. The study demonstrates that such processes increase the impact ionization probability by approximately two orders of magnitude compared to the impact ionization probability for electrons in the first subband, for which transitions with small momentum changes are impossible. The probability of single impact ionization during the electron energy loss due to optical phonon emission is estimated. Experimental methods for detecting impact ionization in this structure are discussed.

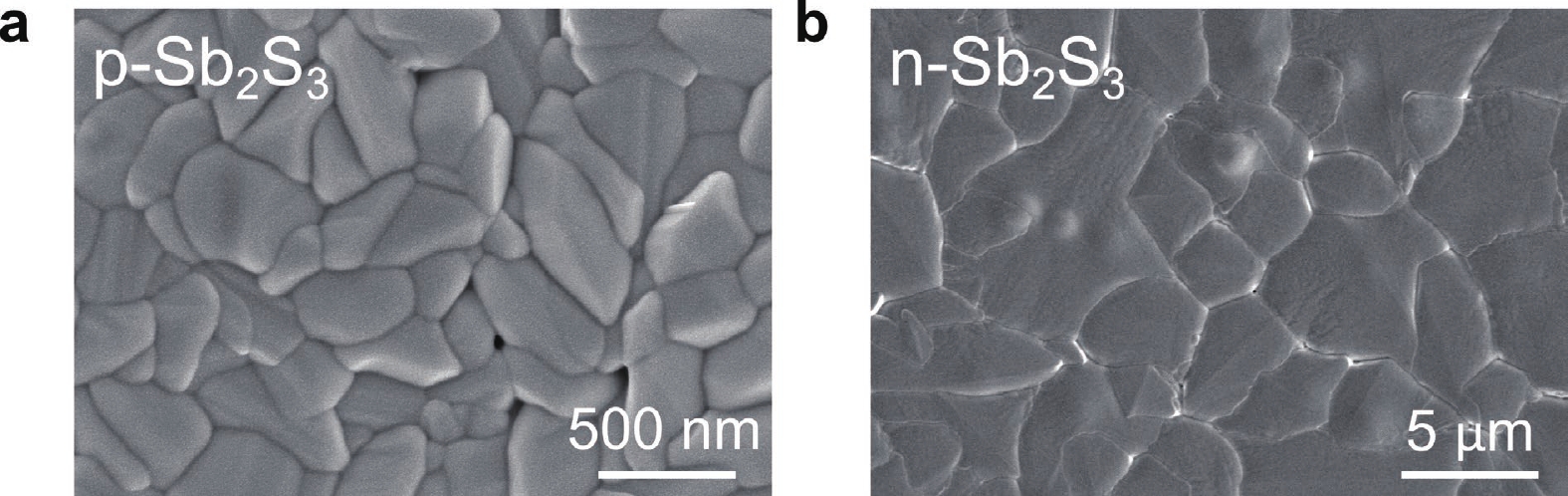

Sb2S3 has attracted increasing attention for next-generation photovoltaics due to its excellent materials and optoelectronic properties, especially a suitable bandgap (~1.75 eV) for indoor photovoltaics and silicon-based tandem solar cells. However, the highest power conversion efficiency (PCE) report thus far for Sb2S3 solar cells is 8.26%, lagging far behind its theoretical efficiency limit (~28%). This study aims to scrutinize the important roles of hole transport layers (HTLs) in near-intrinsic Sb2S3 solar cells. It is found that the device efficiencies of both of p-type Sb2S3 and n-type Sb2S3 based planar solar cells are significantly enhanced with the incorporation of Spiro-OMeTAD HTL, further confirmed by the SCAPS simulation. The specific roles of HTL on promoting the interface hole extraction in Sb2S3 solar cells are elucidated. Then the performance optimization is conducted by systematically optimizing key parameters of Sb2S3 absorbers, such as absorber thickness, defect density, and doping concentration. Furthermore, several typical inorganic HTL candidates for replacing Spiro-OMeTAD were explored for Sb2S3 solar cells, revealing that the Cu2O HTL based device exhibits a highest PCE of 23.09%. This work highlights the necessity of HTLs for devices based on near-intrinsic Sb2S3 and provides valuable insights for further enhancing the performance of Sb2S3 solar cells.

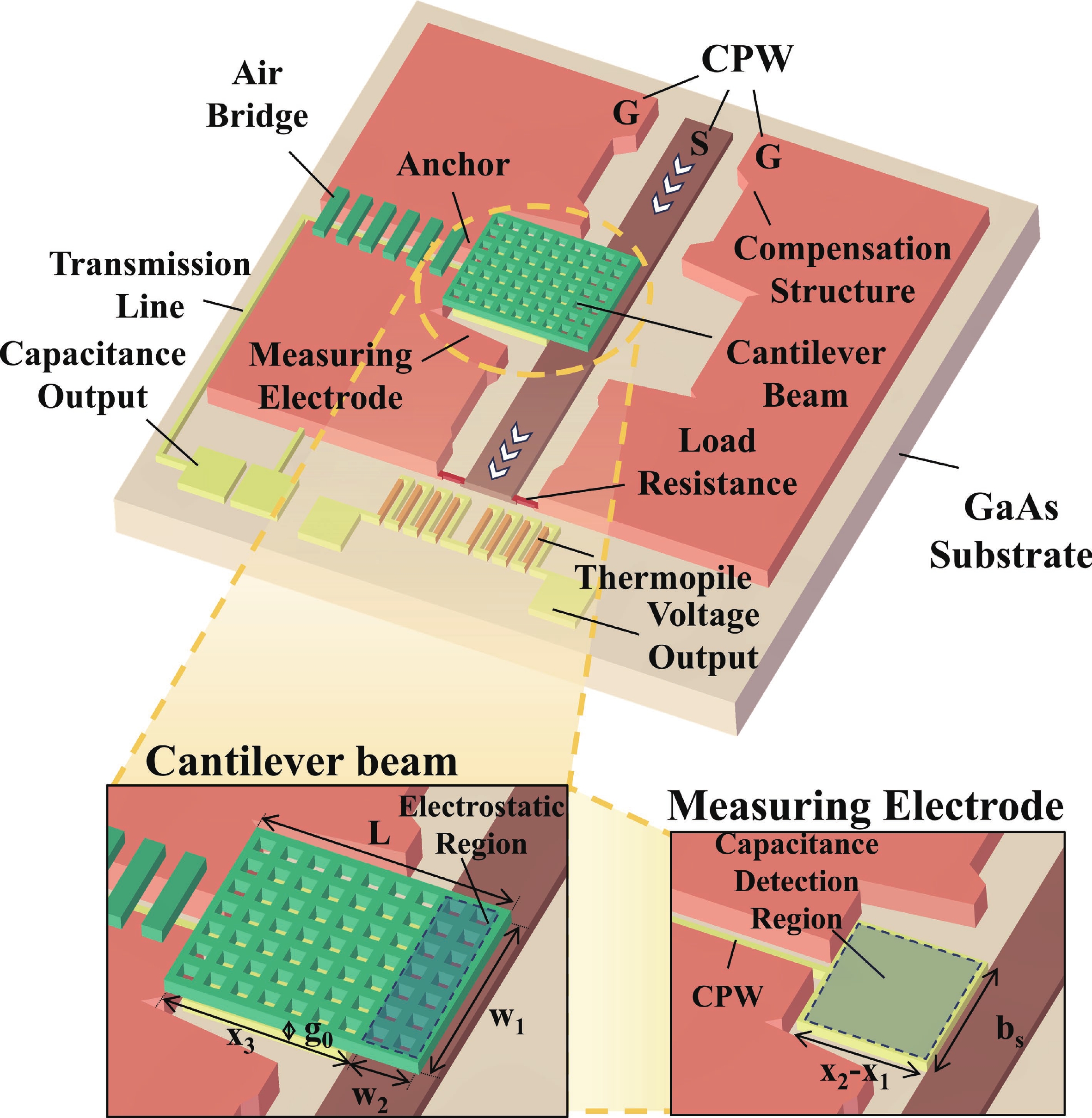

To study MEMS power detection chips more accurately, a thermo-electromechanical coupling model is proposed in this work. The fringing capacitance is included in the model, further refining the expression for the parallel-plate capacitance. Moreover, the squeeze-film damping and thermoelastic damping are considered in the second-order differential equation to study the cantilever vibration. It is found that the squeeze-film damping is the dominant damping of the system, and the cantilever beam exhibits linear expansion with increasing temperature. A dual-channel microwave detection chip is fabricated and measured, and the return loss reaches its minimum of −66.46 dB at 9 GHz, indicating optimal impedance matching at the central frequency. Moreover, the measured sensitivity is approximately 65.6 fF/W. Critically, the measured resonant frequency of the cantilever beam is 115.7 kHz, which is orders of magnitude lower than the input signal frequency. This large separation ensures that the sensor operates in a stable, non-resonant regime, thereby guaranteeing linearity and reliability. These findings demonstrate the excellent microwave performance of the power sensor fabricated in this work, providing valuable insights for optimizing the design of MEMS microwave power detection chips.

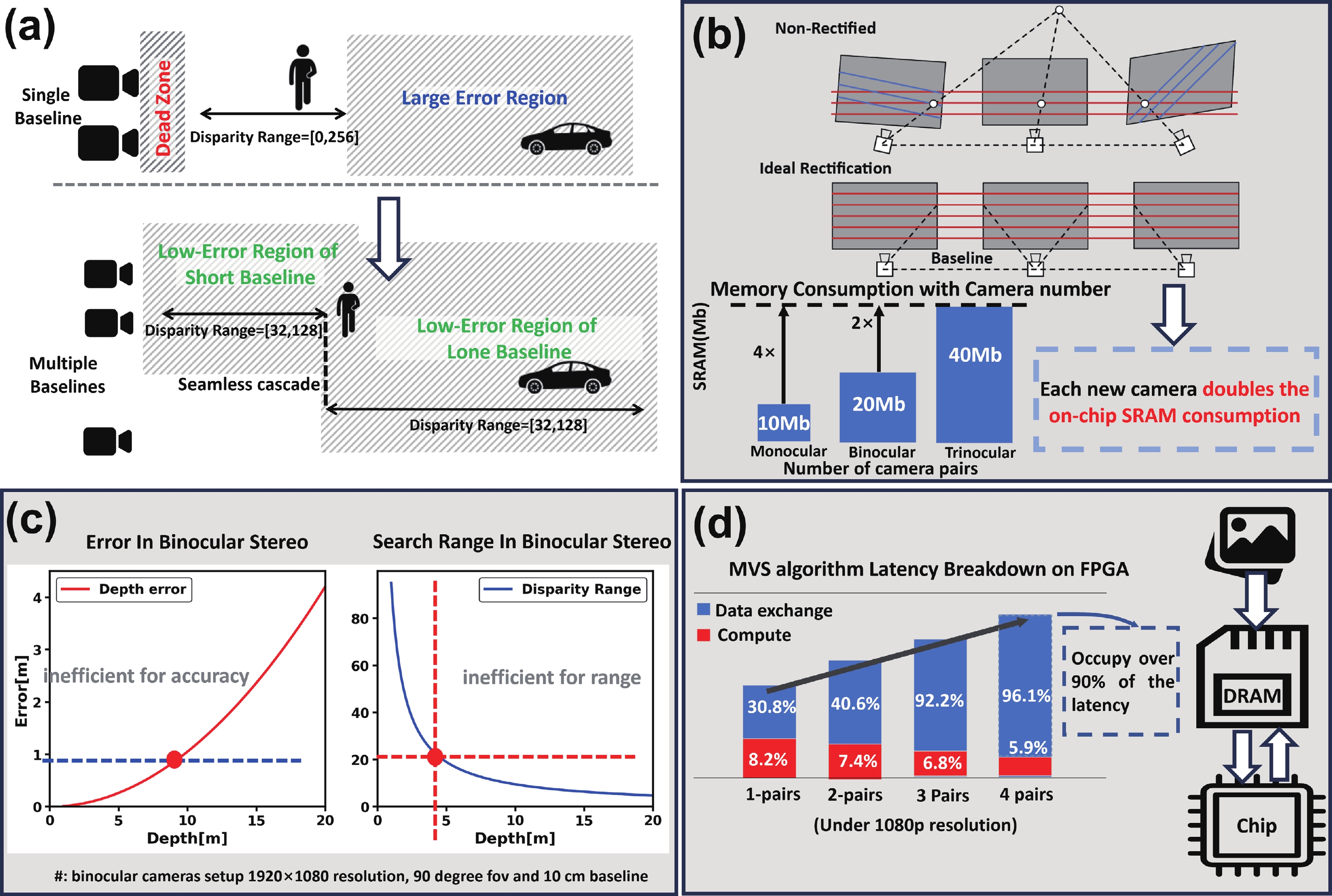

Achieving long-range, high-accuracy depth perception under stringent power constraints remains a critical challenge for stereo vision in edge applications. This work presents a cascadable stereo matching processor that overcomes the inherent trade-off between sensing range and computational efficiency. The core innovation is a scalable semi-global matching (SSGM) algorithm which dynamically optimizes the disparity search range for different baselines, ensuring constant on-chip memory usage and a significant reduction in data movement. The architecture further integrates a raw-domain rectification front-end, which performs direct geometric transformation on Bayer-patterned image streams. This approach eliminates the need for external memory access by bypassing conventional ISP pipelines, thereby maximizing throughput and reducing system memory consumption. Parallel processing paths for multiple baselines converge in a pixel-wise fusion module, which synthesizes a unified depth map by selecting the most reliable disparity estimate for each output pixel. The cascadable stereo matching processor achieves speedups of up to 178x and 97x over CPU and EdgeGPU platforms, respectively, in multi-baseline stereo disparity fusion. Implemented in 40-nm CMOS technology, the processor operates at 160 MHz, achieving a processing speed of 80 frames per second with an energy efficiency of 7.9 pJ/pixel and occupying a core area of 6.04 mm2.

In fractional-N phase-locked loops, minimizing the integral nonlinearity (INL) of the digital-to-time converter (DTC) is crucial since it directly limits PLL performance. Considering the trade-off between DTC delay range and linearity, this paper presents a fractional-N dual-path SPD/PFD PLL (DP-SPFDPLL) with a complementary DTC pair. Controlled by the complementary control words, two DTCs are introduced before the two inputs of the phase detector for DTC range reduction and INL cancellation. The required DTC range is further halved by using differential VCO outputs to retime the frequency divider output. The overall design collectively achieves a 4× reduction in DTC range requirement. Fabricated in 7 nm FinFET, the DP-SPFDPLL achieves 118 fs RMS jitter and −247.5 dB figure-of-merit.

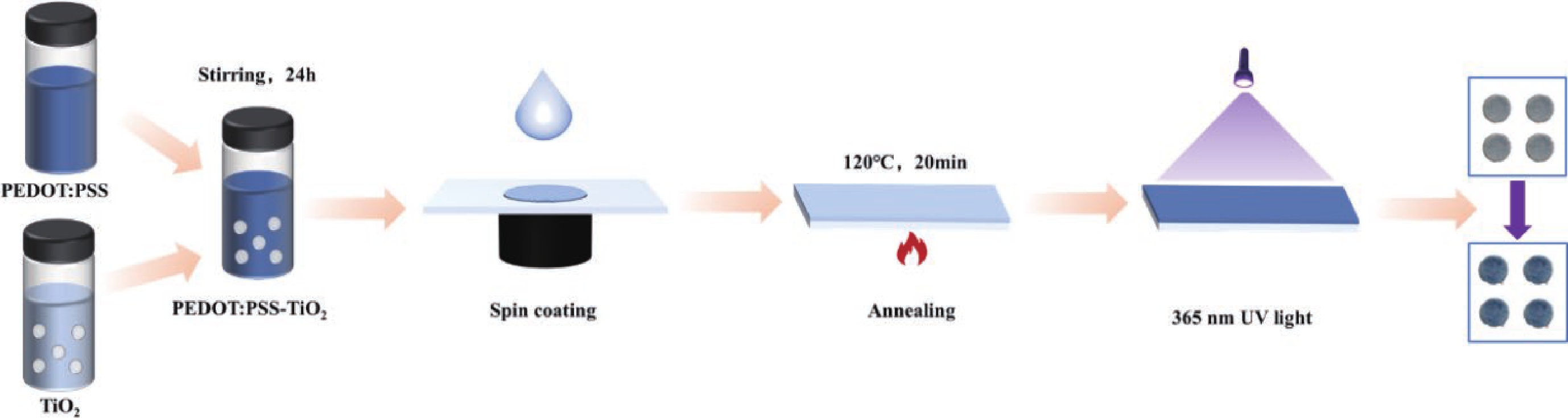

Integrating electrochromic (EC) and photochromic (PC) functions within a single material system holds great significance for the development of next-generation intelligent responsive materials. Traditional organic photochromic materials are all small molecules and oligomers, which require the photochemical response of specific photosensitive groups. However, PEDOT:PSS, a classic electrochromic polymer, has never been reported to exhibit photochromic properties due to the absence of photosensitive groups. Herein, we report for the first time the photochromic properties of PEDOT:PSS films, demonstrating their simultaneous capability of multi-field coupling response in the aspects of light, electricity and chemistry. The composite film undergoes a rapid color change from light blue to dark blue under ultraviolet light irradiation. This is attributed to the transformation process from the bipolarons state to the polarons state in the PEDOT:PSS, induced by photogenerated electrons as confirmed by EPR and Raman analyses. Furthermore, the developed hydrogel system enhances charge separation, yielding a 30.1% relative transmittance change and month-long stability. This work fills the long-standing gap in the understanding of the photochromic and electrochromic mechanisms of PEDOT:PSS, providing fundamental insights into carrier dynamics at organic−inorganic interfaces and laying the foundation for the development of multi-mode stimuli-responsive devices.

In recent years, position-sensitive detectors (PSDs) have found widespread application in displacement measurement, optical measurement, imaging, and laser communication, owing to their high spatial resolution and rapid response capabilities. However, the performance and operating mechanisms of perovskite-based PSDs remain insufficiently elucidated. In this work, we fabricated a high-sensitivity self-powered PSD based on a ZnO/P(VDF-TrFE)−CH3NH3PbI3(MAPbI3) heterojunction. Systematic optimization revealed an optimal P(VDF-TrFE) doping concentration of 5 mg/mL, enabling the device to achieve a remarkable positional sensitivity (PS) of 307.03 mV/mm with a minimum nonlinearity of 1.02%. Furthermore, the intrinsic pyroelectric property of P(VDF-TrFE) induces a significant pyroelectrically enhanced lateral photovoltaic effect (LPE), boosting the PS to 511.33 mV/mm—an enhancement of 166.5%. The heterojunction PSD maintains effective operational performance over an electrode spacing range of 0.5−2.2 mm. While the LPE response declines with increasing spacing, a considerable pyroelectric effect (PE)-enhanced PS of 70.67 mV/mm is retained even at 2.2 mm. Importantly, we demonstrate multi-wavelength imaging by exploiting both the inherent LPE response and its pyroelectrically enhanced counterpart, with imaging intensity tunable via electrode spacing control. This study provides crucial insights into the LPE behavior of the heterojunction and systematically clarifies the mechanism by which the PE modulates device performance and imaging capabilities.

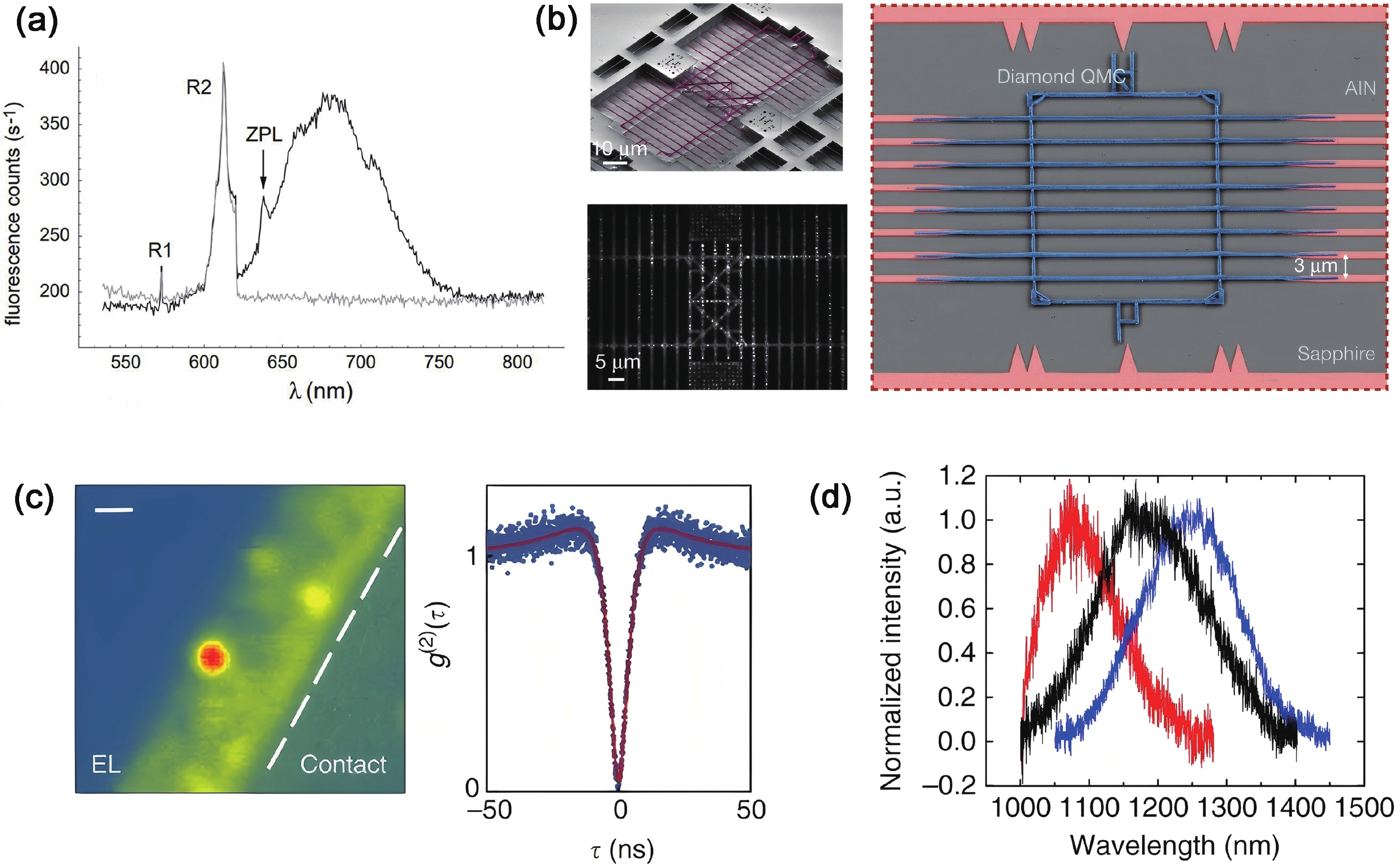

Charged quantum dots (QD) coupled to micropillar cavities are key platforms for studying photon-spin interactions. However, most research involves quantum dots charged via external excitation, resulting in short charge lifetimes. We demonstrate a device where a quantum dot confines an extra electron through δ-doping and couples to a high Q-factor (about 11 000) micropillar cavity mode (CM). We propose a precise calibration process for the micropillar cavity to achieve coupling between the negatively charged exciton (X−) transitions and CM at low temperatures. Micro-photoluminescence (μPL) spectroscopy confirms X− transitions and their coupling with CM at 7 K, with the coupled emission intensity enhanced about tenfold relative to the uncoupled state. The X− transitions and CM both show low spectral fluctuations at the change of polarization of incident light (X− 2.66 μeV, CM 3 μeV).

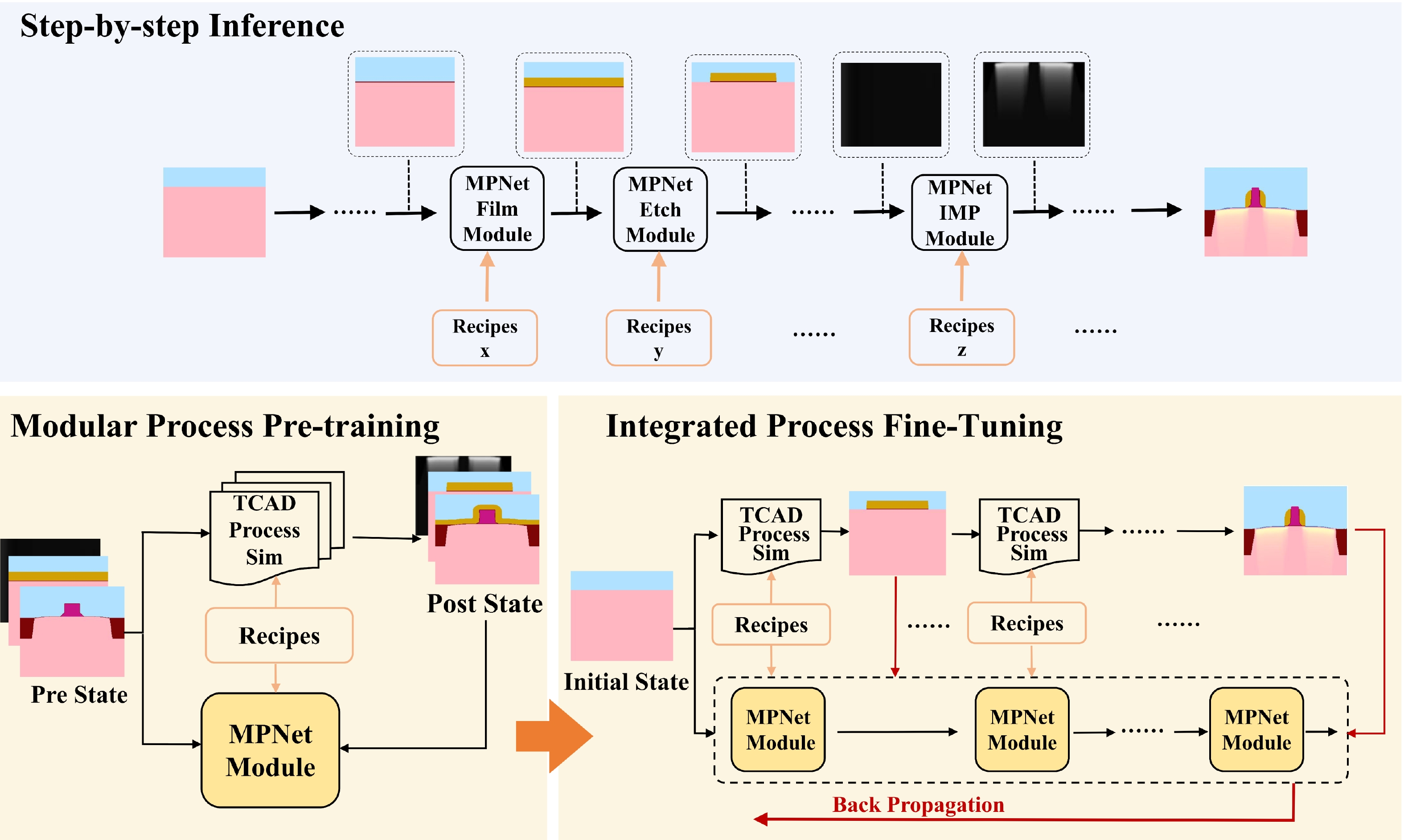

The computational cost of TCAD simulations is becoming prohibitively high with the complexity of advanced process technologies, making simulation acceleration a critical research priority. While end-to-end surrogate models mapping process recipes to device structures and characteristics offer a promising alternative, their application is often limited by poor generalizability and explainability. In this work, we present MPNet, a modular deep learning surrogate modeling framework for process TCAD. MPNet comprises distinct surrogate models for individual process modules, which are assembled into an integrated framework. These modular models employ a novel UNet-attention feature evolution method to capture the complex evolutions of device geometry and doping profiles. Each module can be trained separately on its individual process, after which the modules are cascaded and jointly fine-tuned to minimize error accumulation throughout the cascade. The efficacy of the proposed MPNet framework is demonstrated through a MOSFET integrated process TCAD case study. Results show that MPNet achieves a computational speedup of over 103 times compared to conventional TCAD, while maintaining predictive fidelity exceeding 98%. Finally, to illustrated the application of the proposed framework, MPNet is coupled with a PSO algorithm, showcasing its utility for fast process optimization to meet specific process targets.

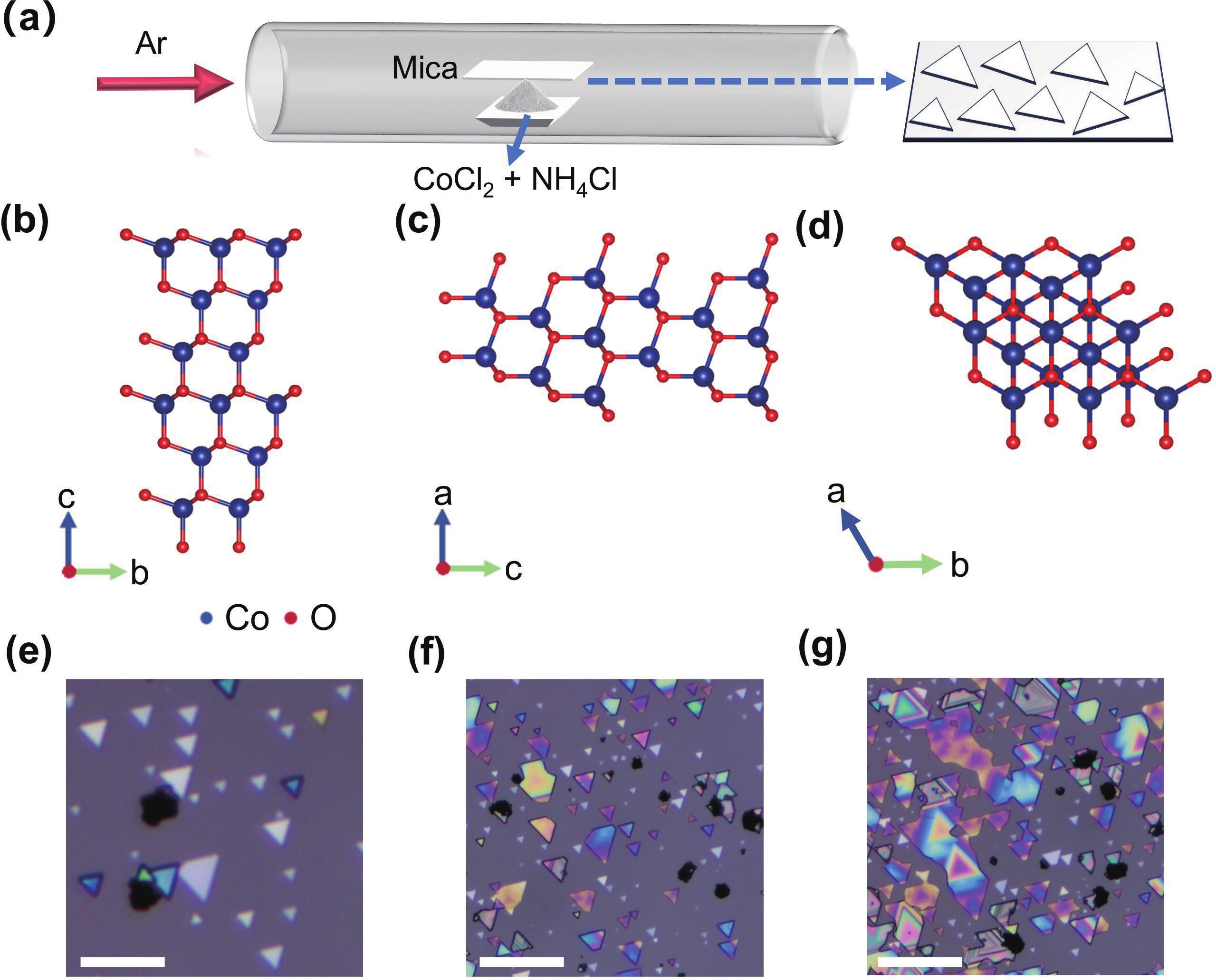

Two-dimensional (2D) magnetic materials have attracted significant attention owing to their tunable magnetic properties and prospective applications in next-generation spintronic devices. However, their practical utilization is often limited by poor air stability. 2D magnetic metal oxides, which generally exhibit better stability under ambient conditions, represent a promising alternative. In this work, high-quality CoO nanosheets were successfully synthesized via chemical vapor deposition. Structural characterization confirms a well-defined triangular morphology and single-crystalline nature, with the thinnest nanosheets reaching approximately 10.1 nm in thickness. Magnetic measurements reveal significant magnetic anisotropy with an in-plane easy magnetization axis and a transition temperature of approximately 159 K. Our study provides a feasible approach for the controllable synthesis of air-stable 2D magnetic semiconductors, thereby laying a foundation for their potential application in low-power spintronic devices.

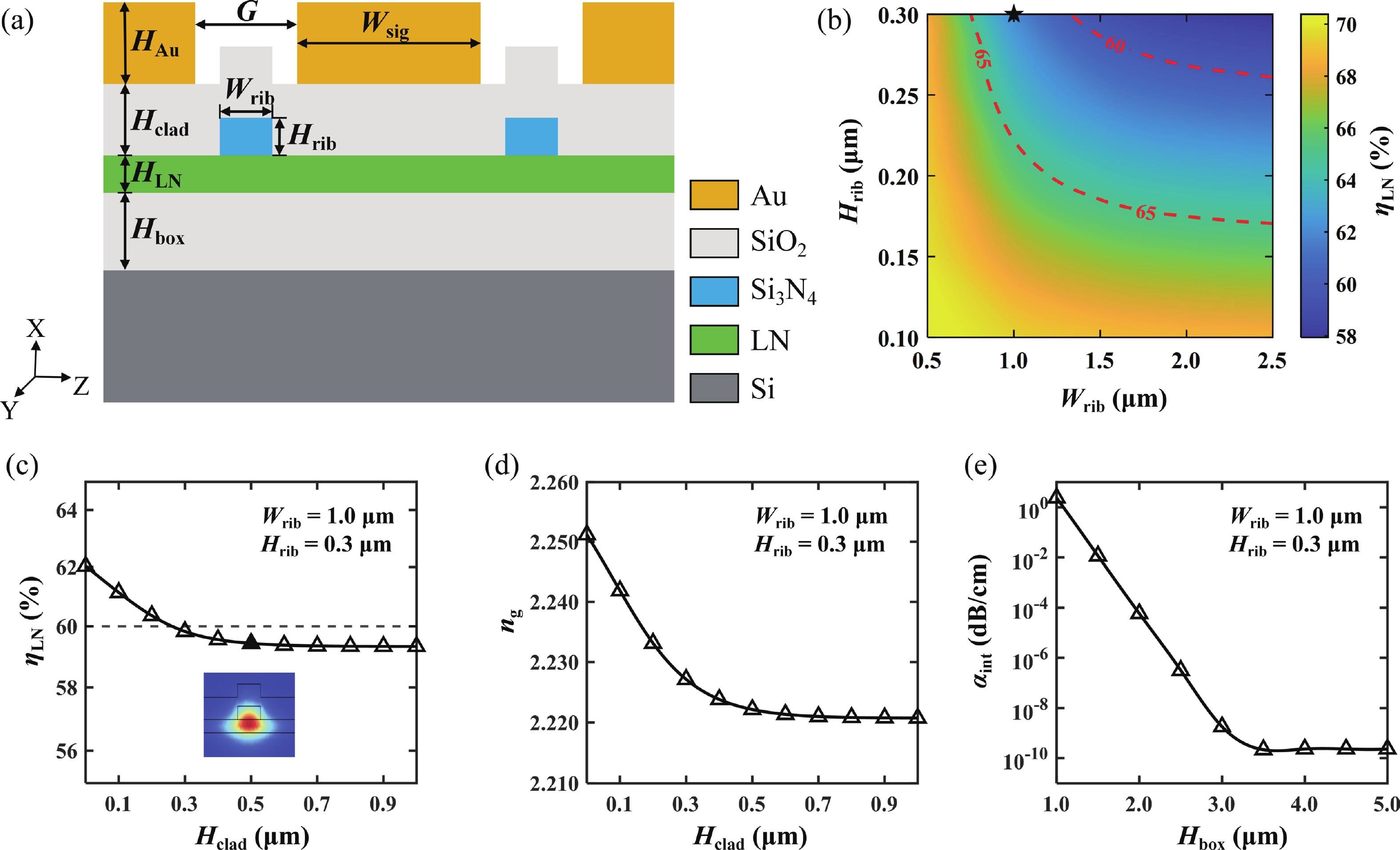

Heterogeneously integrated lithium niobate (LN) electro-optic modulators have great potential for high-speed applications, but challenges remain in optimizing performance, particularly in terms of modulation efficiency, bandwidth, and the trade-offs. This work presents an optimized design for a silicon-nitride (Si3N4)-loaded modulator on a thin-film lithium niobate (TFLN) platform, consisting of 300 nm-thick LN film and 300 nm-thick Si3N4 optical waveguide. By systematically optimizing the dielectric layer thickness, electrode parameters, and achieving velocity and impedance matching, we demonstrate a modulator with a bandwidth exceeding 200 GHz. Our collaborative optimization scheme highlights the critical role of reducing the silicon oxide box layer thickness for velocity matching. We show that multiple structural configurations can achieve bandwidths greater than 120 GHz with Vπ·L< 4 V·cm, providing feasibility in low-loss design and fabrication. These findings offer valuable design guidelines for high-performance electro-optic modulators suitable for data communications.

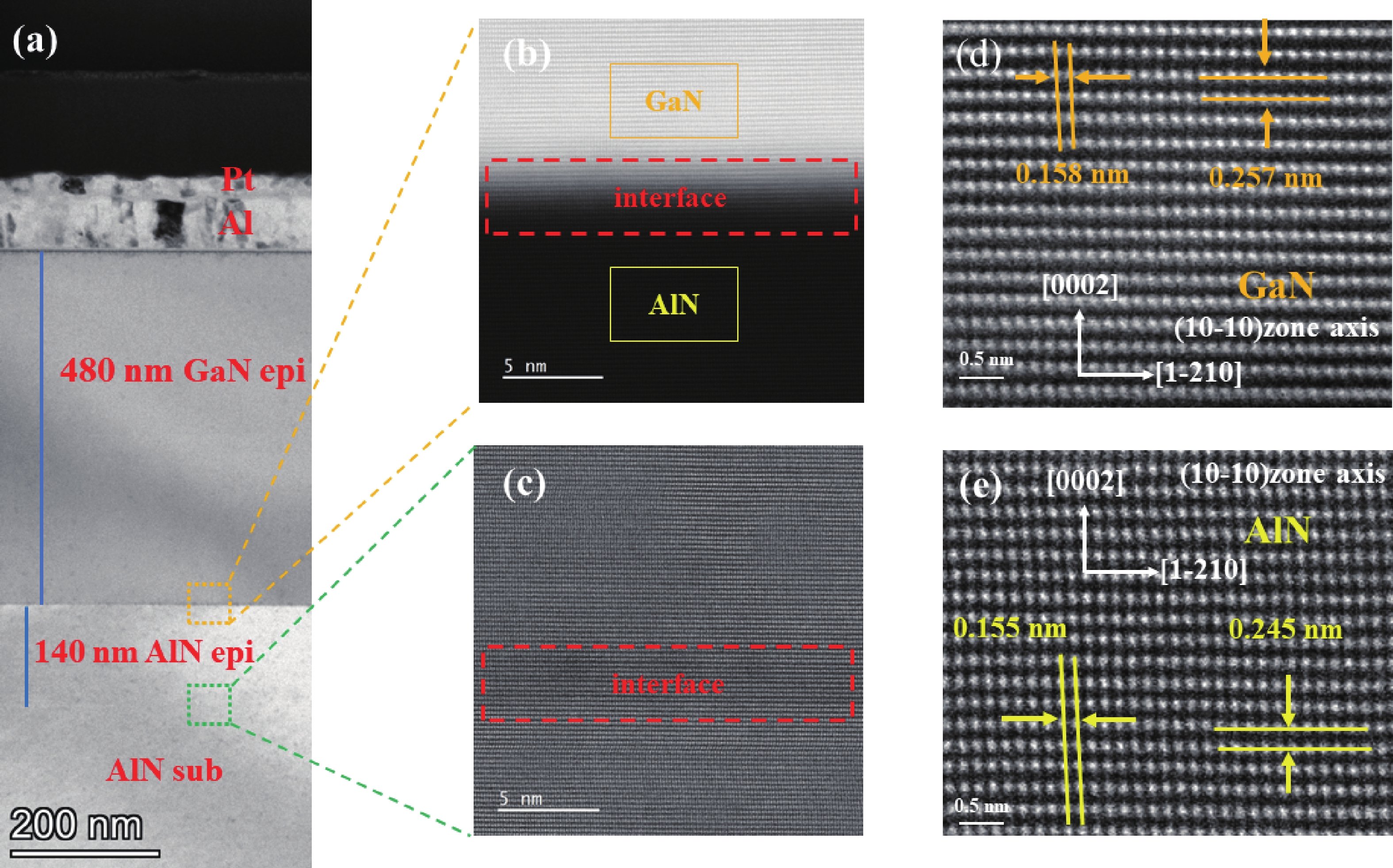

Bulk single-crystal aluminum nitride (BSC AlN) substrates are known to be ideal platforms for constructing high-power and DUV optoelectronic nitride devices. However, high-quality epitaxial growth of nitride films on BSC AlN and related characterization is still far from being well studied. The challenges and uncertainties in doing accurate thermal characterization on such heterostructures are not fully recognized. In this study, we successfully fabricated a buffer-free thin GaN/AlN heterostructure on a BSC AlN substrate via metal−organic chemical vapor deposition (MOCVD) technology. This heterostructure consists of a 140 nm-thick AlN homoepitaxial layer and a 480 nm-thick GaN epitaxial layer. Characterization results indicate that the prepared heterojunction has excellent crystal quality and smooth surface morphology. To accurately obtain the thermophysical parameters of the heterostructure, this study employed broadband frequency domain thermoreflectance (BB-FDTR) technology, and careful measurements with detailed data analysis were demonstrated. In addition to showing the feasibility of epitaxial growth of high-quality thin film GaN directly on BSC AlN substrates, this study also provides key experimental data for evaluating the heat dissipation advantages of GaN/AlN heterostructures.

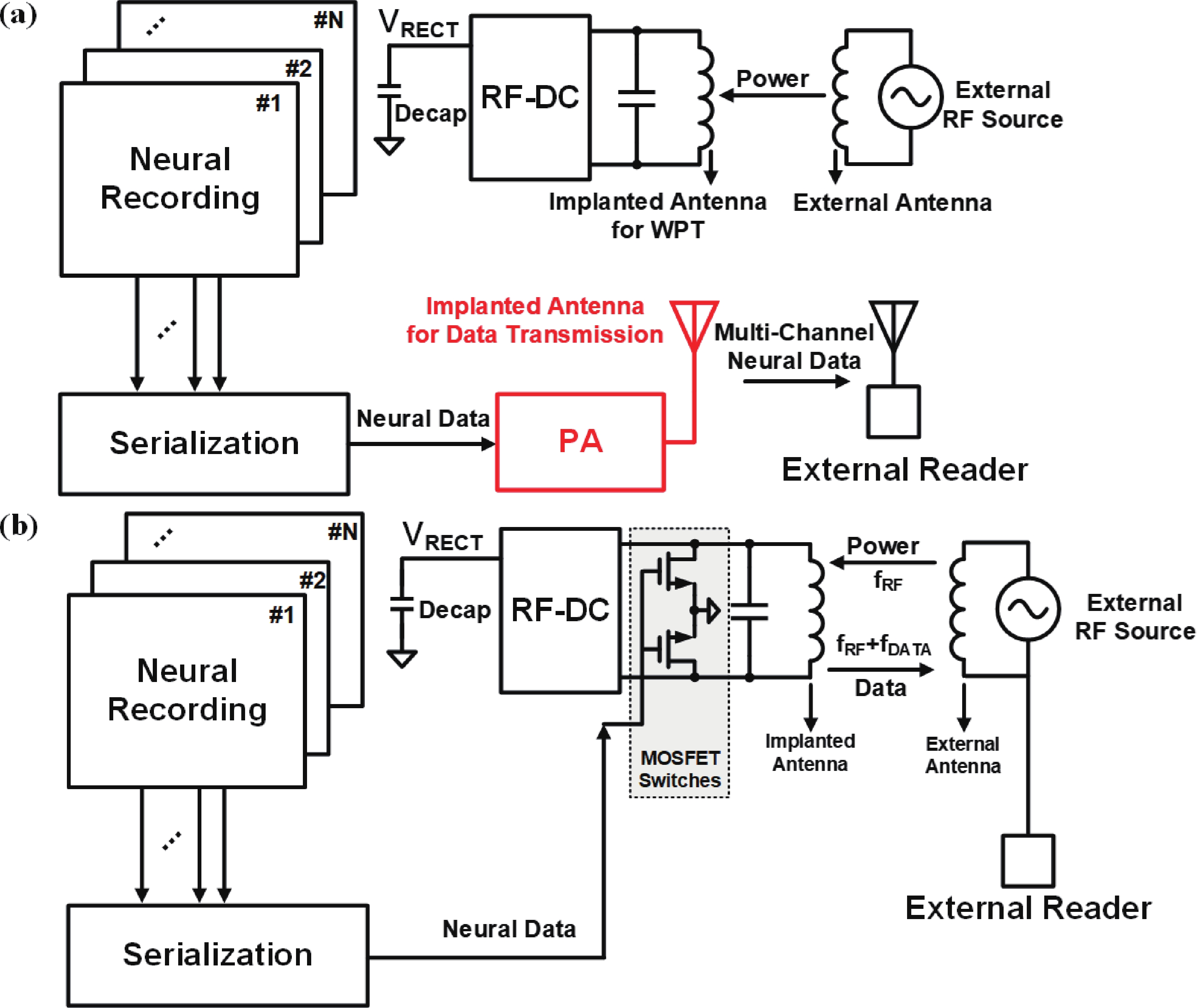

Battery-free radio systems utilizing wireless power transfer (WPT) further facilitate the miniaturization of neural implants. However, simultaneous monitoring of multiple neuronal activities is required to obtain high-fidelity neural signals. Consequently, the integration of numerous channels on a single chip and the wireless transmission of massive multi-channel data pose significant challenges for implantable battery-free neural interfaces. This work introduces dual overlapped on-chip antennas to eliminate the need for a battery in the neural implants and enable high-data-rate backscatter for transmitting the massive data acquired simultaneously from 72 channels. Additionally, an orthogonal coding and sampling technique is employed to reduce both power consumption and area per channel. Fabricated in a 65 nm CMOS process, the proposed chip integrates 72 neural recording channels within a 2 mm × 2 mm area and achieves a backscatter data rate of 18 Mbps.

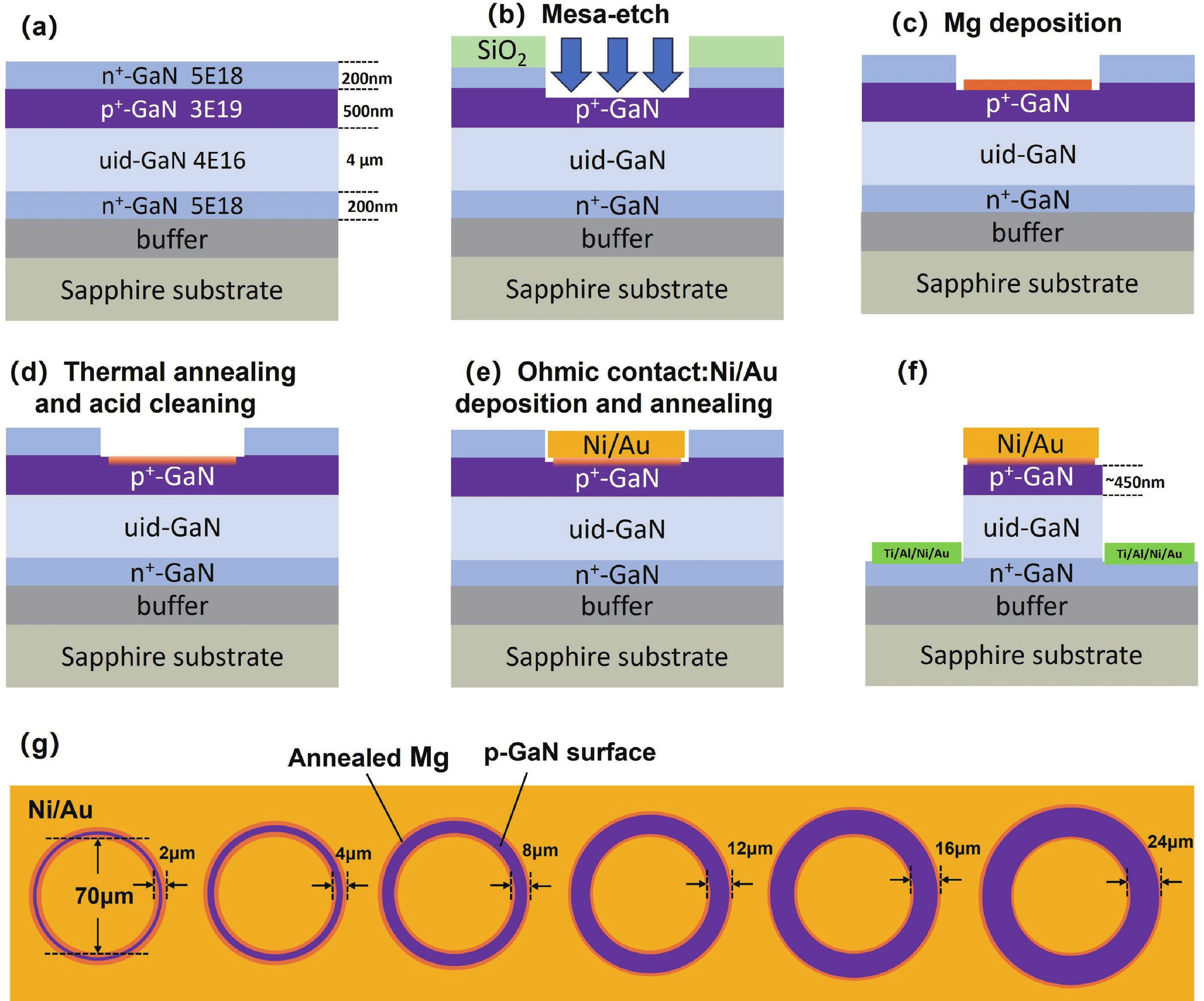

This work demonstrates a high-performance vertical GaN p−i−n diode based on a buried p-layer n-p−i−n epitaxial structure. The post-etch magnesium (Mg) diffusion process is applied to suppress the etch-induced surface damage on the p-GaN layer. The Mg diffusion effectively reduces the valence band barrier from 2 to 1.1 eV, yielding a low specific contact resistivity of 6.521 × 10−4 Ω·cm2. As a result, the fabricated devices exhibit markedly enhanced forward characteristics, including a reduced turn-on voltage of 3.3 V and a specific on-resistance of 0.92 mΩ·cm2. Temperature-dependent forward I−V measurements indicate that the dominant carrier transport mechanism evolves from defect-related tunneling in the etched devices toward transport dominated by intrinsic p–n junction conduction after Mg diffusion. In addition, the devices exhibit excellent stability in forward conduction, with a voltage variation of approximately 0.028 V. These results indicate that Mg diffusion effectively improves the contact characteristics degraded by ICP etching and provide a viable approach for achieving high-performance and reliable vertical GaN power devices.

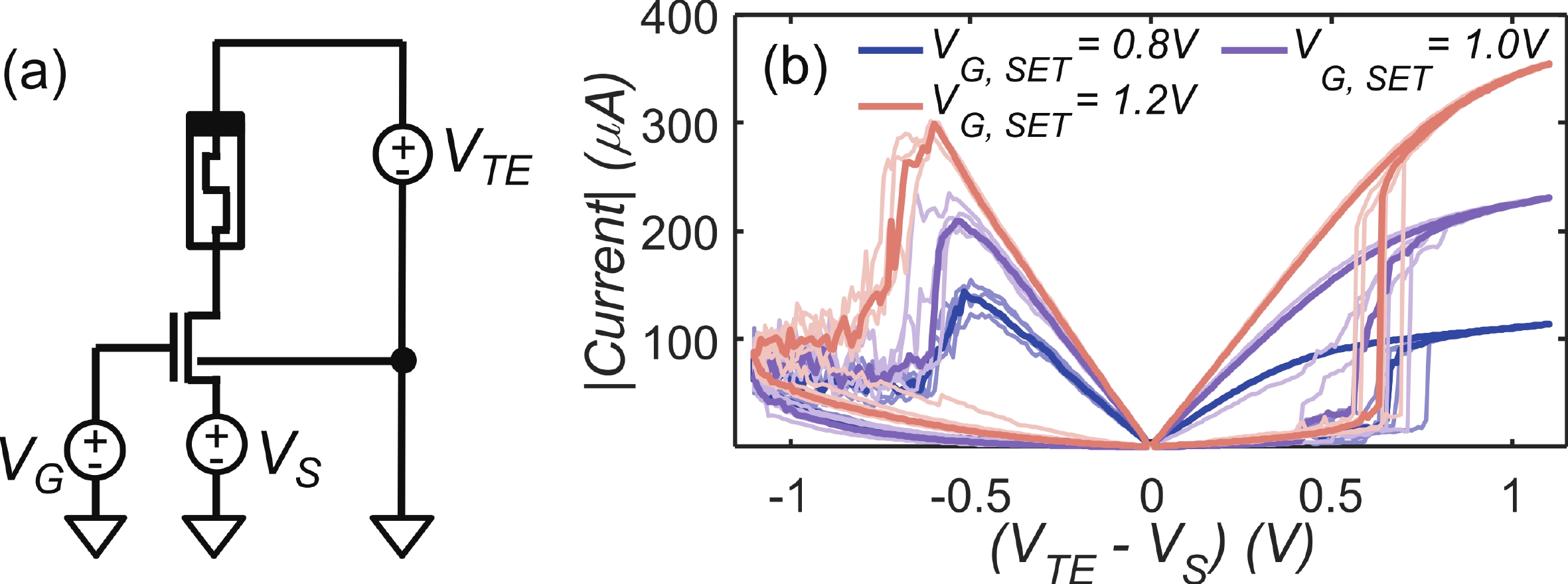

Resistive random access memories (RRAMs) are emerging as a key enabling technology for cost-effective, energy-efficient and secure chips, especially in the framework of edge computing. In particular, their electrically programmable resistance has been widely exploited in several in-memory computing and neuromorphic architectures. By adjusting the applied voltages and compliance currents (IC), RRAM devices can be programmed to multiple resistance states during set and reset procedures, enabling multilevel functionality. While the multilevel behavior of the reset phase is generally well captured by existing compact models, only a few account for the multilevel characteristics of the set operations. Moreover, such models are rarely validated against comprehensive experimental datasets capturing device dynamics across multiple timescales. In this work, we present a physics-based compact model that enhances the UniMORE RRAM framework by incorporating the dynamic lateral evolution of the conductive filament (CF), thereby enabling accurate simulation of set operations at varying IC values. The model is calibrated to experimental data from IHP 130 nm 1T1R RRAM technology and reproduces device behavior across several operating conditions using a single set of parameters. The results highlight the potential of the proposed compact model in design optimization workflows of RRAM-based circuits.

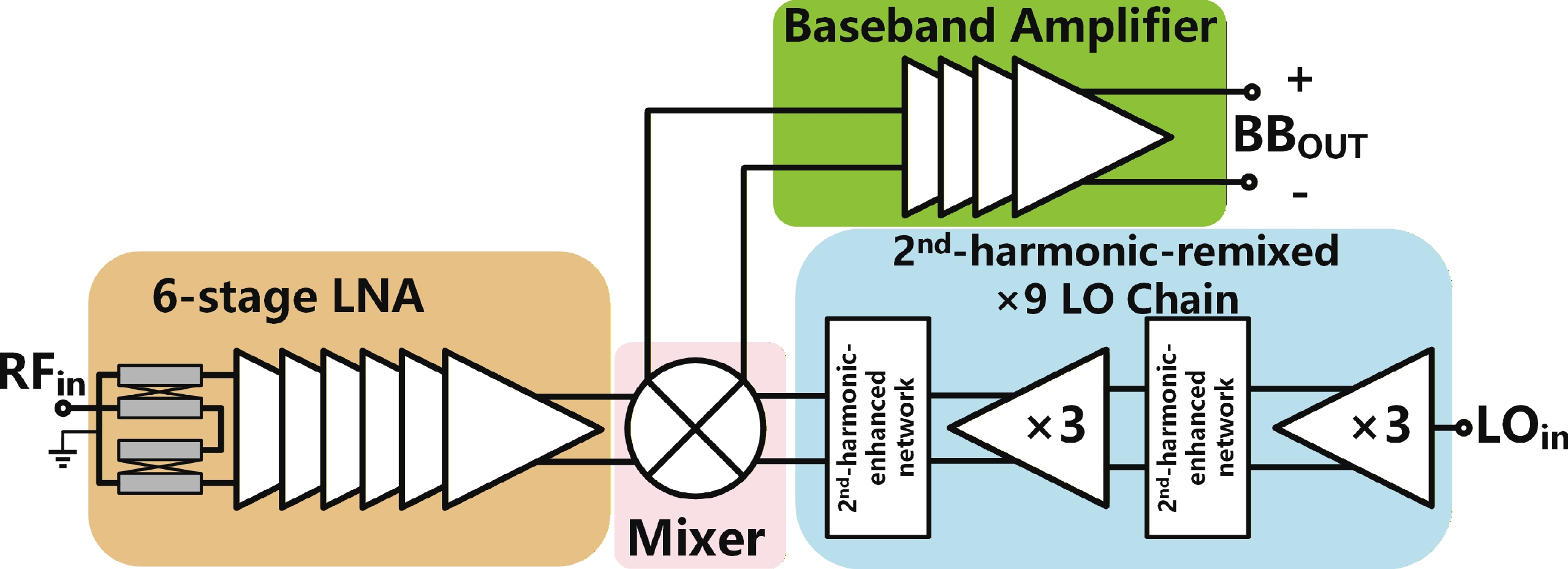

In this paper, a compact and low-power sub-THz direct-conversion receiver with a second-harmonic-remixed LO chain is proposed. Based on a common-mode second-harmonic-enhanced network, the common-mode second-harmonic voltage at the drains of the common-source differential pair in the tripler is enhanced and mixed with the fundamental voltage at the gate to generate additional differential third-harmonic voltage. Hence, the saturation output power and efficiency of the triplers used in the LO chain have been significantly improved. The power consumption of the LO chain employed in the receiver is as low as 65 mW. Measurement results demonstrate that the receiver achieves a conversion gain of 30.5 dB and a 3-dB RF bandwidth of 34 GHz, while the in-band minimum noise figure is 9.9 dB.

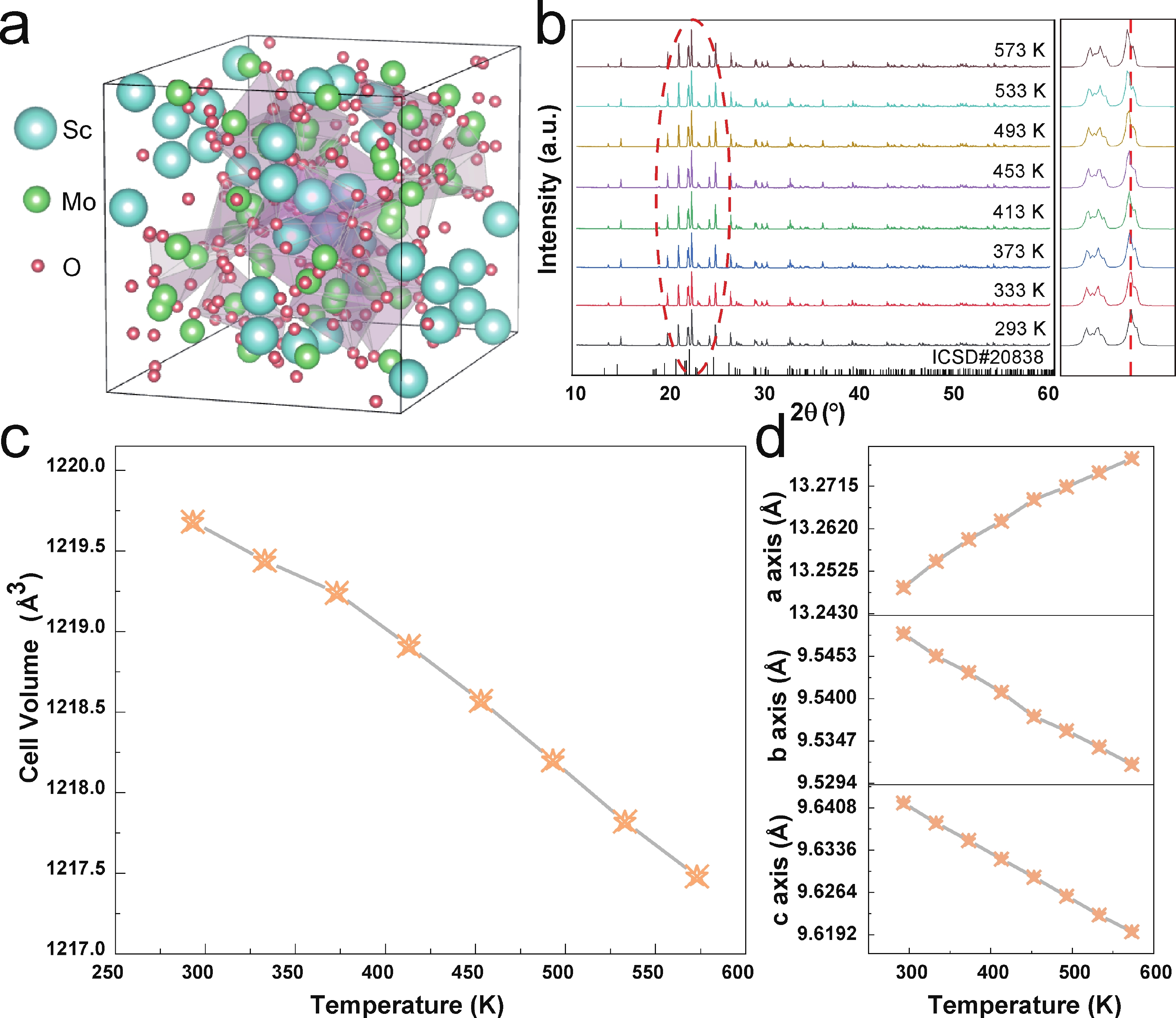

Fluorescence temperature sensing technology has become a research direction in the field of temperature measurement with its significant advantages of non-contact measurement, high spatial resolution, fast response and anti-electromagnetic interference. Although the double rare earth ion doping ratio fluorescent temperature sensing materials have made significant progress, the thermal quenching phenomenon is still the key bottleneck restricting its performance improvement. In this study, we propose to construct a flexible Sc2Mo3O12:Eu3+/Tb3+ film with negative thermal expansion characteristics, and systematically study its visual temperature sensing characteristics. The negative thermal expansion characteristics of Sc2Mo3O12 matrix effectively inhibited the thermal quenching rate of Tb3+ luminescence, and enhanced the thermal enhanced luminescence effect of Eu3+. This two-way regulation mechanism improves the intensity comparison of the two light-emitting channels, and provides an innovative strategy for improving the sensitivity of temperature sensing. The flexible film based on Eu3+/Tb3+ codoped system realizes intuitive temperature perception through the significant change of fluorescent color, and can complete the temperature interpretation without complex spectral equipment. This greatly expands its application prospect in the field of rapid field detection and real-time monitoring, and shows its broad potential in the fields of wearable devices, biomedical diagnosis, and real-time monitoring of surface temperature field.

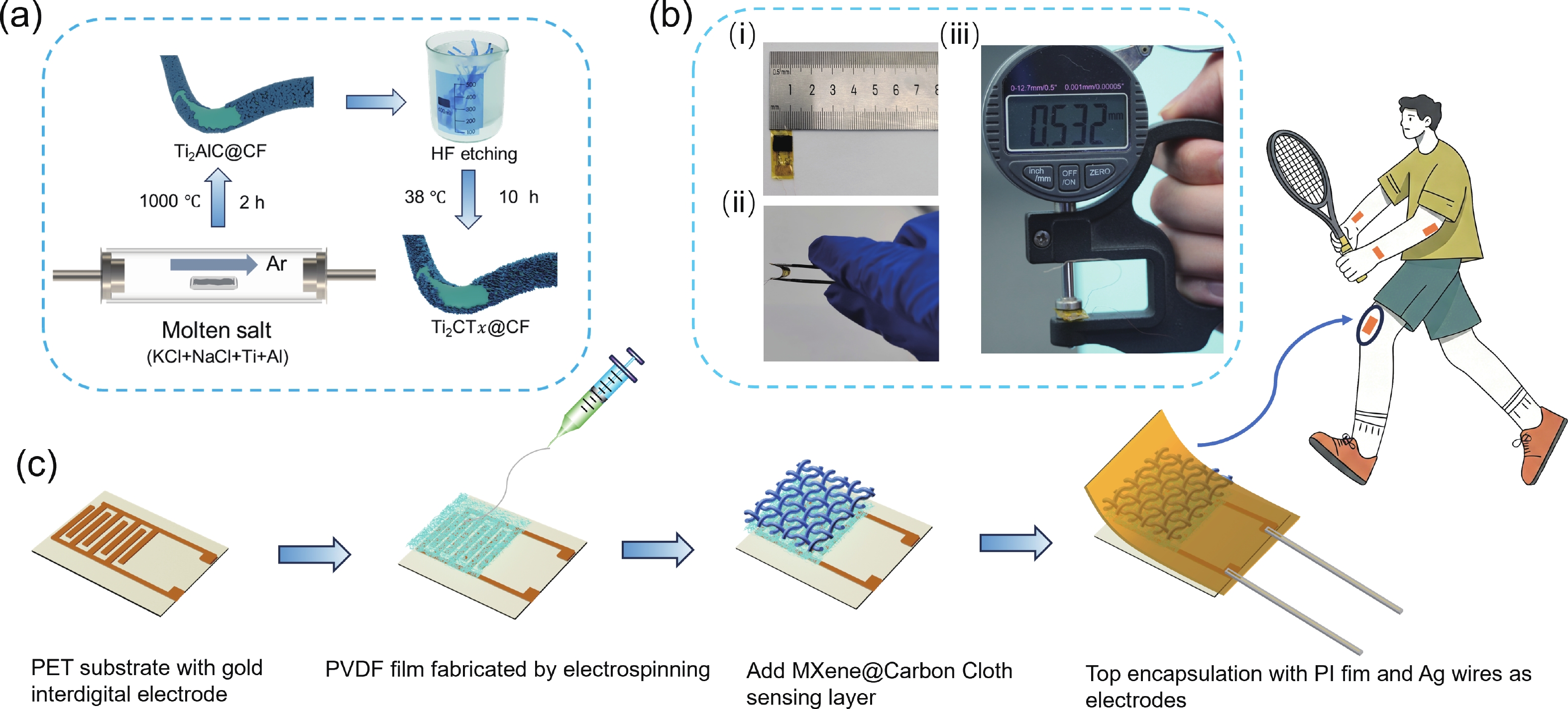

High performance flexible pressure sensors, as a very important group of electronic component for information transmission and collection, have gained widespread attention. Herein, Ti2CTx MXene nanosheets were vertically grown on carbon cloth substrate (Ti2CTx@CC) via the simple sintering and subsequent etching process. Flexible pressure sensors featuring the Ti2CTx MXene nanosheets as the sensitive material were then fabricated using polyvinylidene fluoride (PVDF) film weaved by the electrospinning route between the sensitive material and the interdigital electrodes to improve the sensitivity. As-fabricated flexible sensor exhibited superior performances including high sensitivity up to 3109.2 kPa−1, good response and recovery time of 80/80 ms, and favorable stability over 8000 loading/unloading cycles. Boasting the high sensitivity across a broad range, the sensor can in real-time capture a spectrum of human activities—from the faint pulse signal to the large pressure of joint activities and shows promising capability for mapping spatial pressure distribution.