| Citation: |

Liheng Lou, Lingling Sun, Haijun Gao, Haiting Zhan. A wideband frequency synthesizer with VCO and AFC co-design for fast calibration[J]. Journal of Semiconductors, 2013, 34(1): 015008. doi: 10.1088/1674-4926/34/1/015008

****

L H Lou, L L Sun, H J Gao, H T Zhan. A wideband frequency synthesizer with VCO and AFC co-design for fast calibration[J]. J. Semicond., 2013, 34(1): 015008. doi: 10.1088/1674-4926/34/1/015008.

|

A wideband frequency synthesizer with VCO and AFC co-design for fast calibration

DOI: 10.1088/1674-4926/34/1/015008

More Information

-

Abstract

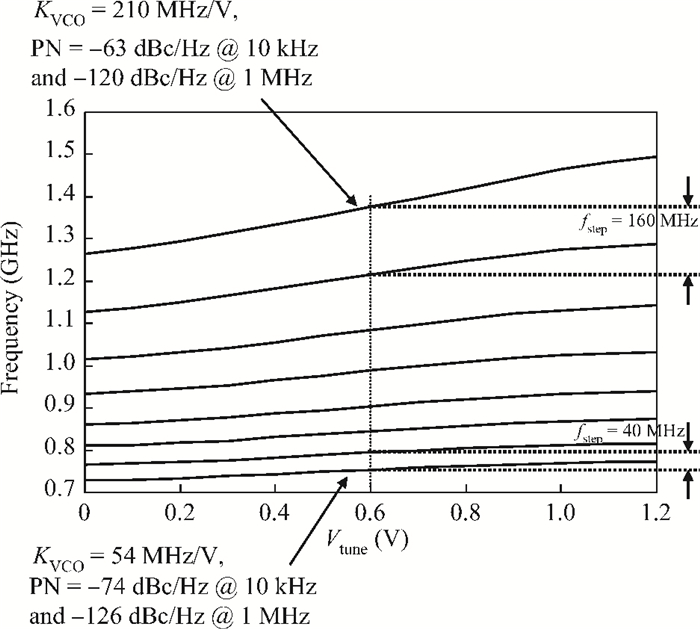

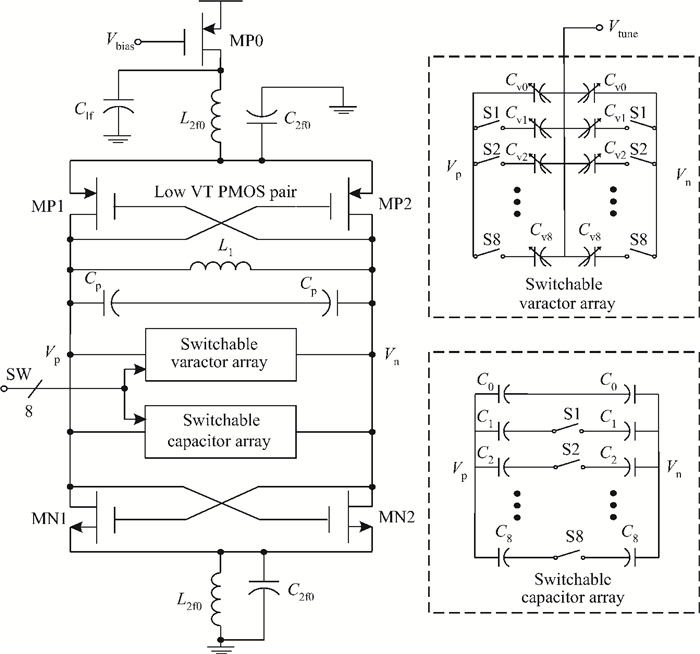

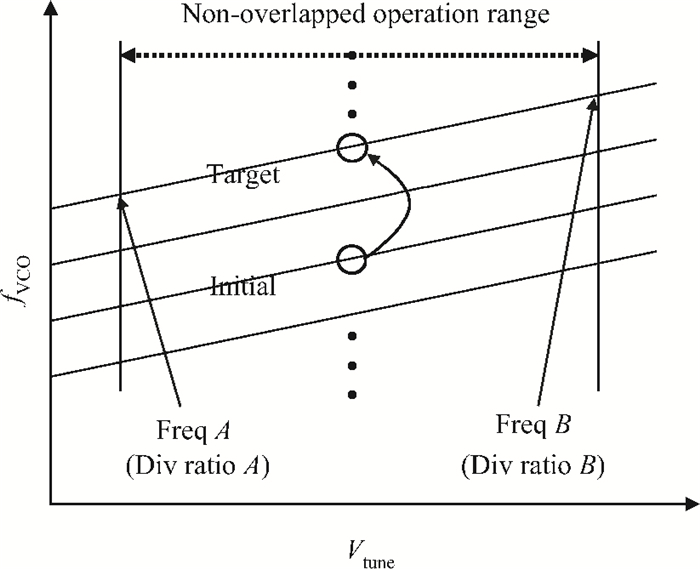

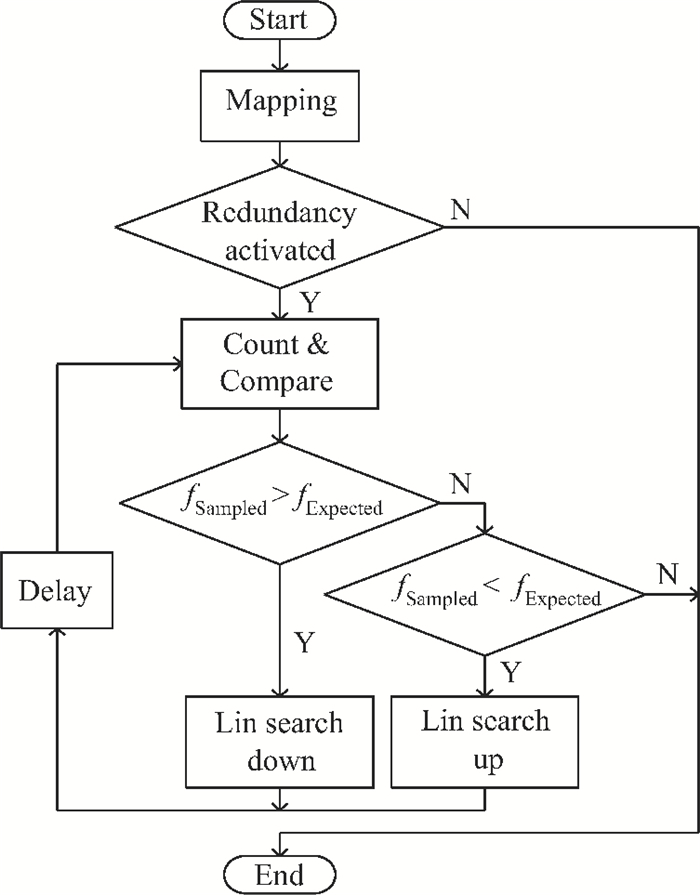

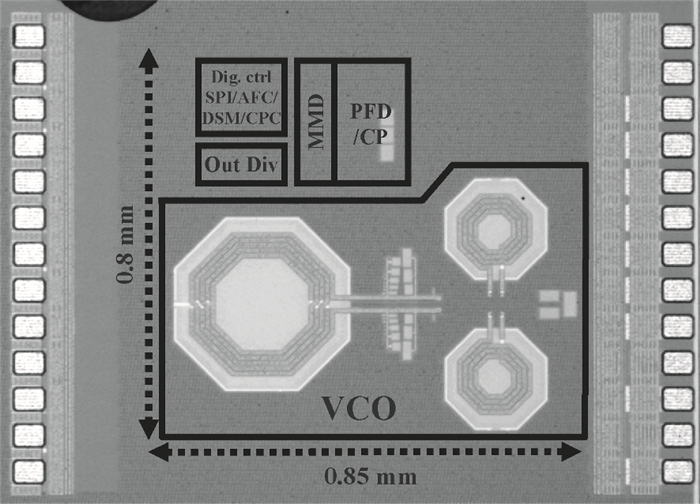

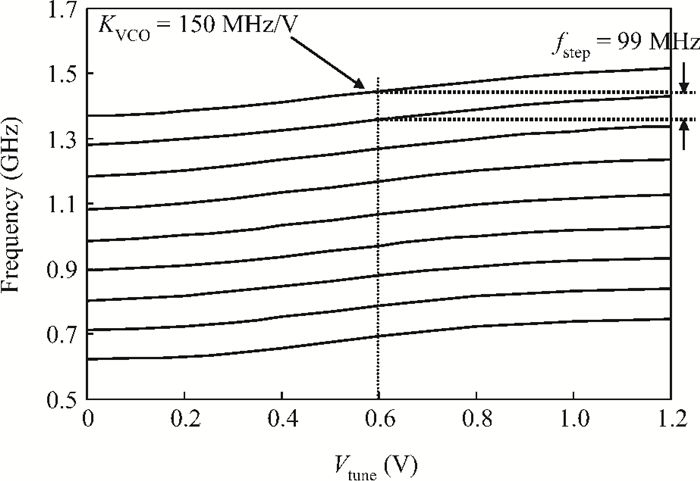

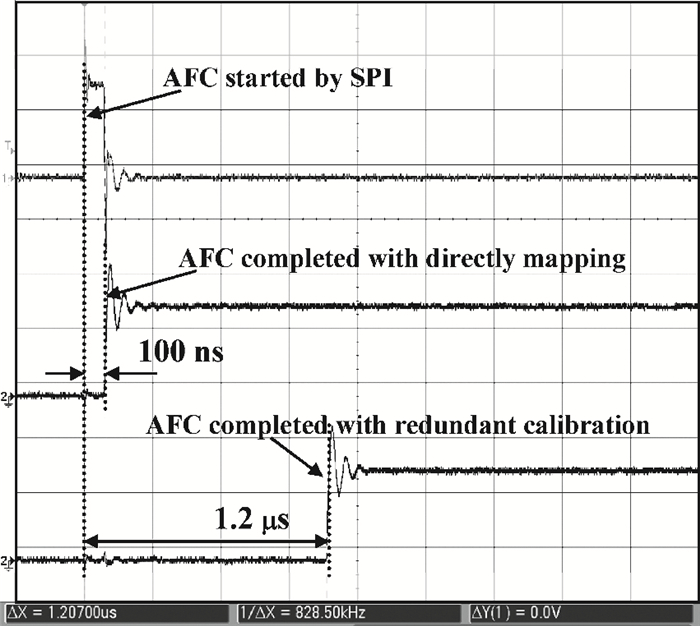

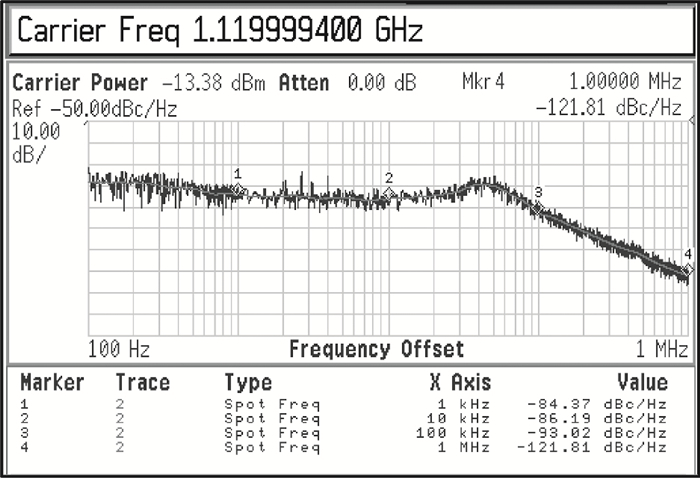

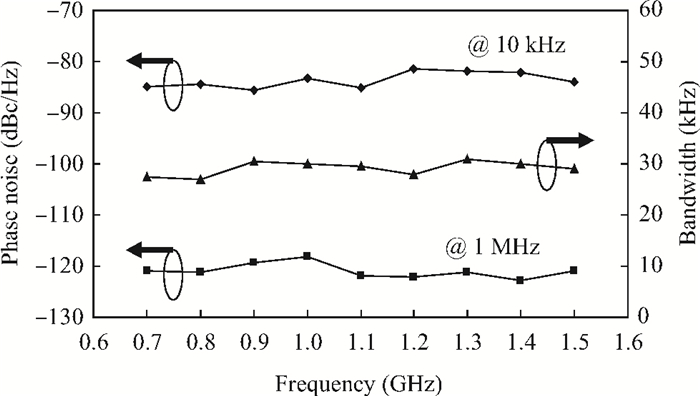

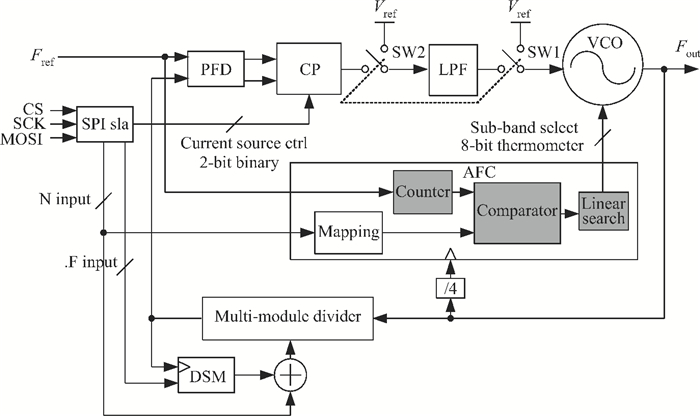

A wideband fractional-N frequency synthesizer is implemented in a 65 nm CMOS process. It employs a wideband LC voltage-controlled oscillator (VCO) with optimized VCO gain (KVCO) and a sub-band step to improve automatic frequency calibration (AFC) efficiency at negligible expense of phase noise performance. An agile AFC is realized by direct mapping based on the division ratio, and optional redundant counting and comparing calibration is introduced accommodating PVT variations, which samples the reference clock using the prescaled VCO output as a discriminating clock. A charge pump with switched charging current is adopted to compensate for the loop bandwidth variation. Measurement results show this directly-mapped AFC locates the target sub-band in 100 ns and only needs 1.2 μs for redundant calibration. The frequency synthesizer spans a frequency range from 0.62 to 1.52 GHz, with phase noise of-86 dBc/Hz at 10 kHz offset and-122 dBc/Hz at 1 MHz offset while consuming 9.76 mA from a 1.2 V supply.-

Keywords:

- frequency synthesizer,

- fractional-N,

- AFC,

- KVCO,

- bandwidth,

- CMOS

-

References

[1] Lin T H, Lai Y J. An agile VCO frequency calibration technique for a 10-GHz CMOS PLL. IEEE J Solid-State Circuits, 2007, 42(2):340 doi: 10.1109/JSSC.2006.889360[2] Hajimiri A, Lee T H. Design issues in CMOS differential LC oscillators. IEEE J Solid-State Circuits, 1999, 34(5):717 doi: 10.1109/4.760384[3] Moon Y J, Roh Y S, Jeong C Y, et al. A 4.39-5.26 GHz LC-tank CMOS voltage-controlled oscillator with small VCO-gain variation. IEEE Microw Wireless Compon Lett, 2009, 19(8):524 doi: 10.1109/LMWC.2009.2024846[4] Kim J, Shin J, Kim S, et al. A wide-band CMOS LC VCO with linearized coarse tuning characteristics. IEEE Trans Circuits Syst Ⅱ:Express Briefs, 2008, 55(5):399 doi: 10.1109/TCSII.2007.914896[5] Kondou M, Matsuda A, Yamazaki H, et al. A 0.3 mm2 90-to-770 MHz fractional-N synthesizer for a digital TV tuner. IEEE International Solid State Circuits Conf, 2010:248 http://ieeexplore.ieee.org/document/5302628/authors[6] Shin J, Shin H. A 1.9-3.8 GHz delta-Sigma fractional-N PLL frequency synthesizer with fast auto-calibration of loop bandwidth and VCO frequency. IEEE J Solid-State Circuits, 2012, 47(3):665 doi: 10.1109/JSSC.2011.2179733[7] Lee K S, Yu H, Ahn H K, et al. A 0.13-μm CMOS Σ-Δ frequency synthesizer with an area optimizing LPF, fast AFC time, and a wideband VCO for WCDMA/GSM/GPRS/EDGE applications. IEEE Radio Frequency Integrated Circuits Symp, 2008:299[8] Lee H I, Cho J K, Lee K S, et al. A sigma-delta fractional-N frequency synthesizer using a wide-band integrated VCO and a fast AFC technique for GSM/GPRS/WCDMA applications. IEEE J Solid-State Circuits, 2004, 39(7):1164 doi: 10.1109/JSSC.2004.829938[9] Jeong C Y, Choi D H, Yoo C. A fast automatic frequency calibration (AFC) scheme for phase-locked loop (PLL) frequency synthesizer. IEEE Radio Frequency Integrated Circuits Symp, 2009:583 http://ieeexplore.ieee.org/document/5135609/?reload=true&arnumber=5135609&punumber%3D5076160[10] Shin J, Shin H. A fast and high-precision VCO frequency calibration technique for wideband delta-Sigma fractional-N frequency synthesizers. IEEE Trans Circuits Syst I:Regular papers, 2010, 57(7):1573 doi: 10.1109/TCSI.2009.2036057[11] Yin Yadong, Yan Yuepeng, Liang Weiwei, et al. A fast lock frequency synthesizer using an improved adaptive frequency calibration. Journal of Semiconductors, 2010, 31(6):065011 doi: 10.1088/1674-4926/31/6/065011 -

Proportional views

DownLoad:

DownLoad: