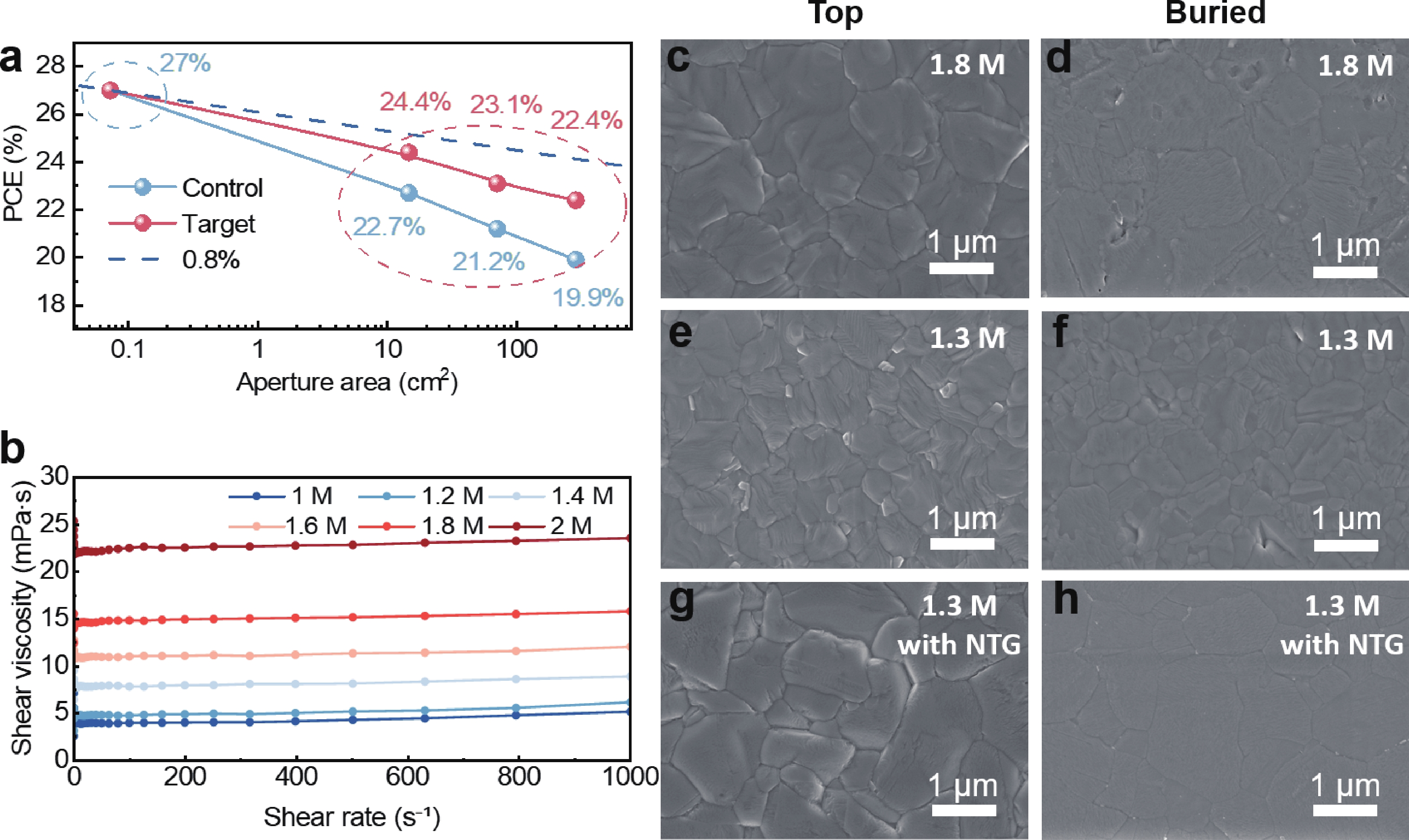

Large−area perovskite solar cell modules efficiency remains lower than small−area devices, perovskite crystallization between small and large areas difference could be one reason. Previously, diluted solution was often used to reduce viscosity to achieve uniform perovskite thin films, but this approach could narrow the crystallization window and leave insufficient time for controlled crystal growth. Meanwhile, insufficient solute supply often results in interrupted material availability for grain growth, leading to the formation of excessive small crystal nuclei and thus poor thin−film quality. Here, we developed a strategy that use a bi−functional group additive to stabilize the δ−FAPbI3 intermediate phase, which delays the direct and rapid conversion of lead iodide into α−FAPbI3 during large−area perovskite film growth. Based on this strategy, the efficiencies of perovskite modules with aperture areas of 14.6, 70.5, and 285.6 cm2 developed in this work are 24.4% (certified steady−state efficiency: 24.4%), 23.1%, and 22.4%, respectively. The efficiency loss per order−of−magnitude increase in area was reduced from 2.0% to 1.3%, which is approaching the state of the art of traditional thin−film CdTe solar cells (0.8%). In addition, the large−area module (155 cm2) retained 86% of its initial efficiency after 1,053 hours of maximum power point (MPP) tracking.

Just Accepted manuscripts are peer-reviewed and accepted for publication. They are posted online prior to technical editing formatting for publication and author proofing.

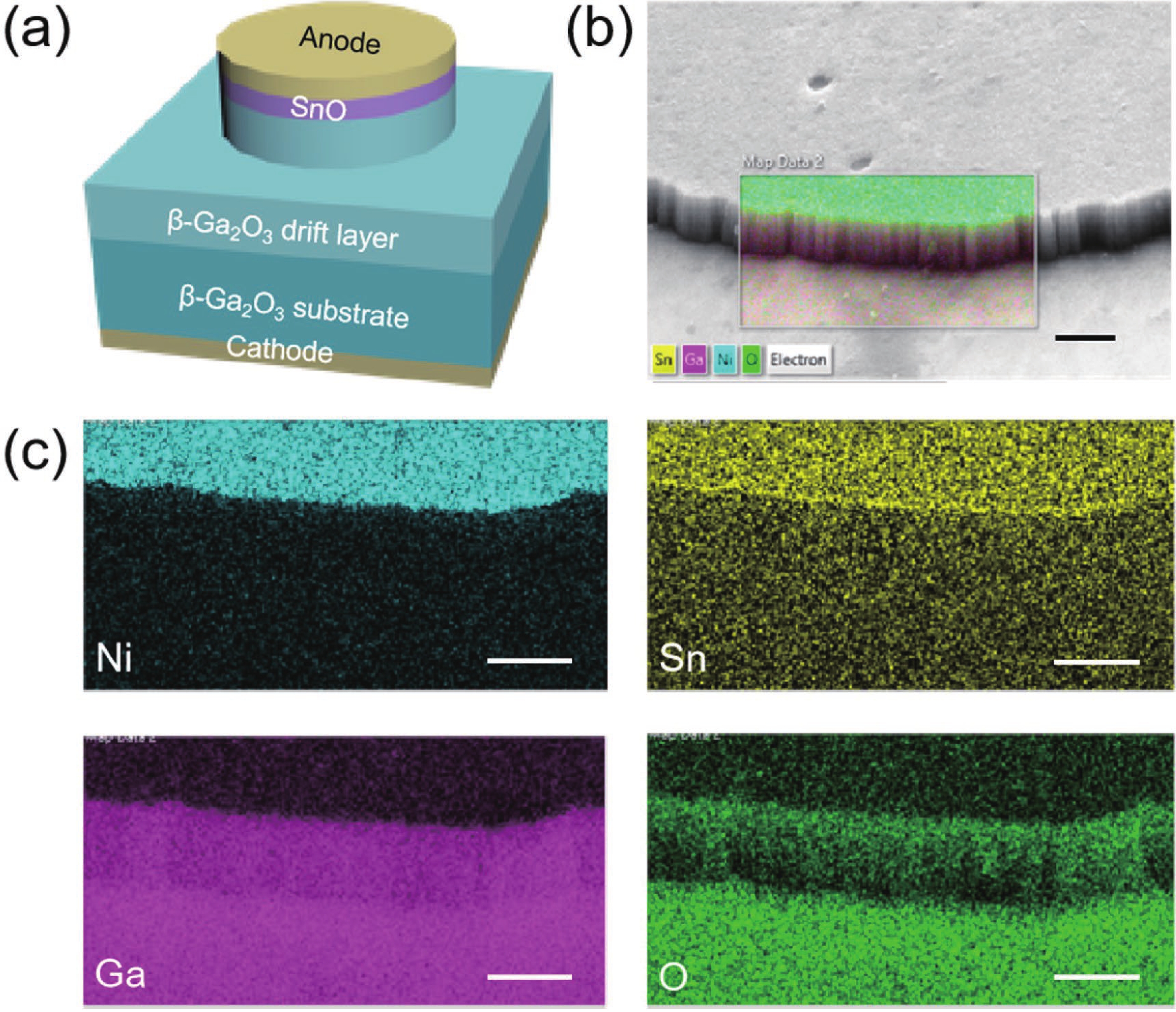

In this article, a vertical SnO/β-Ga2O3 mesa heterojunction diode (mesa-HJD) fabricated through self-aligned etching is reported. The mesa structure eliminates the influence of lateral depletion at the region, leading to an improved breakdown characteristics in comparison with its unterminated heterojunction diode (UT-HJD) counterpart. The SnO/β-Ga2O3 mesa-HJD, featuring a 500 nm mesa depth, achieves a breakdown voltage (BV) of 1100 V, which can be improved to 1631 V by sidewall passivation. With the increase of mesa depth, BV increases, accompanied by the increase of specific on-resistance (Ron,sp). Therefore, a maximum Baliga’s power figure of merit (PFOM) can be achieved for the optimized device with 500 nm mesa depth, giving the value of 0.93 GW/cm2 for the passivated device. The mesa-HJD demonstrates considerable potential for application in high BV β-Ga2O3 power electronic devices in the future.

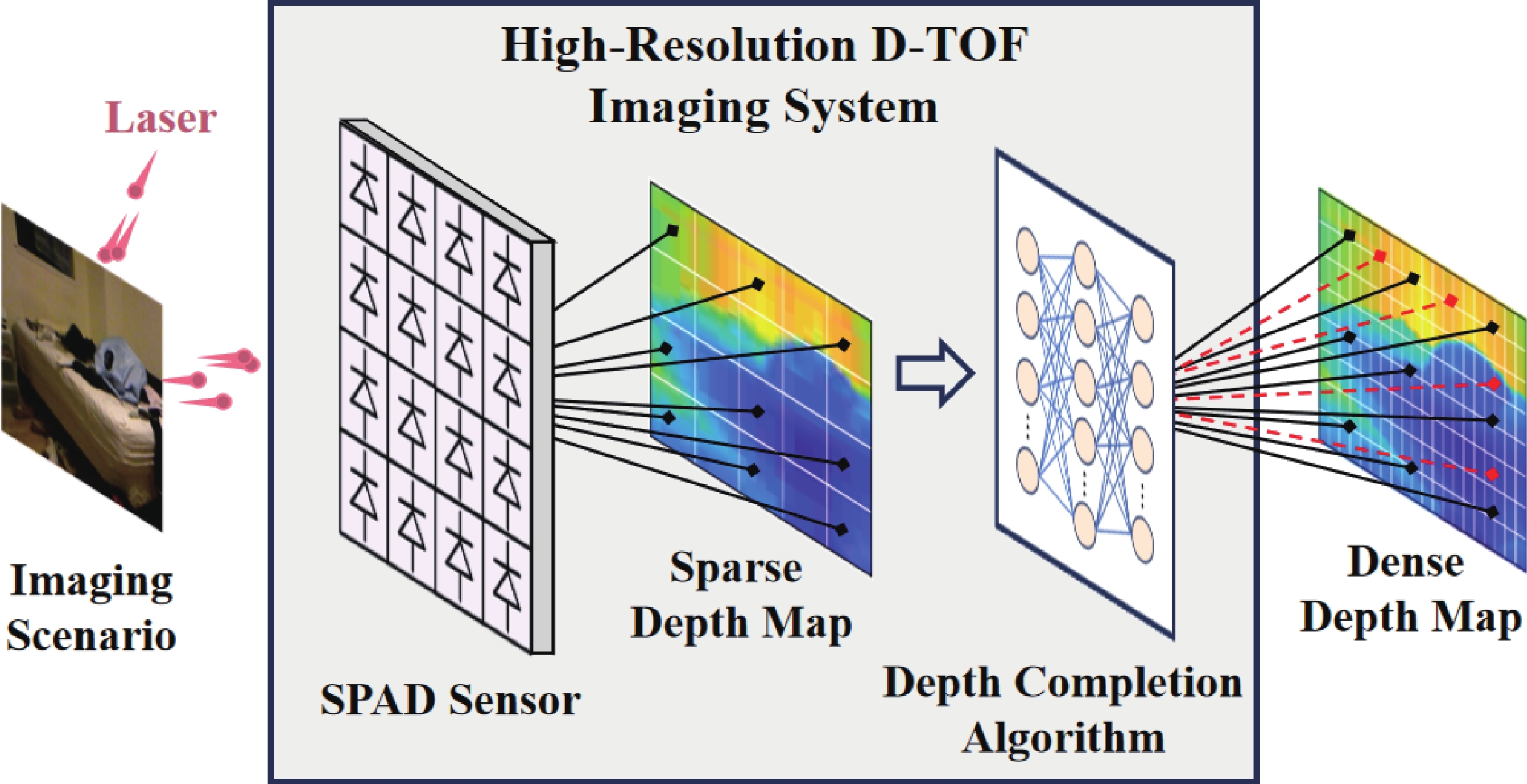

Single-photon avalanche diode (SPAD) image sensors are widely used in direct time-of-flight (D-TOF) imaging, but their ranging performance is often constrained by limited laser power. This article presents a SPAD-based D-TOF imaging system that combines a reconfigurable macro-pixel sensor architecture with a lightweight depth completion algorithm to achieve long-range depth imaging with enhanced spatial resolution under low optical power. The proposed sensor adopts a back-side illuminated (BSI) 3D-stacked architecture with programmable macro-pixels that enhance detection sensitivity and enable flexible sensitivity–resolution trade-offs. An injection-locked ring-oscillator-based time-to-digital converter (RO-TDC) array achieves a time resolution of 152.5 ps, enabling accurate TOF measurement at an optical power of 10 mW. To compensate for macro-pixel-induced resolution loss, a probabilistic normalized convolutional neural network (pNCNN) is employed for depth completion using sparse depth inputs only. Experimental results demonstrate that up to 30 × effective resolution enhancement of the system can be achieved via the depth completion algorithm without changing the physical resolution of the sensor. Additionally, the proposed system achieves a maximum ranging distance of 90 m and a range-to-power figure-of-merit (FOM) of 9 m/mW, which validates the effectiveness of the system.

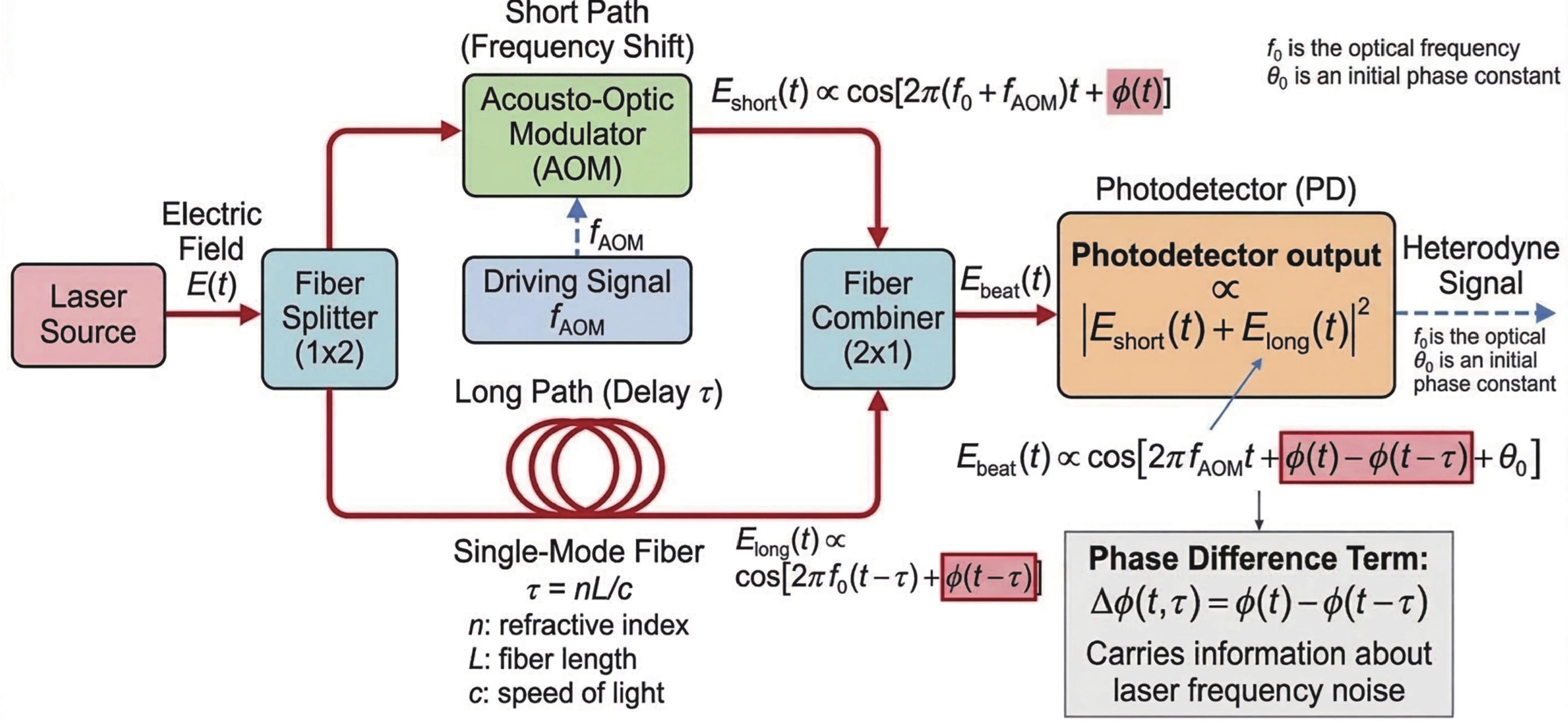

Systematic optimization of the delayed self-heterodyne method for laser frequency noise characterization is investigated across an extensive linewidth range (100 Hz to 10 MHz). By evaluating various fiber lengths, window functions, and five demodulation algorithms, we identify a critical trade-off: long fibers enhance sensitivity for narrow-linewidth lasers but exacerbate spectral leakage in broad-linewidth sources. Our findings demonstrate that Hanning and Blackman windows effectively suppress this leakage, ensuring measurement consistency across different delay lengths. Among the evaluated algorithms, the Hilbert transform offers the superior balance of high-frequency accuracy and computational efficiency. Validated under low-power conditions, this optimized framework provides a robust and power-independent methodology for precise FN analysis, offering significant guidance for high-performance laser development.

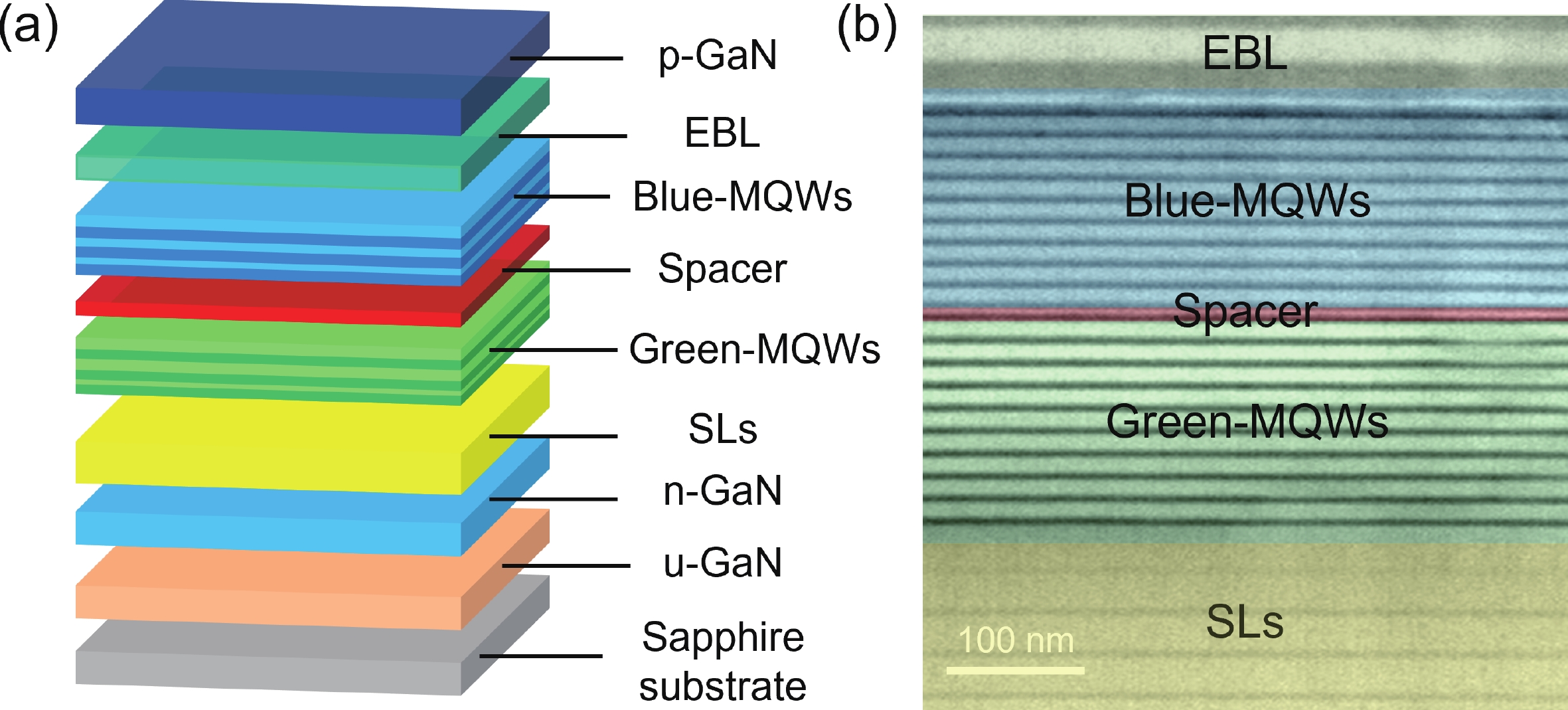

III-nitride semiconductors with continuously tunable bandgaps are promising for white light emission and full-color displays. The mainstream RGB LED integration approach suffers from low long-wavelength efficiency and complex packaging. Herein, we demonstrate a novel single-chip dual-wavelength LED structure, which integrates blue (upper) and green (bottom) multiple quantum wells (MQWs) separated by a GaN intermediate spacer layer. The device exhibits two distinct emission peaks at 446 and 528 nm, with excellent luminescence stability. We investigate the role of the spacer layer and reveal its critical effect on the carrier distribution and radiative recombination behavior. The maximum wall-plug efficiency (WPE) of the device reaches approximately 36.7%, and its abnormal droop curve indicates a transition of the green emission mechanism from electroluminescence (EL) to photoluminescence (PL). By tuning the injection current, the dual-wavelength LED achieves a continuous color transition from green to blue, which corresponds to chromaticity coordinates ranging from (0.2584, 0.7098) to (0.1771, 0.2649) in the CIE 1931 chromaticity diagram. This work provides a feasible and flexible strategy for emission color modulation, and also lays a foundation for the development of high-performance solid-state lighting devices.

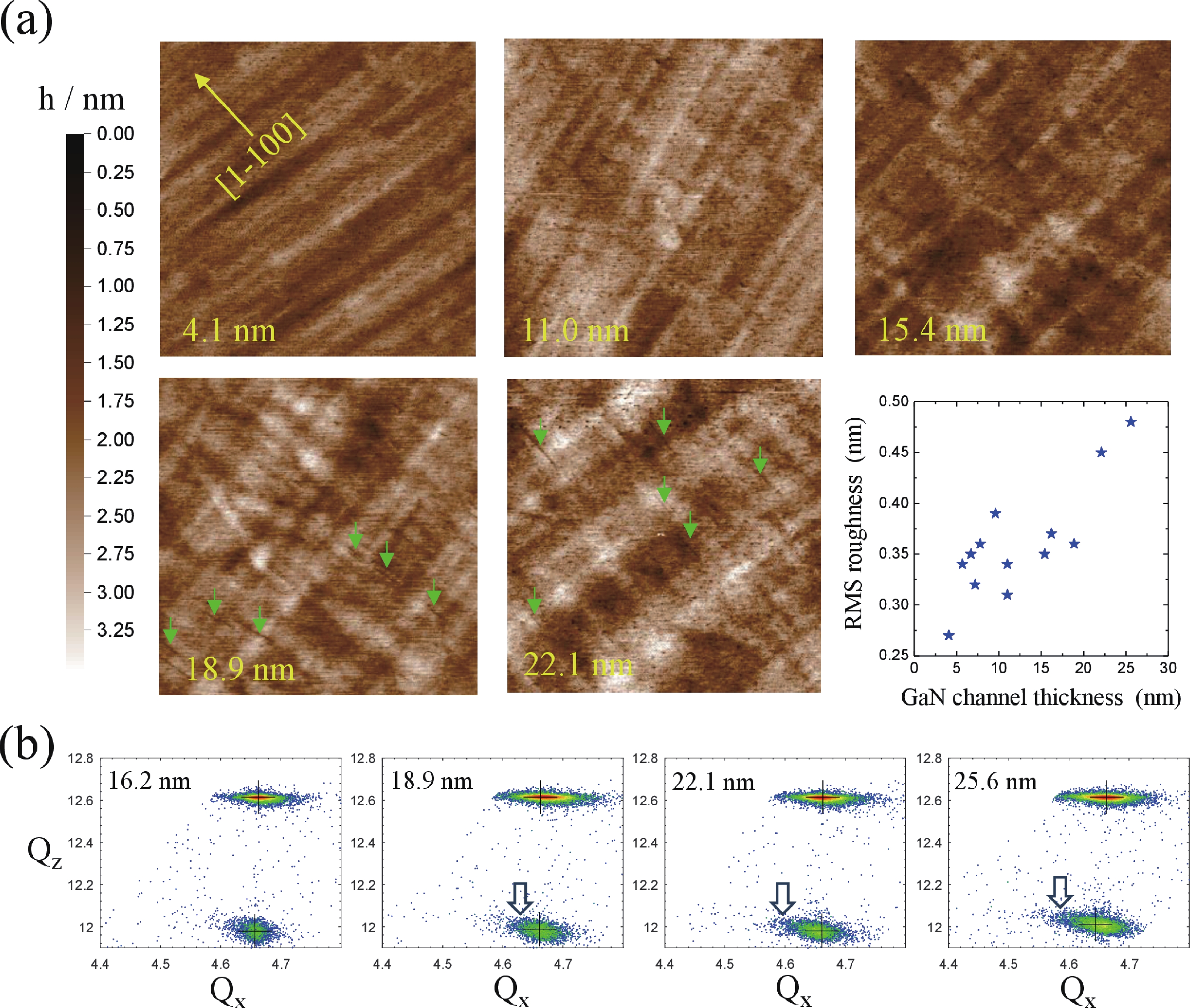

We have systematically studied the impact of thickness on the electrical properties of thin GaN channels on N-polar AlN (0001) templates grown on sapphire. The observed increase in sheet carrier density with increasing GaN thickness can be quantitatively reproduced by calculations assuming a Fermi-level pinning about 0.8 eV below the conduction band. The mobility strongly increases until 6 nm which correlates with reduced overlap of the 2DEG wave function with the surface layer. The mobility then increases more gradually up to 10 nm, corresponding to a reduced fraction of the 2DEG within the first 0.5 nm near the AlN/GaN interface, namely, the region affected by interface roughness. The mobility saturates at approximately 400 cm2·V−1·s−1, probably limited by dislocations and the overlap with deep traps inside the AlN back barrier. If the GaN thickness exceeds 15 nm, the mobility decreases, likely due to the onset of gradual relaxation and appearance of misfit dislocations. Finally, we note that the temperature-dependent mobility exhibits an unexpected contribution proportional to $ T^{-2} $ for all GaN channels on N-polar AlN, including those reported in the literature. Such observation may be explained by a 50% higher effective mass of the electron, which amplify the electron-phonon scattering, ultimately limiting the room-temperature mobility to about 750 cm2·V−1·s−1 and confining the sheet resistivity to values above 200 Ω/□.

The integration of proximity sensing into flexible tactile electronic skins (e-skins) represents a fundamental shift from conventional contact-only interfaces toward anticipatory perception systems. This mini-review provides a systematic examination of recent advances in proximity-augmented e-skins, which overcome the inherent latency of tactile sensors by extending sensory awareness into the pre-contact domain. We provide a comprehensive overview of five key sensing modalities—capacitive, triboelectric, magnetic, temperature-based, and humidity-based—detailing their operating principles, material innovations, and structural optimization strategies. System-level requirements for practical deployment are also critically analyzed. Representative applications in interactive surfaces, human–robot collaboration, soft robotics, healthcare monitoring, and integrated multifunctional e-skins are highlighted to illustrate the transformative potential of this technology. Despite substantial progress, challenges persist in seamless multimodal integration, scalable manufacturing, and intelligent data fusion. Future directions are discussed to realize robust, perceptually intelligent e-skins that bridge the gap between laboratory innovations and real-world applications.