| Citation: |

Hua Fan, Xue Han, Qi Wei, Huazhong Yang. An 11-bit ENOB, accuracy-programmable, and non-calibrating time-mode SAR ADC[J]. Journal of Semiconductors, 2013, 34(1): 015010. doi: 10.1088/1674-4926/34/1/015010

****

H Fan, X Han, Q Wei, H Z Yang. An 11-bit ENOB, accuracy-programmable, and non-calibrating time-mode SAR ADC[J]. J. Semicond., 2013, 34(1): 015010. doi: 10.1088/1674-4926/34/1/015010.

|

An 11-bit ENOB, accuracy-programmable, and non-calibrating time-mode SAR ADC

DOI: 10.1088/1674-4926/34/1/015010

More Information

-

Abstract

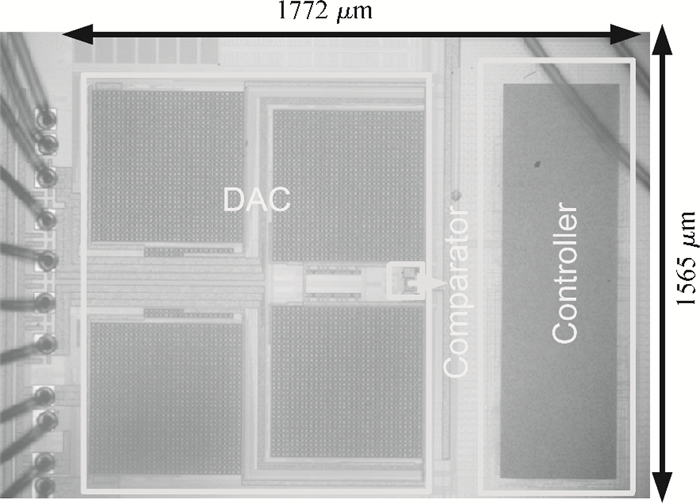

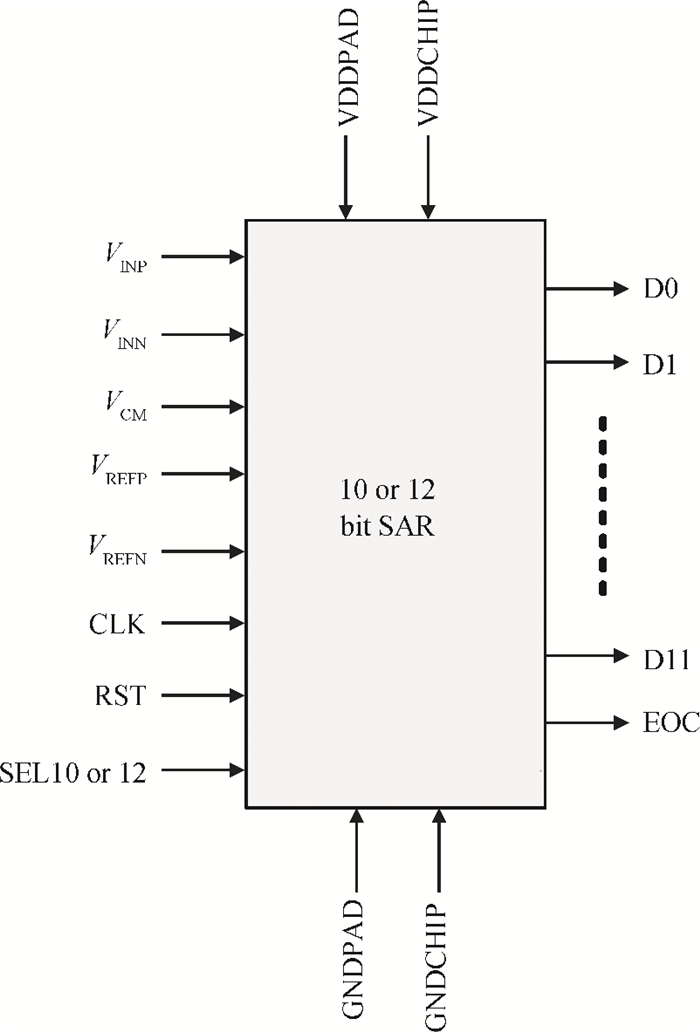

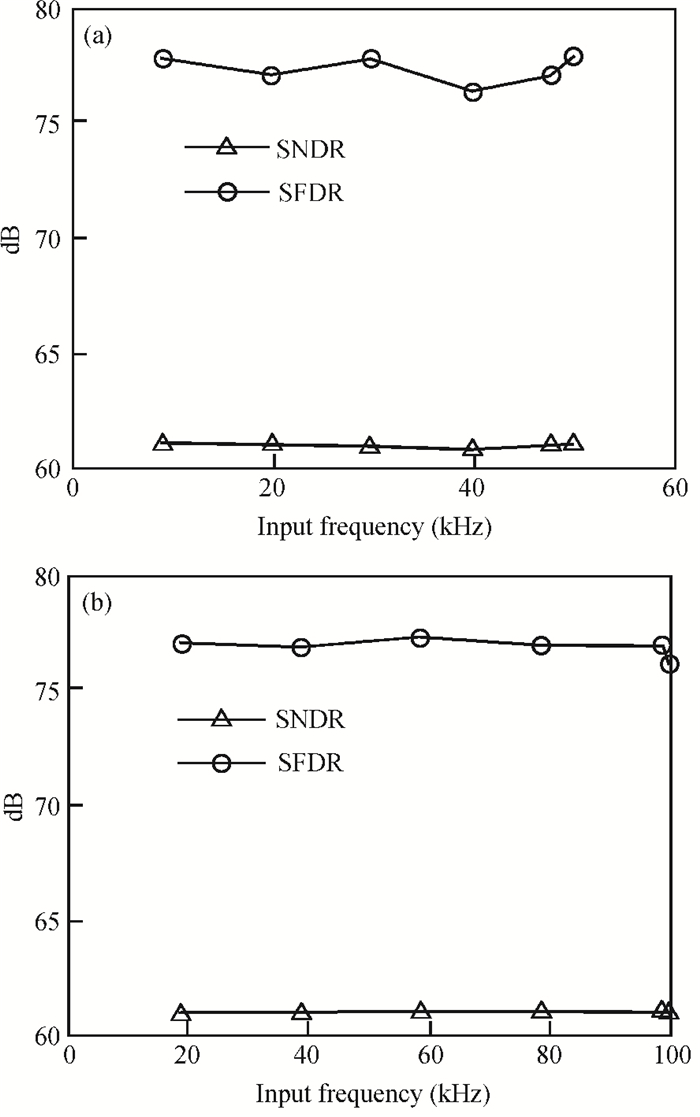

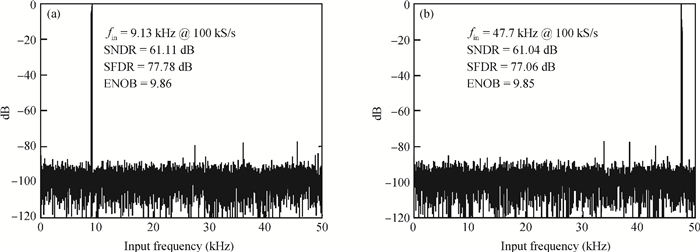

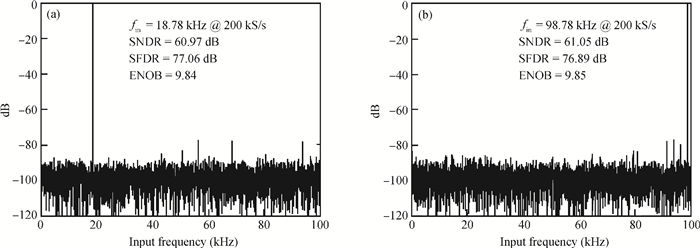

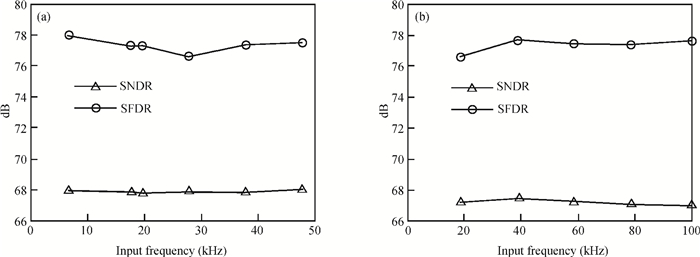

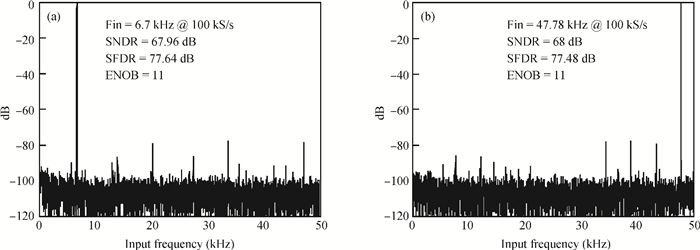

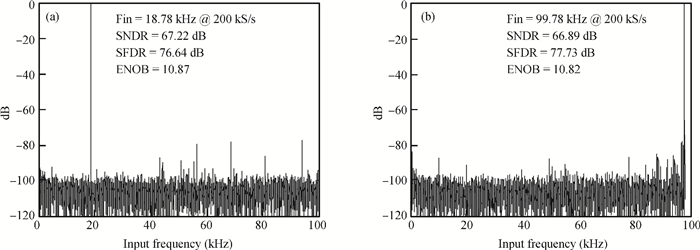

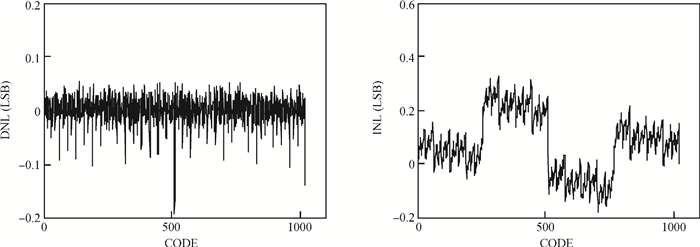

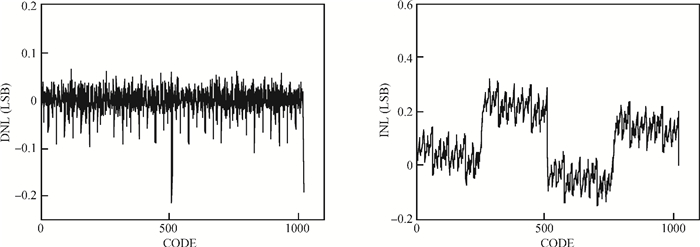

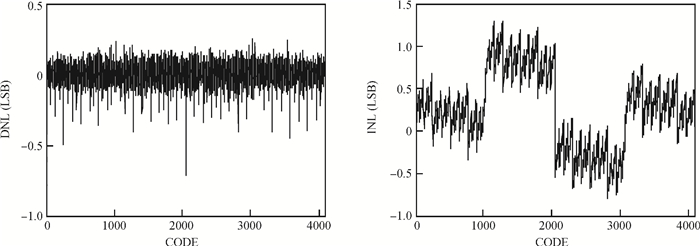

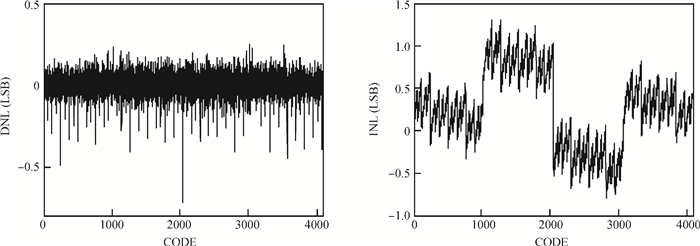

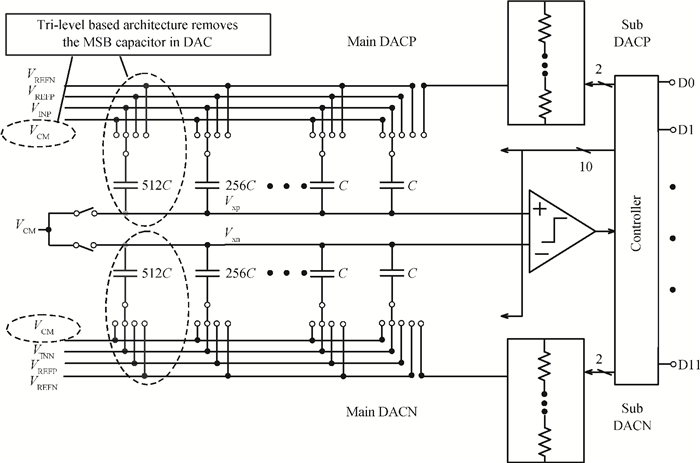

A 10 or 12 bit programmable successive approximation register (SAR) ADC incorporating improved time-domain comparator for bridge stress monitoring systems is presented. Techniques for improving the accuracy of time-domain comparator are presented. The application of these approaches is illustrated using results from an experimental 10 or 12 bit programmable SAR ADC. Prototyped in a 0.18-μm, 6M1P CMOS process, the ADC, at 12 bit, 100 kS/s, achieves a Nyquist signal-to-noise-plus-distortion ratio (SNDR) of 68 dB (11 ENOB), a spurious free dynamic range (SFDR) of 77.48 dB, while dissipating 558 μW from a 1.8-V supply. Its differential nonlinearity (DNL) and integral nonlinearity (INL) are 0.2/-0.74 LSB and +1.27/-0.97 LSB, respectively. -

References

[1] Shikata A, Sekimoto R, Kuroda T, et al. A 0.5 V 1.1 MS/sec 6.3 fJ/conversion-step SAR-ADC with tri-level comparator in 40 nm CMOS. IEEE J Solid-State Circuits, 2012, 47(4):1022 doi: 10.1109/JSSC.2012.2185352[2] Liu C C, Chang S J, Huang G Y, et al. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J Solid-State Circuits, 2010, 45(4):731 doi: 10.1109/JSSC.2010.2042254[3] Cho S H, Lee C K, Kwon J K, et al. A 550-μW 10-bit 40-MS/s SAR ADC with multistep addition-only digital error correction. IEEE J Solid-State Circuits, 2011, 46(8):1881 doi: 10.1109/JSSC.2011.2151450[4] Zhu Y, Chan C H, Chio U F, et al. A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J Solid-State Circuits, 2010, 45(5):1111 http://ieeexplore.ieee.org/document/5482529/?reload=true&arnumber=5482529&sortType%3Dasc_p_Sequence%26filter%3DAND(p_IS_Number:5482512)[5] Cho T S, Lee K J, Kong J, et al. A 32-μW 1.83-kS/s carbon nanotube chemical sensor system. IEEE J Solid-State Circuits, 2009, 44:2348 doi: 10.1109/JSSC.2009.2023158[6] Van Elzakker M, Van Tuijl E, Geraedts P, et al. A 1.9μW 4.4 fJ/conversion-step, 10 bit, 1 MS/s charge redistribution ADC. IEEE International Solid-State Circuits Conference (ISSCC), 2008:244 https://zh.scribd.com/doc/151430867/Solving-problems-with-NMR-pdf[7] Chen Y, Tsukamoto S, Kuroda T. A 9 b 100 MS/s 1.46 mW SAR ADC in 65 nm CMOS. IEEE Asian Solid-State Circuits Confer-ence (ASSCC), 2009:145 http://ieeexplore.ieee.org/document/5357199/?reload=true&arnumber=5357199&sortType%3Dasc_p_Sequence%26filter%3DAND(p_IS_Number:5357143)%26pageNumber%3D3[8] Hamade A R. A single chip all-MOS 8-bit A/D converter. IEEE J Solid-State Circuits, 1981, SC-13:785 http://ieeexplore.ieee.org/document/1052051/[9] Zhu Y, Chan C H, Chio U F, et al. Parasitics nonlinearity cancellation technique for split DAC architecture by using capacitive charge-pump. IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), 2010:889 doi: 10.1007/s10470-012-9977-6[10] Kuramochi Y, Matsuzawa K, Kawabata M. A 0.027-mm2 self-calibrating successive approximation ADC core in 0.18-μm CMOS. IEICE Trans, Fundamentals, 2009, E92-A(2):360 doi: 10.1587/transfun.E92.A.360[11] Gambini Si, Rabaey J M. Low voltage analog to digital converter design in 90 nm CMOS. Technical Report No.UCB/EECS-2007-17, Berkeley, 2007[12] Agnes A, Bonizzoni E, Maicovati P, et al. A 9.4-ENOB 1 V 3.8μW 100 kS/s SAR ADC with time-domain comparator. IEEE International Solid-State Circuits Conference (ISSCC), 2008, 51:246 https://www.researchgate.net/publication/4332071_A_94-ENOB_1V_38mW_100kSs_SAR_ADC_with_Time-Domain_Comparator[13] Lee S K, Park S J, Park H J, et al. A 1.3μW 0.6 V 8.7-ENOB successive approximation ADC in a 0.18μm CMOS. Symposium on VLSI Circuits Digest of Technical Papers, 2009:242[14] Nuzzo P, De Bernardinis F, Terreni P, et al. Noise analysis of regenerative comparators for reconfigurable ADC architectures. IEEE Trans Circuit Syst I:Fundamental Theory and Applications, 2008, 55(6):1441 doi: 10.1109/TCSI.2008.917991[15] Micheva N I. Design port and optimization of a high-speed SAR ADC comparator from 65 nm to 0.11μm. Master Thesis of MIT, 2011:44 https://zh.scribd.com/document/245501847/Iccter-Proceedings[16] Kobenge S B, Yang H. A novel low power time-mode comparator for successive approximation register ADC. IEICE Electronics Express, 2009, 6(16):1155 doi: 10.1587/elex.6.1155[17] Van der Plas G, Decoutere S, Donnay S. A 0.19 pJ/conversion-step 2.5 mW 1.25 GS/s 4 b ADC in a 90 nm digital CMOS process. IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2008:556 doi: 10.1007/s10470-013-0156-1?view=classic[18] Behzad R. Design of analog CMOS integrated circuits. International Edition, 2001 http://catalog.lib.kyushu-u.ac.jp/recordID/1001200565[19] Ali A M A, Dillon C, Sneed R, et al. A 14-bit 125 MS/s IF/RF sampling pipelined ADC with 100 dB SFDR and 50 fs jitter. IEEE J Solid-State Circuits, 2006, 41(8):1846 doi: 10.1109/JSSC.2006.875291[20] Analog Devices. Low power, pseudo differential, 100 ksps 12-bit ADC in an 8-lead SOT-23. AD7457, 2005 doi: 10.1007/s10470-012-9977-6[21] ZMDI. 12-bit, 200 ksps, 8-channel, serial output ADC datasheet. ZADCS146, 2010 doi: 10.1007/s10470-012-9977-6[22] Chiang C T, Chang W H. A 12-bit multi-channel dual-mode successive approximation ADC for power management bus (Pmbus) devices. International Journal of Circuit Theory and Applications, 2011(Published online in Wiley Interscience (www.Interscience.wiley.com). DOI: 10.1002/cta.811)[23] Wang Z, Lin R, Gordon E, et al. An in-situ temperature-sensing interface based on a SAR ADC in 45 nm LP digital CMOS for the frequency-temperature compensation of crystal oscillators. IEEE International Solid-State Circuits Conference (ISSCC), 2010:316 doi: 10.1007/s10470-014-0298-9/fulltext.html[24] Verma N, Chandrakasan A P. An ultra low energy 12-bit rate-resolution scalable SAR ADC for wireless sensor nodes. IEEE J Solid-State Circuits, 2007, 42(6):1196 doi: 10.1109/JSSC.2007.897157[25] Ueda Y, Yamauchi H, Mukuno M, et al. 6.33 mW MPEG audio decoding on a multimedia processor. IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2006:414 http://ieeexplore.ieee.org/document/1696218/authors[26] Jiang T, Liu W, Zhong F Y, et al. Single-channel, 1.25-GS/s, 6-bit, loop-unrolled asynchronous SAR-ADC in 40 nm-CMOS. IEEE Custom Integrated Circuits Conference (CICC), 2010:1 http://ieeexplore.ieee.org/document/5617411/keywords[27] Chen S W M, Brodersen R W. A 6-bit 600-MS/s 5.3 mW asynchronous ADC in 0.13-μm CMOS. IEEE J Solid-State Circuits, 2006, 41(12):2669 doi: 10.1109/JSSC.2006.884231 -

Proportional views

DownLoad:

DownLoad: