| Citation: |

Mingyi Chen, Xiaojie Chu, Peng Yu, Jun Yan, Yin Shi. A 55 nm CMOS ΔΣ fractional-N frequency synthesizer for WLAN transceivers with low noise filters[J]. Journal of Semiconductors, 2013, 34(10): 105001. doi: 10.1088/1674-4926/34/10/105001

****

M Y Chen, X J Chu, P Yu, J Yan, Y Shi. A 55 nm CMOS ΔΣ fractional-N frequency synthesizer for WLAN transceivers with low noise filters[J]. J. Semicond., 2013, 34(10): 105001. doi: 10.1088/1674-4926/34/10/105001.

|

A 55 nm CMOS ΔΣ fractional-N frequency synthesizer for WLAN transceivers with low noise filters

DOI: 10.1088/1674-4926/34/10/105001

More Information

-

Abstract

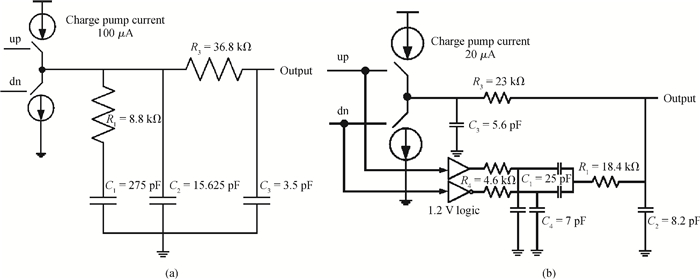

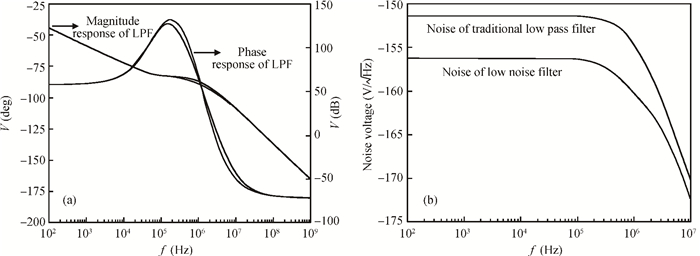

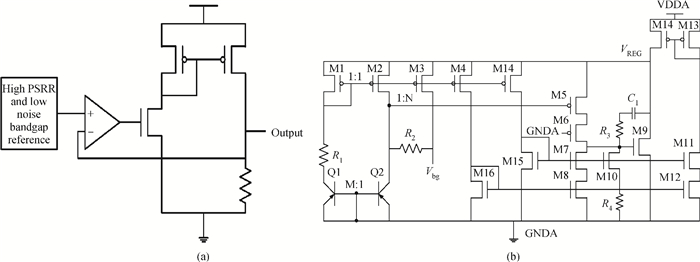

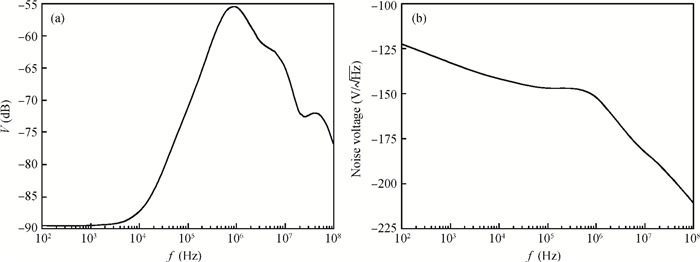

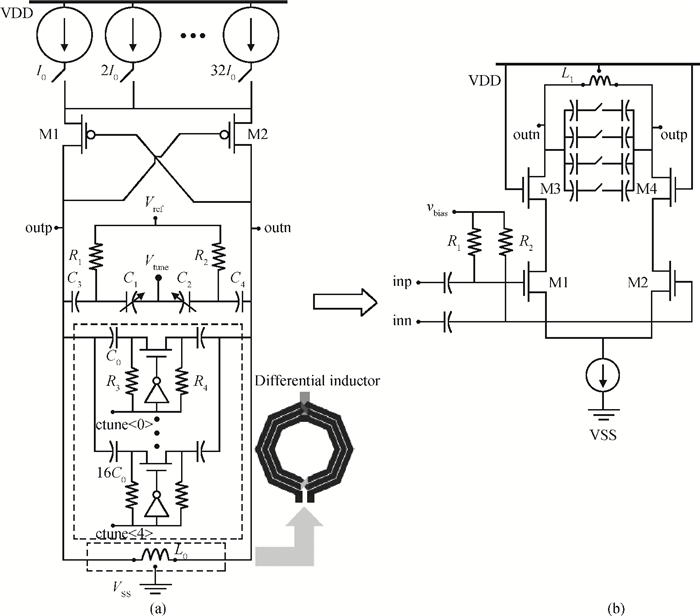

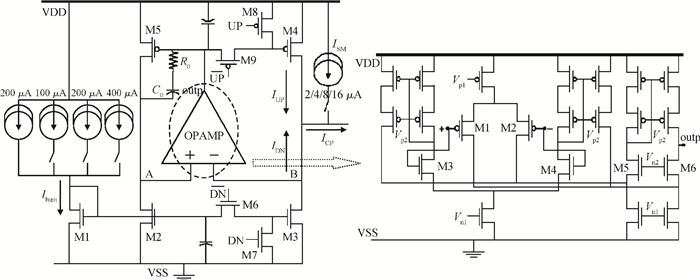

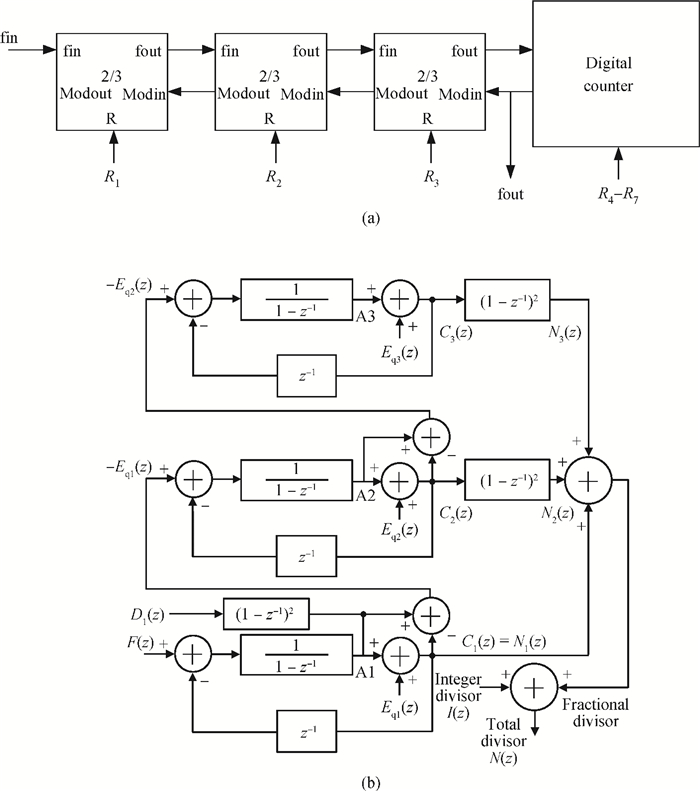

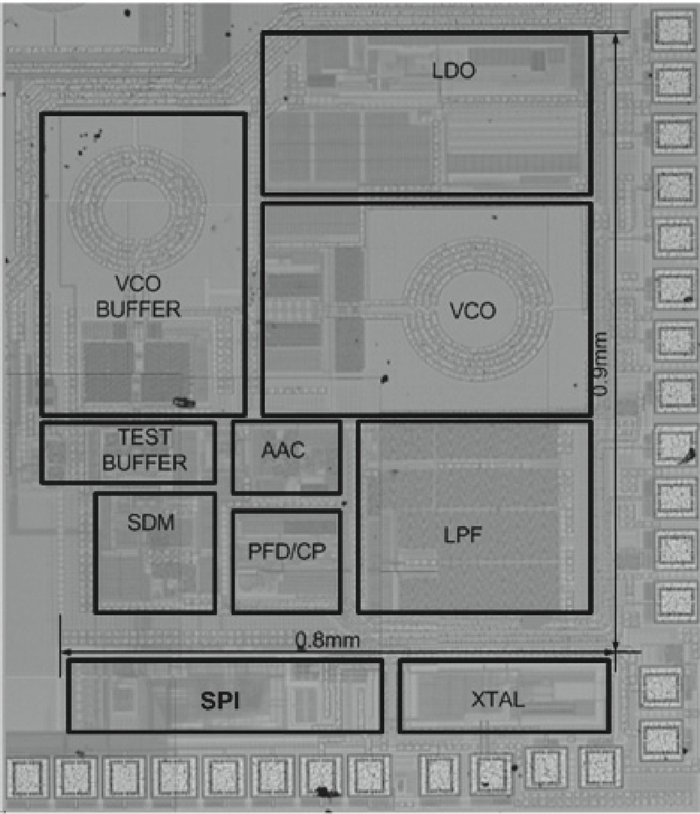

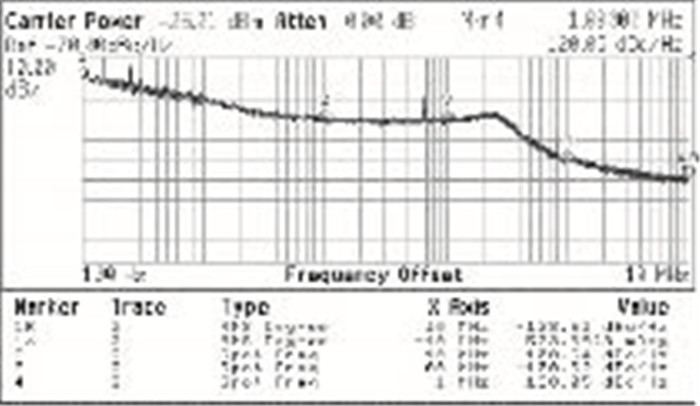

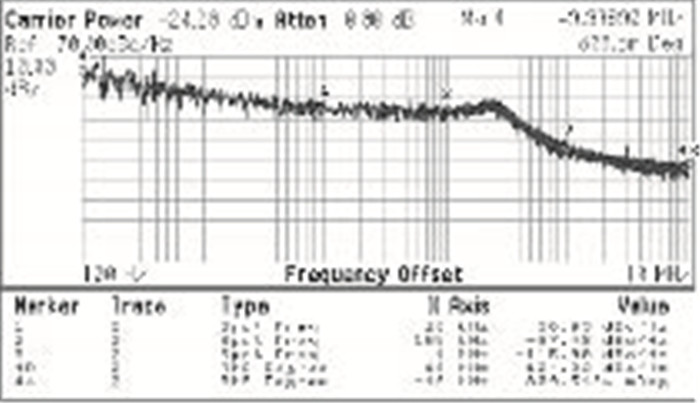

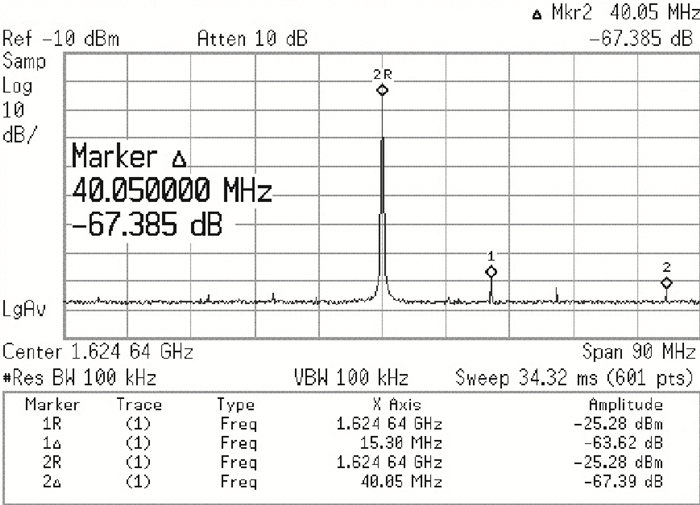

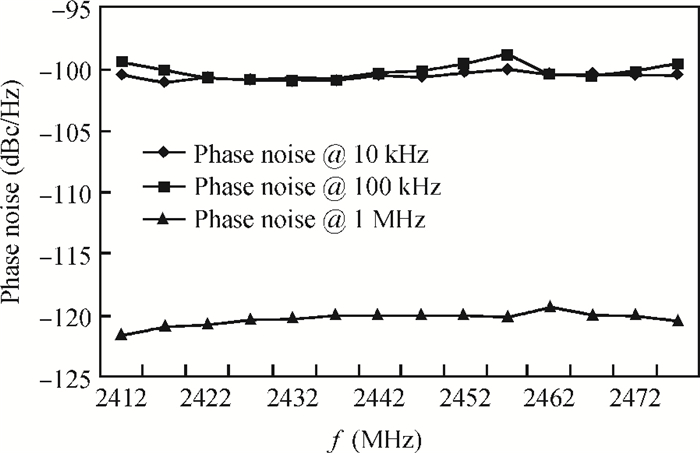

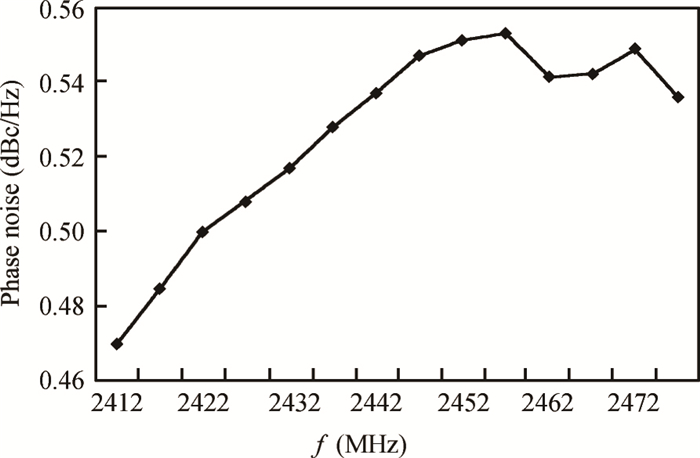

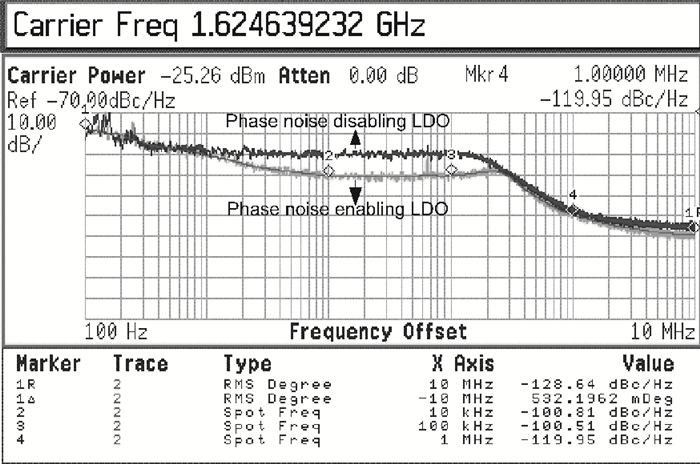

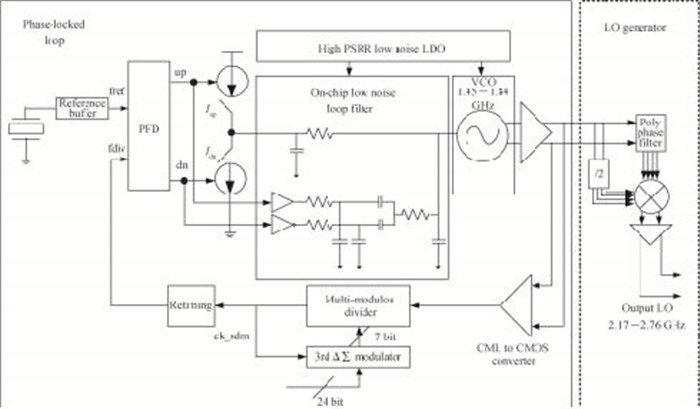

A fully integrated Δ Σ fractional-N frequency synthesizer fabricated in a 55 nm CMOS technology is presented for the application of IEEE 802.11b/g wireless local area network (WLAN) transceivers. A low noise filter, occupying a small die area, whose power supply is given by a high PSRR and low noise LDO regulator, is integrated on chip. The proposed synthesizer needs no off-chip components and occupies an area of 0.72 mm2 excluding PAD. Measurement results show that in all channels, the phase noise of the synthesizer achieves -99 dBc/Hz and -119 dBc/Hz in band and out of band respectively with a reference frequency of 40 MHz and a loop bandwidth of 200 kHz. The integrated RMS phase error is no more than 0.6°. The proposed synthesizer consumes a total power of 15.6 mW. -

References

[1] Jones C G, Beghein C C. Low noise filter. US Patent, No. 6891412 B1, 2005[2] Tham K M, Nagaraj K. A low supply voltage high PSRR voltage reference in CMOS process. IEEE J Solid-State Circuits, 1995, 30(5):586 doi: 10.1109/4.384173[3] Jian H Y, Xu Z, Wu Y C, et al. A fractional-N PLL for multiband (0.8-6 GHz) communications using binary-weighted D/A differentiator and offset-frequency Δ-Σ modulator. IEEE J Solid-State Circuits, 2010, 45(4):768 https://www.infona.pl/resource/bwmeta1.element.ieee-art-000005437492[4] Kondou M, Matsuda A, Yamazaki H, et al. A 0.3 mm2 90-to-770 MHz fractional synthesizer for a digital TV tuner. International Solid-State Circuits Conference, 2010:247 http://ieeexplore.ieee.org/document/5433939/[5] Shin J, Shin H. A 1.9-3.8 GHz ΔΣ fractional-N PLL frequency synthesizer with fast auto-calibration of loop bandwidth and VCO frequency. IEEE J Solid-State Circuits, 2012, 47(3):665 http://ieeexplore.ieee.org/Xplore/home.jsp -

Proportional views

DownLoad:

DownLoad: