| Citation: |

Meng Yu, Lipeng Wu, Fule Li, Zhihua Wang. An 8 bit 12 MS/s asynchronous successive approximation register ADC with an on-chip reference[J]. Journal of Semiconductors, 2013, 34(2): 025010. doi: 10.1088/1674-4926/34/2/025010

****

M Yu, L P Wu, F L Li, Z H Wang. An 8 bit 12 MS/s asynchronous successive approximation register ADC with an on-chip reference[J]. J. Semicond., 2013, 34(2): 025010. doi: 10.1088/1674-4926/34/2/025010.

|

An 8 bit 12 MS/s asynchronous successive approximation register ADC with an on-chip reference

DOI: 10.1088/1674-4926/34/2/025010

More Information

-

Abstract

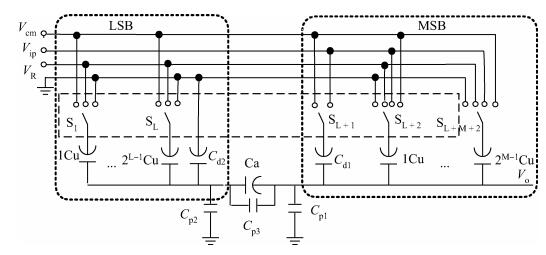

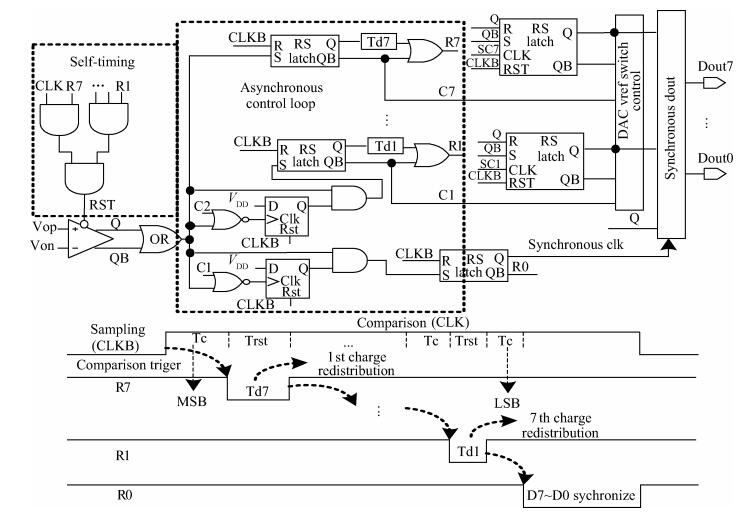

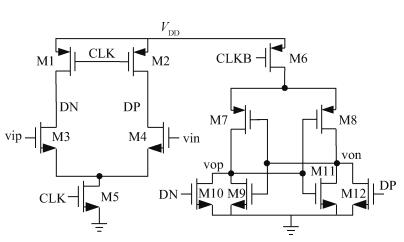

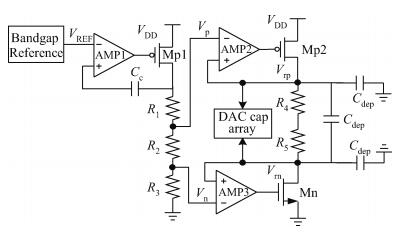

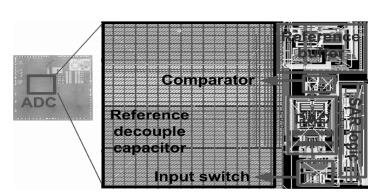

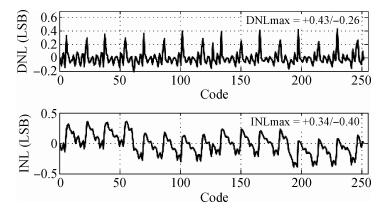

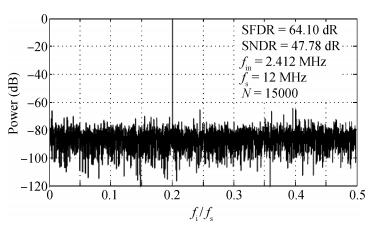

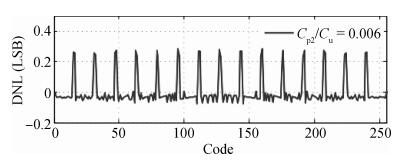

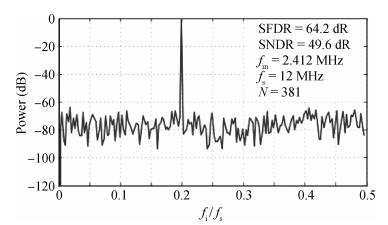

This paper proposes an 8 bit asynchronous successive approximation register ADC for wireless transceivers. A split capacitor DAC is used to reduce power and area consumption and the value of the split capacitor is calculated theoretically to ensure linearity. Asynchronous control logic is proposed to eliminate the high internal clocks and significantly speeds up the successive approximation algorithm. An on-chip reference with a fully integrated buffer and decoupling capacitor is adopted for avoiding an extra pin for the off-chip reference. The prototype, fabricated in UMC 0.18 μm CMOS technology, achieves an effective number of bits of 7.64 bits at a sampling frequency of 12 MS/s. The total power consumption is 0.918 mW for a 1.8 V supply, while the on-chip reference consumes 53% of the total power. It achieves a figure of merit of 180 fJ/conv·step, excluding the reference's power consumption. -

References

[1] Mesgarani A. A single channel 6-bit 900 MS/s 2-bits per stage asynchronous binary search ADC. IEEE 54th International Midwest Symposium on Circuits and Systems, 2011:7 doi: 10.1007/s10470-013-0071-5[2] Chen S M, Brodersen R W. A 6-bit 600-MS/s 5.3 mW asynchronous ADC in 0.13μm CMOS. IEEE J Solid-State Circuits, 2006, 41(12):2669 doi: 10.1109/JSSC.2006.884231[3] Schinkel D, Mensink E, Klumperink E, et al. A double-tail latch-type voltage sense amplifier with 18 ps setup+hold time. Int Solid State Circuits Conf (ISSCC), 2007:314 doi: 10.1007%2Fs10470-011-9687-5.pdf[4] Zhu Y, Chan C H. A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J Solid-State Circuits, 2010, 45(6):1111 doi: 10.1109/JSSC.2010.2048498[5] Ginsburg B P, Chandrakasan A P. 500-MS/s 5-bit ADC in 65 nm CMOS with split capacitor array DAC. IEEE J Solid-State Circuits, 2007, 42(4):739 doi: 10.1109/JSSC.2007.892169[6] Chen Y J, Tsai J H, Shen M H, et al. A 1-V 8-bit 100 kS/s-to-4MS/s asynchronous SAR ADC with 46 fJ/conv.-step. IEEE Int Symp on VLSI Design, Automation and Test (VLSI-DAT), 2011:25 http://www.sciencedirect.com/science/article/pii/S0026269212000730[7] Tsai J H, Chen Y J, Shen M H. A 1-V, 8 b, 40 MS/s, 113μW charge-recycling SAR ADC with a 14μW asynchronous controller. IEEE Symp on VLSI Circuits, 2011:264[8] Kim M J, Yoon H S, Lee Y J, et al. An 11 b 70 MHz 1.2 mm2 49 mW 0.18μm CMOS ADC with on-chip current/voltage references. IEEE European Solid-State Circuits Conf (ESSCC), 2002:463 http://www.academia.edu/28921281/The_ATLAS_experiment_at_the_CERN_large_hadron_collider[9] Cho Y J, Bae H H, Lee M J, et al. An 8 b 220 MS/s 0.25μm CMOS pipeline ADC with on-chip RC-filter based voltage references. IEEE Asia-Pacific Conference on Advanced System Integrated Circuits (AP-ASIC), 2004:90 doi: 10.1007/978-1-4614-1371-4_7 -

Proportional views

DownLoad:

DownLoad: