| Citation: |

Xiao Hong, Houpeng Chen, Zhitang Song, Daolin Cai, Xi Li. A low jitter PLL clock used for phase change memory[J]. Journal of Semiconductors, 2013, 34(2): 025012. doi: 10.1088/1674-4926/34/2/025012

****

X Hong, H P Chen, Z T Song, D L Cai, X Li. A low jitter PLL clock used for phase change memory[J]. J. Semicond., 2013, 34(2): 025012. doi: 10.1088/1674-4926/34/2/025012.

|

A low jitter PLL clock used for phase change memory

DOI: 10.1088/1674-4926/34/2/025012

More Information

-

Abstract

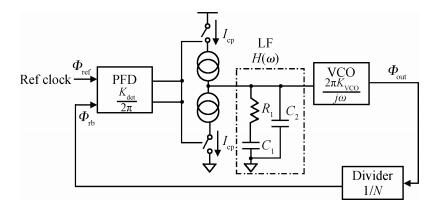

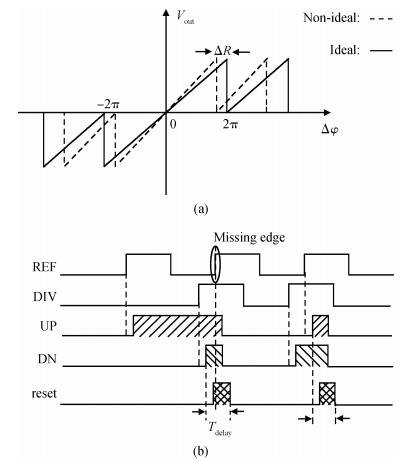

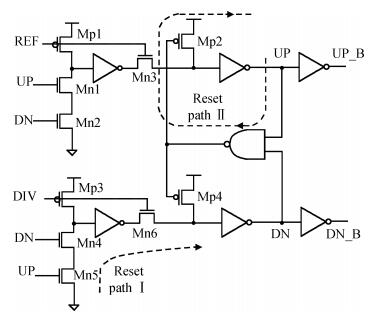

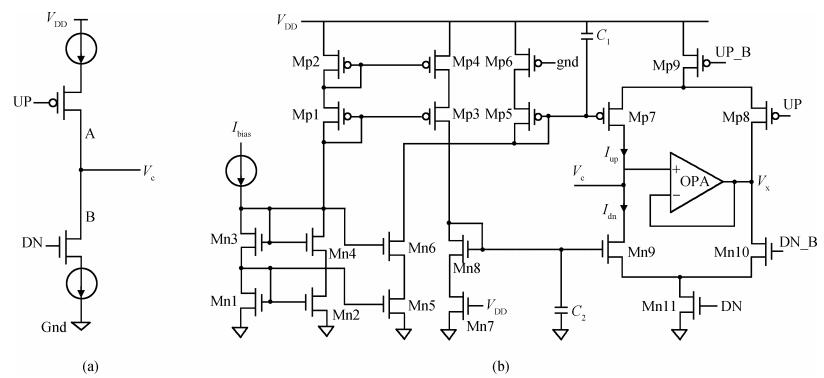

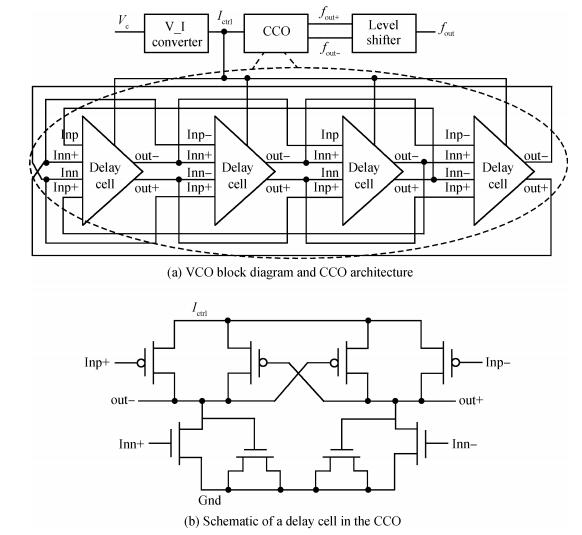

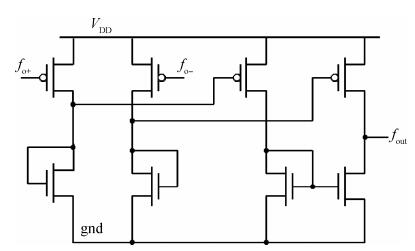

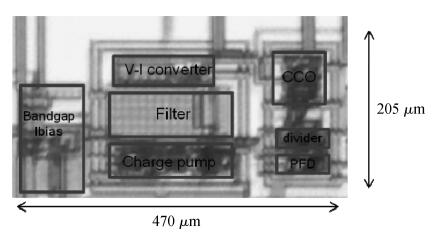

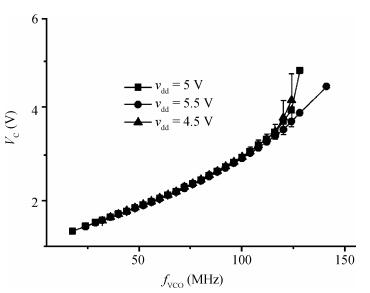

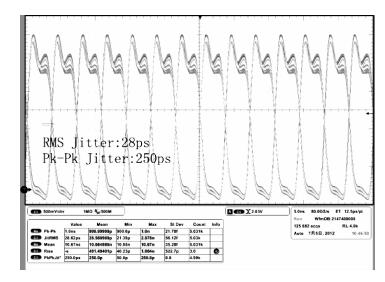

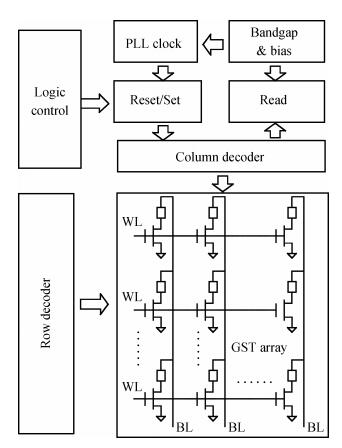

A fully integrated low-jitter, precise frequency CMOS phase-locked loop (PLL) clock for the phase change memory (PCM) drive circuit is presented. The design consists of a dynamic dual-reset phase frequency detector (PFD) with high frequency acquisition, a novel low jitter charge pump, a CMOS ring oscillator based voltage-controlled oscillator (VCO), a 2nd order passive loop filter, and a digital frequency divider. The design is fabricated in 0.35 μm CMOS technology and consumes 20 mW from a supply voltage of 5 V. In terms of the PCM's program operation requirement, the output frequency range is from 1 to 140 MHz. For the 140 MHz output frequency, the circuit features a cycle-to-cycle jitter of 28 ps RMS and 250 ps peak-to-peak.-

Keywords:

- PLL,

- PFD,

- charge pump,

- VCO,

- PCM

-

References

[1] Lai S, Lowrey T. OUM——a 180 nm nonvolatile memory cell element technology for stand alone and embedded applications. IEDM, 2001, 36(5):1 https://core.ac.uk/display/1508489[2] Lavizzari S, Sharma D, Ielmini D. Threshold-switching delay controlled by 1/f current fluctuations in phase-change memory devices. IEEE Trans Electron Devices, 2010, 57(5):1047 doi: 10.1109/TED.2010.2042768[3] Shi X T, Imfeld K. A low-jitter and low-power CMOS PLL for clock multiplication. Proceedings of the 32nd European IEEE Solid-State Circuits Conference, ESSCIRC, 2006:174[4] Keliu S. CMOS PLL synthesizers analysis and design. Boston, Springer Science + Business Media, 2005 doi: 10.1007/b102174[5] Todd C W, Beomsup K. Analysis of timing jitter in CMOS ring oscillators. IEEE Proceedings of ISCAS, 1994:191 http://citeseerx.ist.psu.edu/showciting?cid=729794[6] Mansuri M, Liu D, Yang C K. Fast frequency acquisition phase-frequency detectors for GSamples/s phase-locked loops. IEEE J Solid-State Circuits, 2002, 37(10):1331 doi: 10.1109/JSSC.2002.803048[7] Jae-Shin L, Min-Sun K. Charge pump with perfect current matching characteristics in phase-locked loops. Electron Lett, 2000, 36(23):1907 doi: 10.1049/el:20001358[8] Mansuri M, Yang C K. A low-power adaptive bandwidth PLL and clock buffer with supply-noise compensation. IEEE J Solid-State Circuits, 2003, 38(11):1804 doi: 10.1109/JSSC.2003.818300[9] John G M, Mark A H. Precise delay generation using coupled oscillators. IEEE J Solid-State Circuits, 1993, 28(12):1273 doi: 10.1109/4.262000[10] Hong X, Chen H P, Song Z T, et al. A low noise clock generator for phase change memories. Microelectron, 2011, 41(4):540[11] Ge Y, Jia S. A fast acquisition PLL with wide tuning range. Chinese Journal of Semiconductors, 2007, 28(3):365 -

Proportional views

DownLoad:

DownLoad: