| Citation: |

Ye Han, Quanliang Li, Cong Shi, Nanjian Wu. A 10-bit column-parallel cyclic ADC for high-speed CMOS image sensors[J]. Journal of Semiconductors, 2013, 34(8): 085016. doi: 10.1088/1674-4926/34/8/085016

****

Y Han, Q L Li, C Shi, N J Wu. A 10-bit column-parallel cyclic ADC for high-speed CMOS image sensors[J]. J. Semicond., 2013, 34(8): 085016. doi: 10.1088/1674-4926/34/8/085016.

|

A 10-bit column-parallel cyclic ADC for high-speed CMOS image sensors

DOI: 10.1088/1674-4926/34/8/085016

More Information

-

Abstract

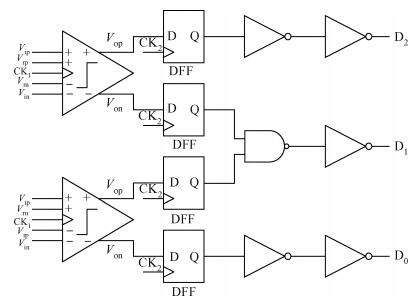

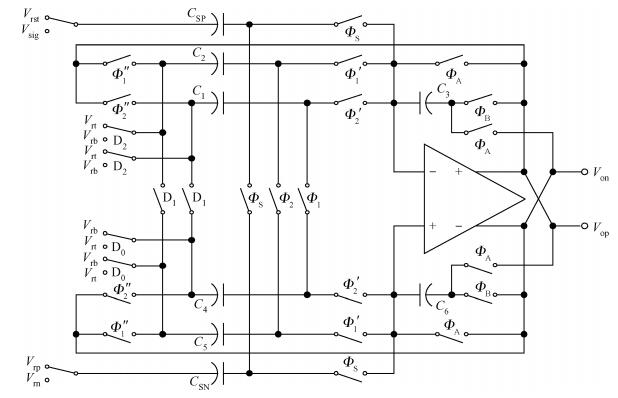

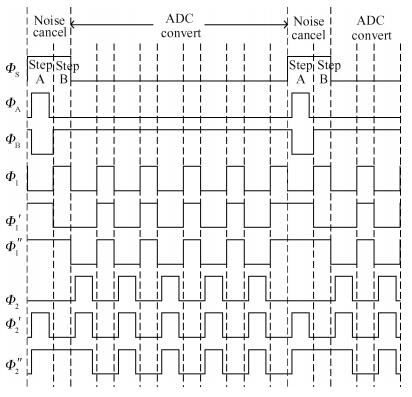

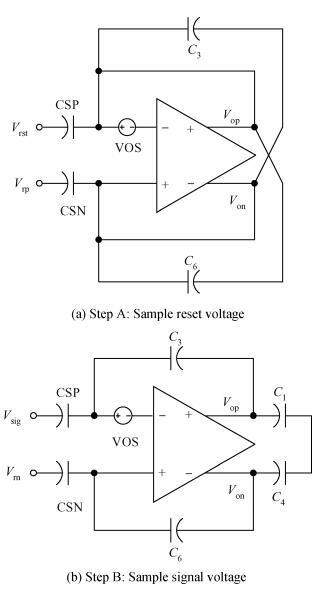

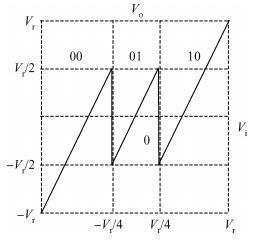

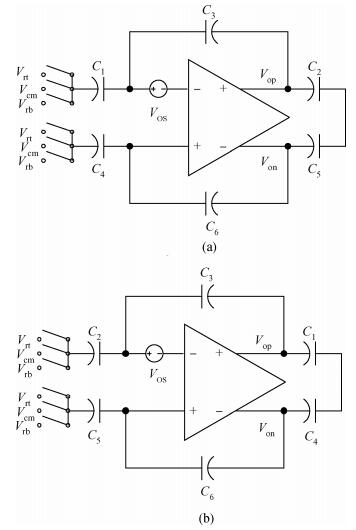

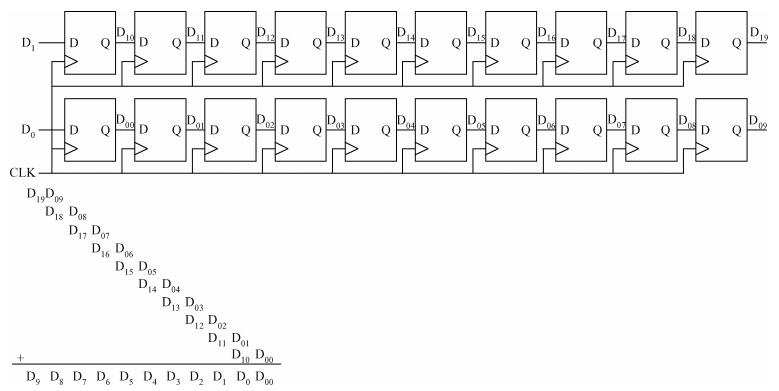

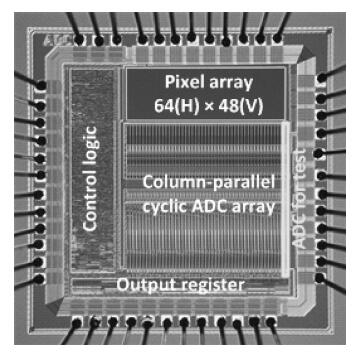

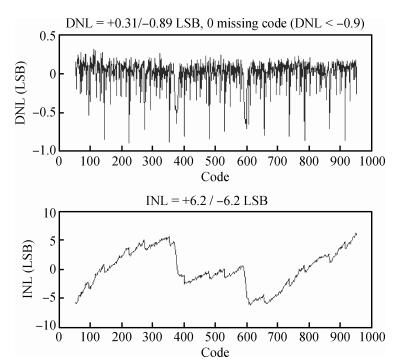

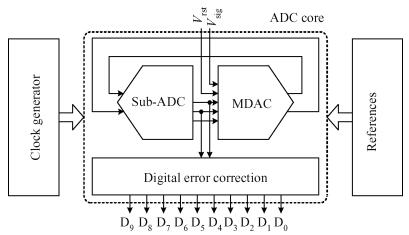

This paper presents a high-speed column-parallel cyclic analog-to-digital converter (ADC) for a CMOS image sensor. A correlated double sampling (CDS) circuit is integrated in the ADC, which avoids a stand-alone CDS circuit block. An offset cancellation technique is also introduced, which reduces the column fixed-pattern noise (FPN) effectively. One single channel ADC with an area less than 0.02 mm2 was implemented in a 0.13 μm CMOS image sensor process. The resolution of the proposed ADC is 10-bit, and the conversion rate is 1.6 MS/s. The measured differential nonlinearity and integral nonlinearity are 0.89 LSB and 6.2 LSB together with CDS, respectively. The power consumption from 3.3 V supply is only 0.66 mW. An array of 48 10-bit column-parallel cyclic ADCs was integrated into an array of CMOS image sensor pixels. The measured results indicated that the ADC circuit is suitable for high-speed CMOS image sensors. -

References

[1] Yang D, Fowler B, Gamal A. A Nyquist-rate pixel-level ADC for CMOS image sensors. IEEE J Solid-State Circuits, 1999, 34(3):348 doi: 10.1109/4.748186[2] Watabe T, Kitamura K, Sawamoto T, et al. A 33 M pixel 120 fps CMOS image sensor using 12 b column-parallel pipelined cyclic ADCs. IEEE International Solid-State Circuits Conference, 2012:388[3] Kleinfelder S, Lim S, Liu X, et al. A 10000 frames/s CMOS digital pixel sensor. IEEE J Solid-State Circuits, 2001, 36(12):2049 doi: 10.1109/4.972156[4] Krymski A I, Tu N. A 9-V/lux-s 5000-frames/s 512×512 CMOS sensor. IEEE Trans Electron Devices, 2003, 50(1):136 doi: 10.1109/TED.2002.806958[5] Oike Y, Gamal A E. A 256×256 CMOS image sensor with Σδ-based single-shot compressed sensing. IEEE International Solid-State Circuits Conference, 2012:386[6] Furuta M, Nishikawa Y, Inoue T, et al. A high-speed, high-sensitivity digital CMOS image sensor with a global shutter and 12-bit column-parallel cyclic A/D converters. IEEE J Solid-State Circuits, 2007, 42(4):766 doi: 10.1109/JSSC.2007.891655[7] Park J H, Aoyama S, Watanabe T, et al. A high-speed low-noise CMOS image sensor with 13-b column-parallel single-ended cyclic ADCs. IEEE Trans Electron Devices, 2009, 56(11):2414 doi: 10.1109/TED.2009.2030635[8] Razavi B. Design of analog CMOS integrated circuits. New York: McGraw-Hill, 2001[9] Hwang K. Computer arithmetic principles, architecture and design. New York: John Wiley & Sons, 1979[10] Andrew A, Paul G. A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter. IEEE J Solid-State Circuits, 1999, 34(5):599 doi: 10.1109/4.760369[11] Bigas M, Cabrujaa E, Forest J, et al. Review of CMOS image sensors. Solid-State Electron, 2006, 37:433[12] Theuwissen J, Albert P. CMOS image sensors:state-of-the-art. Solid-State Electron, 2008, 52:1401 doi: 10.1016/j.sse.2008.04.012[13] Zhang Na. Research on key techniques of super high speed digital CMOS image sensor. Dissertation for the Doctoral Degree, Tianjin: Tianjin University, 2008(in Chinese) -

Proportional views

DownLoad:

DownLoad: