| Citation: |

Heng Wu, Zhen'an Tang, Zhu Wang, Wan Cheng, Daquan Yu. Simulation of through via bottom-up copper plating with accelerator for the filling of TSVs[J]. Journal of Semiconductors, 2013, 34(9): 096001. doi: 10.1088/1674-4926/34/9/096001

****

H Wu, Z A Tang, Z Wang, W Cheng, D Q Yu. Simulation of through via bottom-up copper plating with accelerator for the filling of TSVs[J]. J. Semicond., 2013, 34(9): 096001. doi: 10.1088/1674-4926/34/9/096001.

|

Simulation of through via bottom-up copper plating with accelerator for the filling of TSVs

DOI: 10.1088/1674-4926/34/9/096001

More Information

-

Abstract

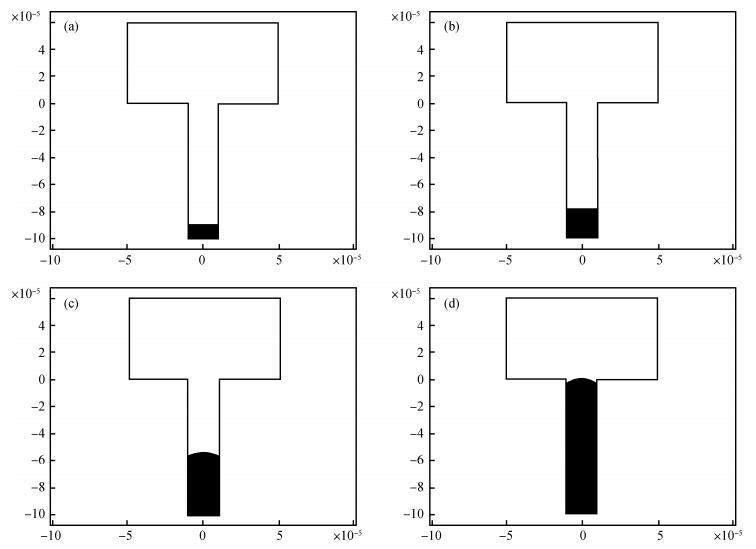

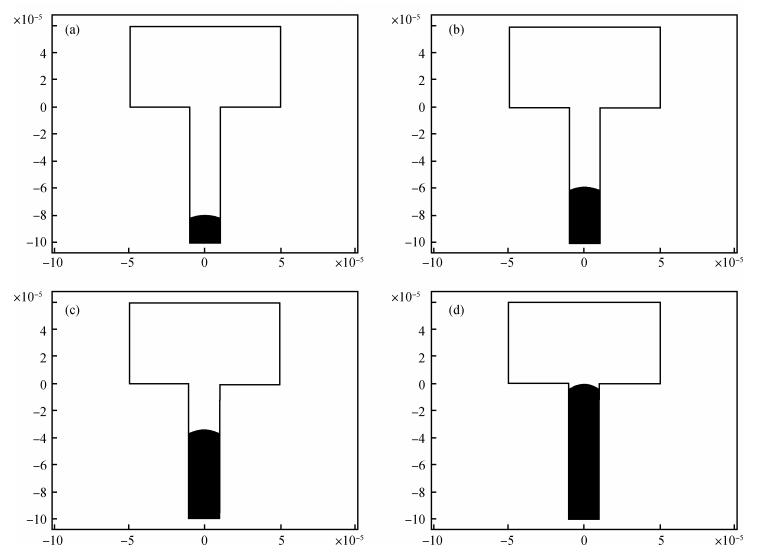

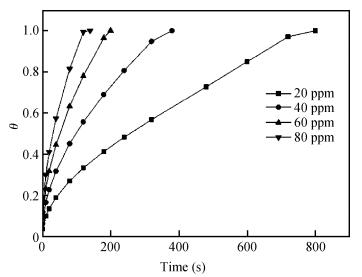

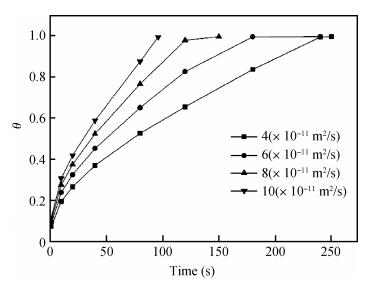

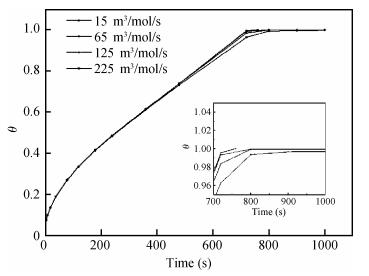

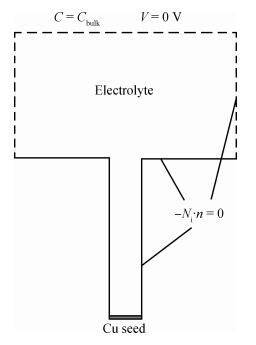

Filling high aspect ratio through silicon vias (TSVs) without voids and seams by copper plating is one of the technical challenges for 3D integration. Bottom-up copper plating is an effective solution for TSV filling. In this paper, a new numerical model was developed to simulate the electrochemical deposition (ECD) process, and the influence of an accelerator in the electrolyte was investigated. The arbitrary Lagrange-Eulerian (ALE) method for solving moving boundaries in the finite element method (FEM) was used to simulate the electrochemical process. In the model, diffusion coefficient and adsorption coefficient were considered, and then the time-resolved evolution of electroplating profiles was simulated with ion concentration distribution and the electric current density.-

Keywords:

- TSVs,

- copper plating,

- through via,

- bottom-up,

- accelerator

-

References

[1] Vereecken F M, Binstead R A, Deligianni H, et al. The chemistry of additives in damascene copper plating. IBM J Res & Dev, 2005, 49:3[2] Beica R, Sharbono C, Ritzdorf T. Through silicon via copper electrodeposition for 3D integration. Proc IEEE ECTC, 2008:577[3] Song C, Wu H, Jing X, et al. Numerical simulation and experimental verification of copper plating with different additives for through silicon vias. Proc ESTC 2012:A1[4] Wu J, del Alamo J A. Fabrication and characterization of through-substrate interconnects. IEEE Trans Electron Devices, 2010, 57:1261 doi: 10.1109/TED.2010.2045671[5] Song C, Wang Z, Tan Z, et al. Moving boundary simulation and experimental verification of high aspect-ratio through-silicon-vias for 3-D integration. IEEE Trans Components, Packaging and Manufacturing Technology, 2012, 2(1):23 doi: 10.1109/TCPMT.2011.2167681[6] Wheeler D, Josell D, Moffat T P. Modeling superconformal electrodeposition using the level set method. J Electrochem Soc, 2003, 150:C302 doi: 10.1149/1.1562598[7] Zheng Z, Stephens R M, Braatz R D, et al. A hybrid multiscale kinetic Monte Carlo method for simulation of copper electrodepostion. J Comput Phys, 2008, 227:5184 doi: 10.1016/j.jcp.2008.01.056[8] Tenno R, Pohjoranta A. An ALE model for prediction and control of the microvia fill process with two additives. J Electrochem Soc, 2008, 155:D383 doi: 10.1149/1.2890413 -

Proportional views

DownLoad:

DownLoad: