| Citation: |

Shubin Liu, Zhangming Zhu, Yintang Yang, Lianxi Liu. A programmable MDAC with power scalability[J]. Journal of Semiconductors, 2014, 35(1): 015011. doi: 10.1088/1674-4926/35/1/015011

****

S B Liu, Z M Zhu, Y T Yang, L X Liu. A programmable MDAC with power scalability[J]. J. Semicond., 2014, 35(1): 015011. doi: 10.1088/1674-4926/35/1/015011.

|

-

Abstract

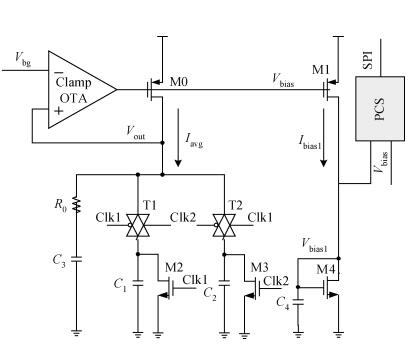

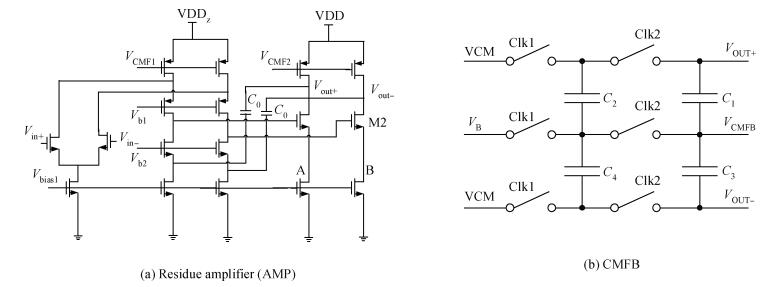

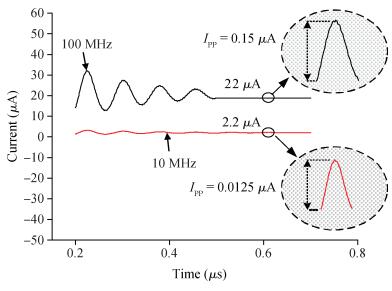

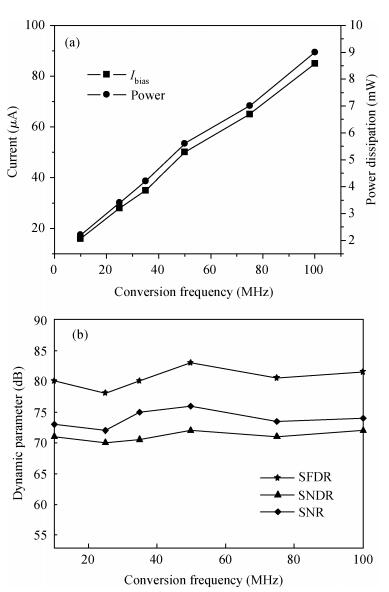

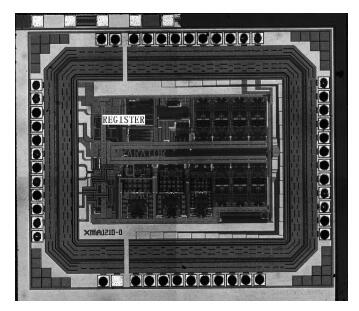

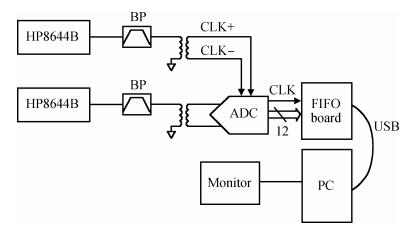

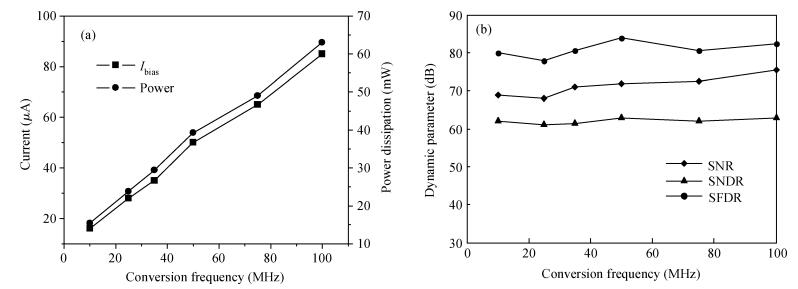

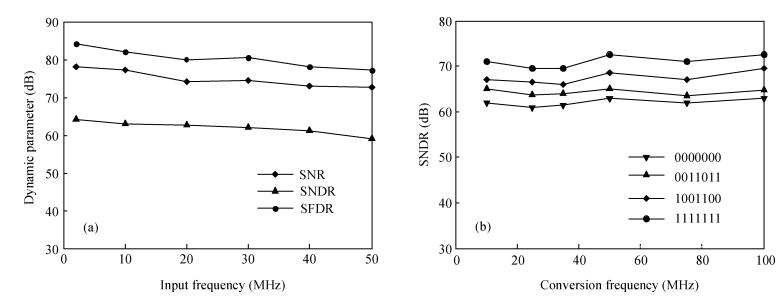

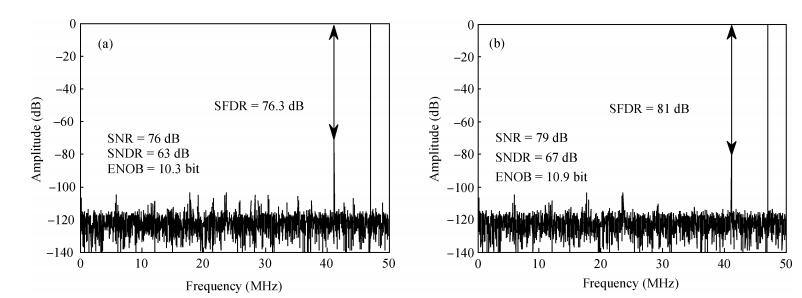

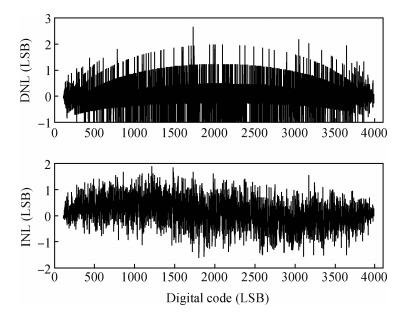

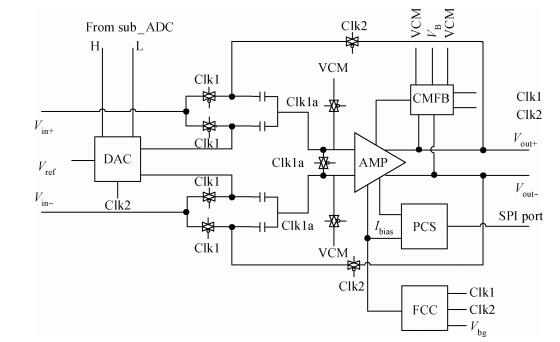

A programmable high precision multiplying DAC (MDAC) is proposed. The MDAC incorporates a frequency-current converter (FCC) to adjust the power versus sampling rate and a programmable operational amplifier (POTA) to achieve the tradeoff between resolution and power of the MDAC, which makes the MDAC suitable for a 12 bit SHA-less pipelined ADC. The prototype of the proposed pipelined ADC is implemented in an SMIC CMOS 0.18 μm 1P6M process. Experimental results demonstrate that power of the proposed ADC varies from 15.4 mW (10 MHz) to 63 mW (100 MHz) while maintaining an SNDR of 60.5 to 63 dB at all sampling rates. The differential nonlinearity and integral nonlinearity without any calibration are no more than 2.2/-1 LSB and 1.6/-1.9 LSB, respectively. -

References

[1] Lee K H, Kim K S, Lee H. A 12 b 50 MS/s 21.6 mW 0.18μm CMOS ADC maximally sharing capacitors and op-amps. IEEE Trans Circuits Syst, 2011, 58(9):2127 doi: 10.1109/TCSI.2011.2112591[2] Hernes B, Briskemyr A, Andersen T N, et al. A 1.2 V 220 MS/s 10 b pipelined ADC implemented in 0.13μm digital CMOS. IEEE International Solid-State Circuits Conference, 2004:256 doi: 10.1007/978-90-481-9710-1_7[3] Lin J F, Chang S J, Liu C C, et al. A 10-bit 60-MS/s low-power pipelined ADC with split-capacitor CDS technique. IEEE Trans Circuits Syst Ⅱ:Express Briefs, 2010, 57:163 doi: 10.1109/TCSII.2010.2040307[4] Boulemnakher M, Andre E, Roux J, et al. A 1.2 V 4.5 mW 10 b 100 Ms/s pipelined ADC in a 65 nm COMS. IEEE International Solid-State Circuits Conference, 2008:250[5] Huang M C, Liu S I. A 10-MS/s-to-100kS/s power-scalable fully differential CBSC 10-bit pipelined ADC with adaptive biasing. IEEE Trans Circuits Syst, 2010, 57:11 doi: 10.1109/TCSII.2009.2037259[6] Ahmed I, John D A. A 50-MS/s (35 mW) to 1-kS/s (15 mW) power scaleable 10-bit pipelined ADC using rapid power-on opamps and minimal bias current variation. IEEE J Solid-State Circuits, 2005, 40(12):2446 doi: 10.1109/JSSC.2005.856289[7] Zhang H, Tan J, Zhang C, et al. A 0.6-to-200 MSPS speed reconfigurable and 1.9-to-27 mW power scalable 10 bit ADC. European Solid-State Circuits Conference (ESSCIRC), 2011:367 https://core.ac.uk/display/4315162[8] Binkley D M, Hopper C E, Tucker S D, et al. A CAD methodology for optimizing transistor current and sizing in analog CMOS design. IEEE Trans Computer-Aided Design of Integrated Circuits and Systems, 2003, 22(2):225 doi: 10.1109/TCAD.2002.806606 -

Proportional views

DownLoad:

DownLoad: