| Citation: |

R Anjana, Ajay Somkuwar. FELERION:a new approach for leakage power reduction[J]. Journal of Semiconductors, 2014, 35(12): 125001. doi: 10.1088/1674-4926/35/12/125001

****

R Anjana, A Somkuwar. FELERION:a new approach for leakage power reduction[J]. J. Semicond., 2014, 35(12): 125001. doi: 10.1088/1674-4926/35/12/125001.

|

FELERION:a new approach for leakage power reduction

DOI: 10.1088/1674-4926/35/12/125001

More Information

-

Abstract

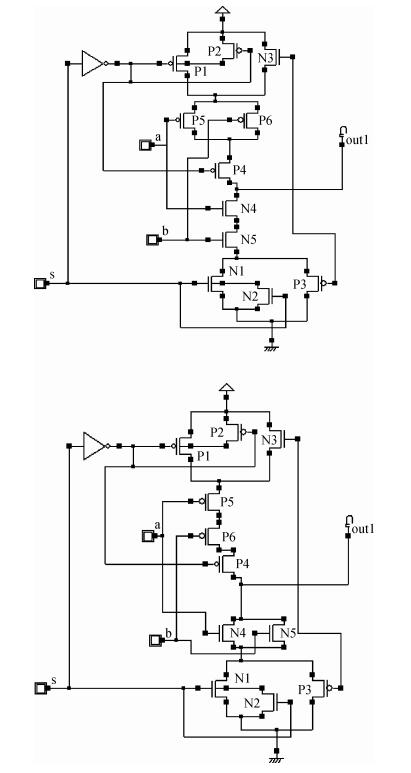

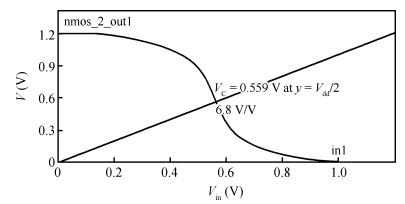

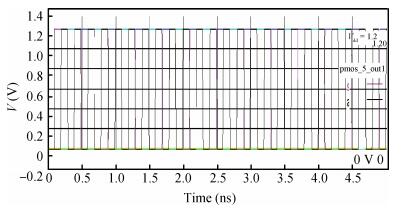

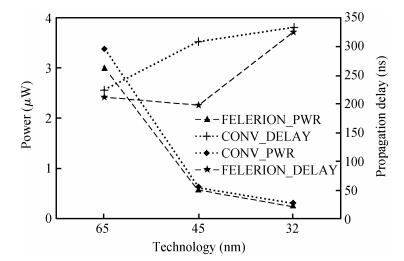

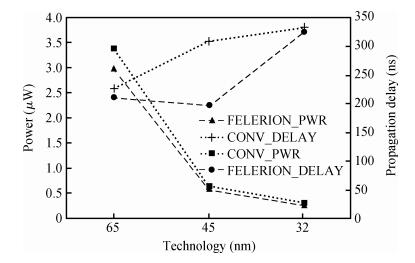

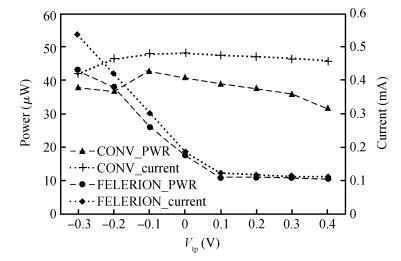

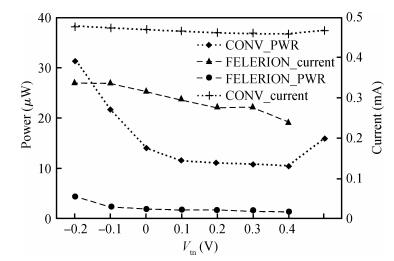

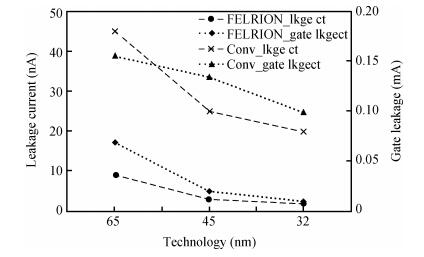

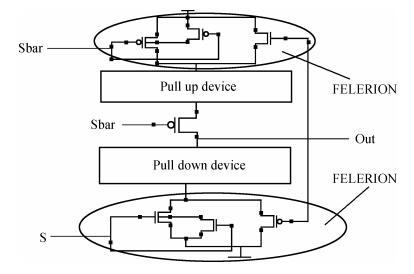

The circuit proposed in this paper simultaneously reduces the sub threshold leakage power and saves the state of art aspect of the logic circuits. Sleep transistors and PMOS-only logic are used to further reduce the leakage power. Sleep transistors are used as the keepers to reduce the sub threshold leakage current providing the low resistance path to the output. PMOS-only logic is used between the pull up and pull down devices to mitigate the leakage power further. Our proposed fast efficient leakage reduction circuit not only reduces the leakage current but also reduces the power dissipation. Power and delay are analyzed at the 32 nm BSIM4 model for a chain of four inverters, NAND, NOR and ISCAS-85 c17 benchmark circuits using DSCH3 and the Microwind tool. The simulation results reveal that our proposed approach mitigates leakage power by 90%-94% as compared to the conventional approach.-

Keywords:

- leakage power,

- sleep transistors,

- FELERION,

- scaling,

- propagation delay,

- power dissipation

-

References

[1] Borkar S. Design challenges of technology scaling. IEEE Microelectron, 2008, 19:1891[2] Mutoh S, Douseki T, Matsuya Y, et al. 1-V power supply high speed digital circuit technology with multi-threshold voltage CMOS. IEEE J Solid-State Circuits, 1995, 30:847 doi: 10.1109/4.400426[3] Narendra S, De V, Antoniadis D, et al. Scaling of stack effect and its application for leakage reduction. Proceedings of the International Symposium on low Power Electronics and Design, Digest of Technical Papers, 2001:195[4] Kawagudhi H, Nose K, Sakurai T. A super cut-off CMOS (SCCMOS) scheme for 0.5-V supply voltage with pico ampere stand by current. IEEE J Solid-State Circuits, 2000, 35:1498 doi: 10.1109/4.871328[5] Wei L, Chen Z, Roy K, et al. Design and optimization of dual-threshold circuits for low-voltage low-power applications. IEEE Trans VLSI Syst, 1999, 7:16 doi: 10.1109/92.748196[6] Kim S H, Mooney Ⅲ V J. Sleepy keeper approach:methodology, layout and power results for 4 bit adder. Technical Report GITCERCS-06-03, Georgia Institute of Technology, 2006[7] Park J C, Mooney Ⅲ V J. Sleepy stack leakage reduction. IEEE Transn VLSI Syst, 2006, 14:1250 doi: 10.1109/TVLSI.2006.886398[8] Hanchate N, Ranganathan N. LECTOR:a technique for leakage reduction in CMOS circuits. IEEE Trans Very Large Scale Integration (VLSI) Syst, 2004, 12:192[9] Lakshmikantan P, Nunez A. VCLEARIT:a VLSI CMOS circuit leakage reduction technique for nanoscale technologies. ACM SIGARCH Computer Architechture News, 2007, 35:10 doi: 10.1145/1360464[10] Sharma V K, Pattanaik M, Raj B. An ON-OFF IC approach for low power high speed CMOS VLSI circuits. International Journal of Electronics, Taylor and Francis, 2014, 101:61[11] International Technology Roadmap for Semiconductors by Semiconductor Industry Association, 2002[12] Deepaksubramanyan B S, Nũnez A. Analysis of subthreshold leakage reduction in CMOS digital circuits. Proceedings of the 13th NASA VLSI Symposium, 2007:1400 -

Proportional views

DownLoad:

DownLoad: