| Citation: |

Zhen Xu, Xueqing Li, Jia'nan Liu, Qi Wei, Li Luo, Huazhong Yang. A 14-bit 500-MS/s DAC with digital background calibration[J]. Journal of Semiconductors, 2014, 35(3): 035008. doi: 10.1088/1674-4926/35/3/035008

****

Z Xu, X Q Li, J Liu, Q Wei, L Luo, H Z Yang. A 14-bit 500-MS/s DAC with digital background calibration[J]. J. Semicond., 2014, 35(3): 035008. doi: 10.1088/1674-4926/35/3/035008.

|

A 14-bit 500-MS/s DAC with digital background calibration

DOI: 10.1088/1674-4926/35/3/035008

More Information

-

Abstract

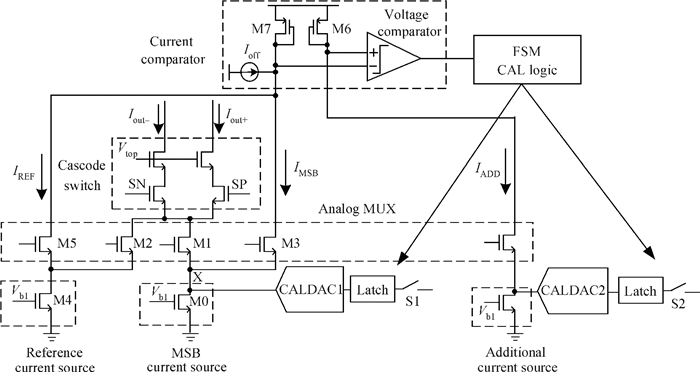

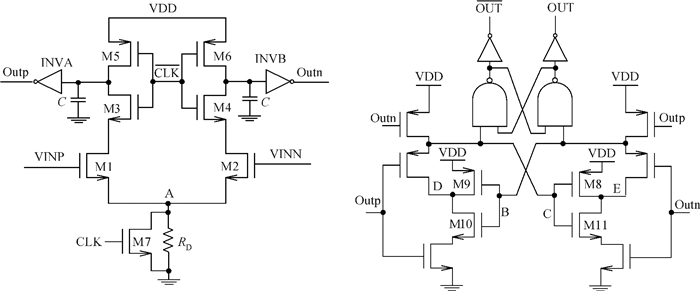

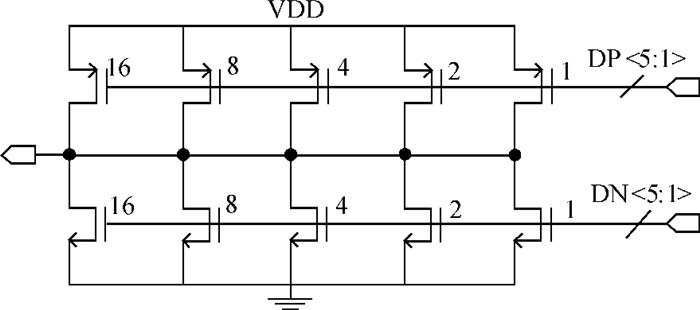

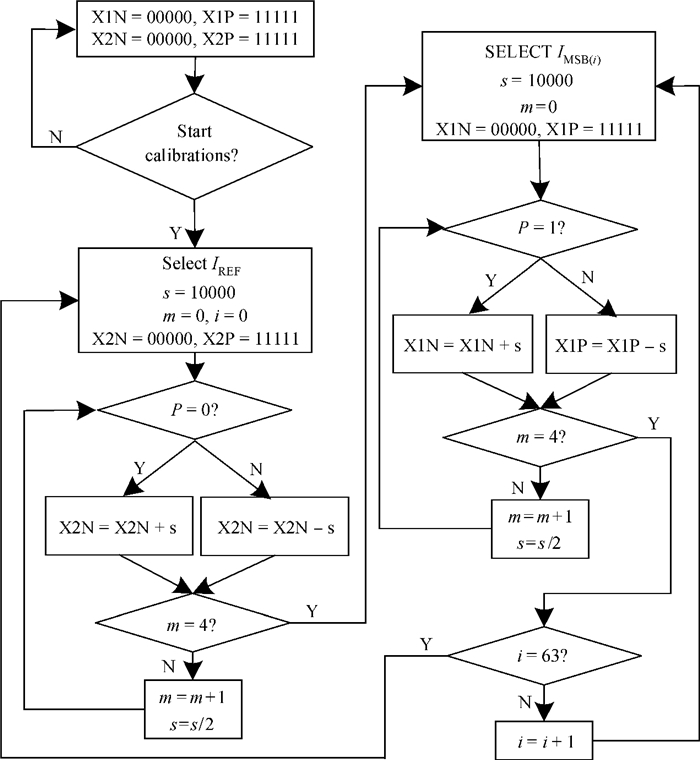

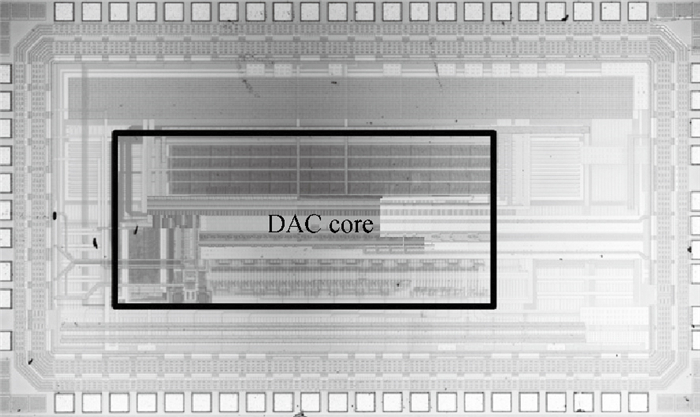

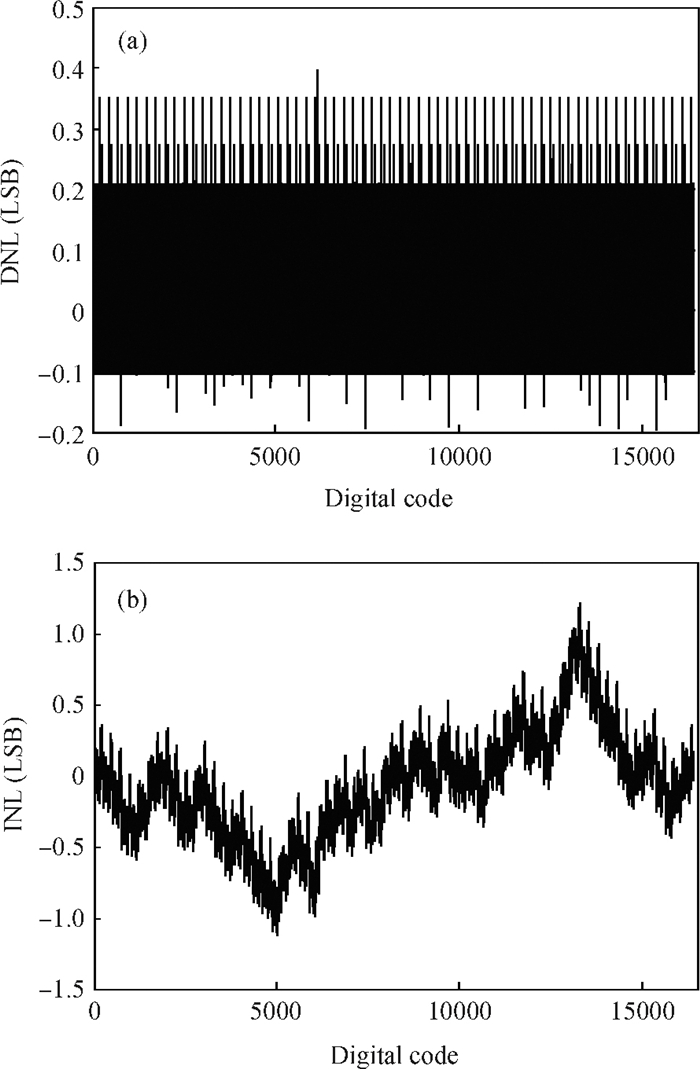

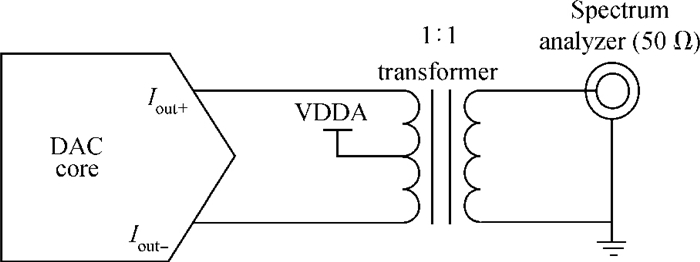

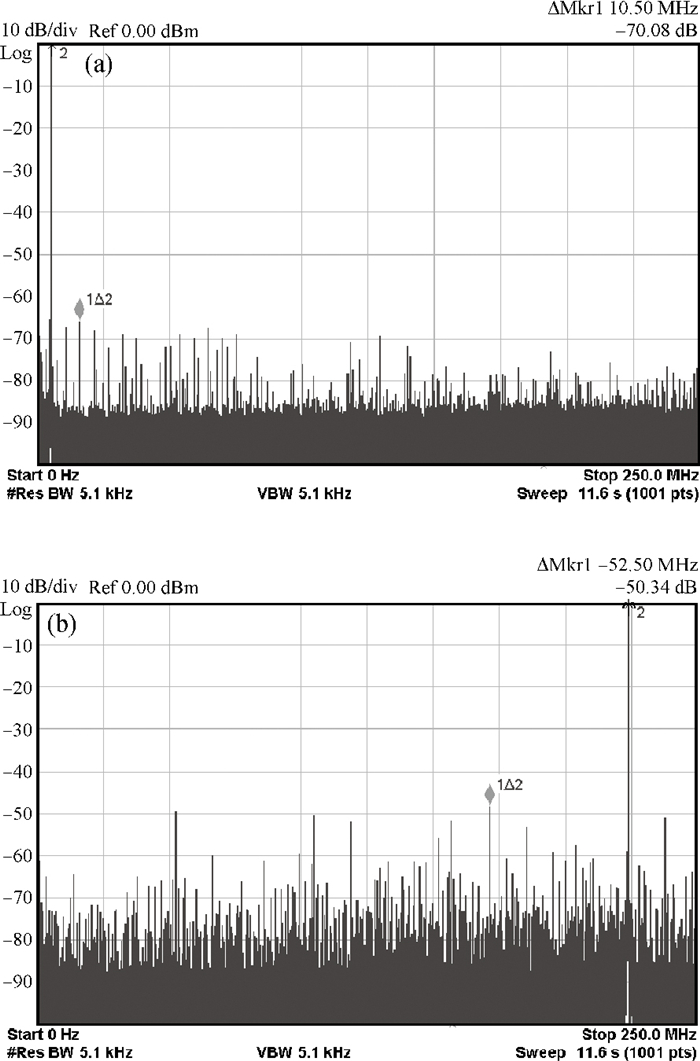

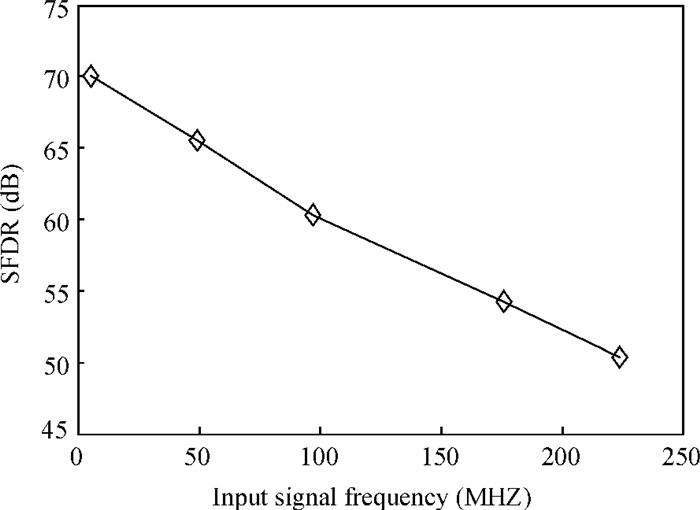

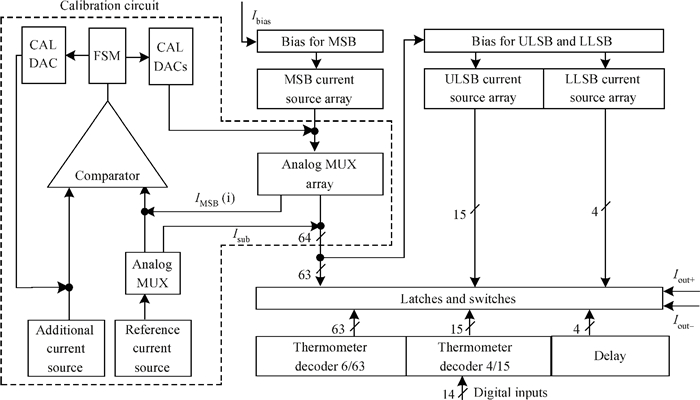

The linearity of current-steering digital-to-analog converters (DACs) at low signal frequencies is mainly limited by matching properties of current sources, so large-size current source arrays are widely used for better matching. This, however, results in large gradient errors and parasitic capacitance, which degrade the spurious free dynamic range (SFDR) for high-frequency signals. To overcome this problem, calibration is an effective method. In this paper, a digital background calibration technique for current-steering DACs is presented and verified by a 14-bit DAC in a 0.13 μm standard CMOS process. The measured differential nonlinearity (DNL) and integral nonlinearity (INL) are 0.4 LSB and 1.2 LSB, respectively. At 500-MS/s, the SFDR is 70 dB and 50.3 dB for signals of 5.4 MHz and 224 MHz, respectively. The core area is 0.69 mm2 and the power consumption is 165 mW from a mixed power supply with 1.2 V and 3.3 V. -

References

[1] Huang Q, Francese P A, Martelli C, et al. A 200 MS/s 14 b 97 mW DAC in 0.18μm CMOS. IEEE ISSCC Dig Tech Papers, 2004:364 http://www.jos.ac.cn/bdtxben/ch/reader/create_pdf.aspx?file_no=13082701[2] Pelgrom M, Duinmaijer A, Welbers A. Matching properties of MOS transistors. IEEE J Solid-State Circuits, 1989, 24(5):1433 doi: 10.1109/JSSC.1989.572629[3] Tseng W H, Fan C W, Wu J T. A 12-bit 1.25-GS/s DAC in 90 nm CMOS with > 70 dB SFDR up to 500 MHz. IEEE J Solid-State Circuits, 2011, 46(12):2845 doi: 10.1109/JSSC.2011.2164302[4] Vander Plas G A M, Vandenbussche J, Sansen W, et al. A 14-bit intrinsic accuracy Q2 random walk CMOS DAC. IEEE J Solid-State Circuits, 1999, 34(12):1708 doi: 10.1109/4.808896[5] Bugeja A, Song B S. A self-trimming 14-b 100-MS/s CMOS DAC. IEEE J Solid-State Circuits, 2000, 35(12):1841 doi: 10.1109/4.890297[6] Chan K L, Zhu J, Galton I. Dynamic element matching to prevent nonlinear distortion from pulse-shape mismatches in high-resolution DACs. IEEE J Solid-State Circuits, 2008, 43(9):2607 https://core.ac.uk/display/21704311[7] Doris K, Lin C, Domine L, et al. D/A conversion:amplitude and time error mapping optimization. Proc IEEE ICECS, 2001:863 http://ieeexplore.ieee.org/document/957610/keywords[8] Yusuke I, Akira M. Digital calibration method for binary-weighted current-steering D/A-converters without calibration ADC. IEICE Trans, 2007, 90(6):1172 http://dialnet.unirioja.es/servlet/articulo?codigo=3510485[9] Radulov G I, Quinn P J, Hegt H, et al. An on-chip self-calibration method for current mismatch in D/A converters. Proc IEEE ESSCIRC, 2005:169 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?reload=true&arnumber=1541586&punumber%3D10265[10] Chi J H, Chu S H, Tsai T H. A 1.8-V 12-bit 250-MS/s 25-mW self-calibrated DAC. Proc IEEE ESSCIRC, 2010:222 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?reload=true&arnumber=5619889&contentType=Conference+Publications[11] Radulov G. Flexible and self-calibrating current-steering digital-to-analog converters:analysis, classification and design. PhD Thesis, Eindhoven University of Technology, 2010 doi: 10.6100/IR656902[12] Qiu D, Fang S, Xie R, et al. A 14-bit 100 MS/s self-calibrated DAC with a randomized calibration-period. IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2010:312 http://ieeexplore.ieee.org/document/5667743/[13] Chen T, Gielen G G E. The analysis and improvement of a current-steering DACs dynamic SFDR-I:the cell-dependent delay differences. IEEE Trans Circuits Syst Ⅰ, 2006, 53(1):3 http://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=01576881[14] Schafferer B, Adams R. A 3 V CMOS 400 mW 14 b 1.4 GS/s DAC for multi-carrier applications. IEEE ISSCC Dig Tech Papers, 2004:360 doi: 10.1007/978-1-4614-1250-2_2/fulltext.html[15] Van den Bosch A, Steyaert M, Sansen W. An accurate statistical yield model for CMOS current-steering D/A converters. IEEE Int Symp Circuits and Systems (ISCAS), 2000:Ⅳ.105 doi: 10.1023/A:1011261330190[16] Chen T, Gielen G. The analysis and improvement of a current-steering DAC's dynamic SFDR——Ⅱ:the output-dependent delay differences. IEEE Trans Circuits Syst Ⅰ, 2007, 54(2):268 doi: 10.1109/TCSI.2006.887598[17] Fan H, Han X, Wei Q, et al. A 12-bit self-calibrating SAR ADC achieving a Nyquist 90.4-dB SFDR. Analog Integrated Circuits and Signal Processing, 2013, 74(1):239 doi: 10.1007/s10470-012-9977-6[18] Traff H. Novel approach to high speed CMOS current comparators. Electron Lett, 1992, 28(3):310 doi: 10.1049/el:19920192[19] Chen T, Georges G E. A 14-bit 200-MHz current-steering DAC with switching-sequence post-adjustment calibration. IEEE J Solid-State Circuits, 2007, 42(11):2386 doi: 10.1109/JSSC.2007.906200[20] Cheng L, Chen C X, Ye F, et al. A digitally calibrated current-steering DAC with current-splitting array. IEEE International Midwest Symposium on Circuits and Systems, 2012:278 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?reload=true&arnumber=6292011[21] Ali A M A, Dillon C, Sneed R, et al. A 14-bit 125 MS/s IF/RF sampling pipelined ADC with 100 dB SFDR and 50 fs jitter. IEEE J Solid-State Circuits, 2006, 41(8):1846 doi: 10.1109/JSSC.2006.875291 -

Proportional views

DownLoad:

DownLoad: