| Citation: |

Wei Lü, Duona Luo, Fengcheng Mei, Jiaqi Yang, Libin Yao, Lin He, Fujiang Lin. A 0.6 V 10 bit 1 MS/s monotonic switching SAR ADC with common mode stabilizer in 0.13 μm CMOS[J]. Journal of Semiconductors, 2014, 35(5): 055006. doi: 10.1088/1674-4926/35/5/055006

****

W Lü, D N Luo, F C Mei, J Q Yang, L B Yao, L He, F J Lin. A 0.6 V 10 bit 1 MS/s monotonic switching SAR ADC with common mode stabilizer in 0.13 μm CMOS[J]. J. Semicond., 2014, 35(5): 055006. doi: 10.1088/1674-4926/35/5/055006.

|

A 0.6 V 10 bit 1 MS/s monotonic switching SAR ADC with common mode stabilizer in 0.13 μm CMOS

DOI: 10.1088/1674-4926/35/5/055006

More Information

-

Abstract

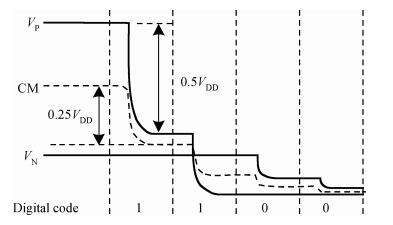

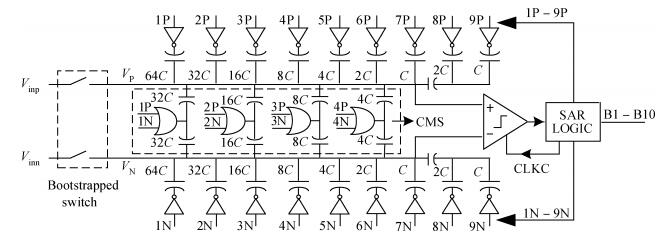

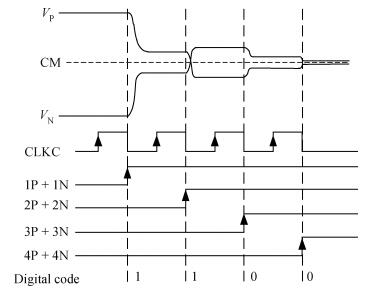

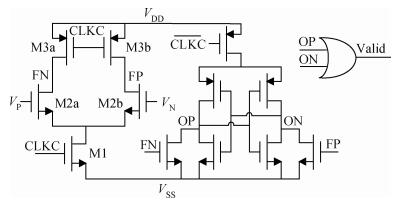

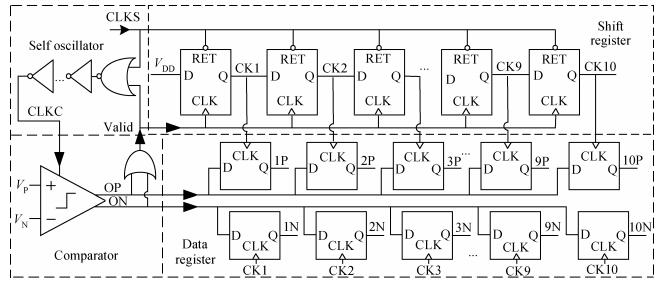

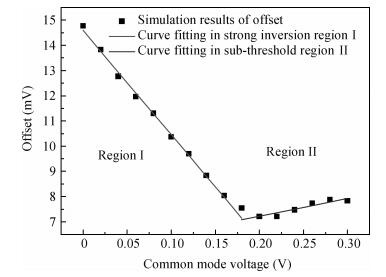

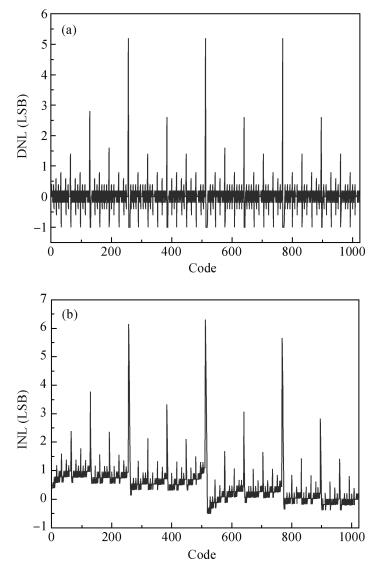

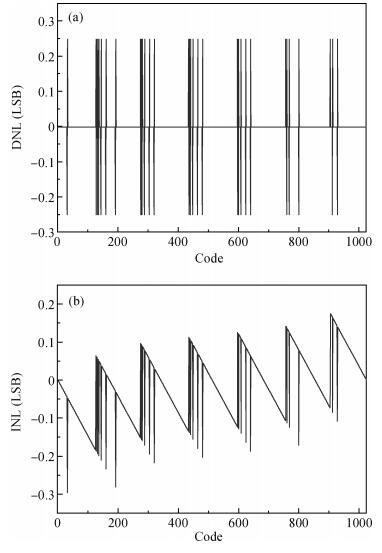

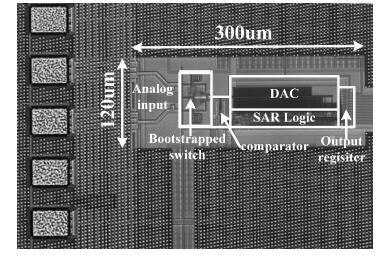

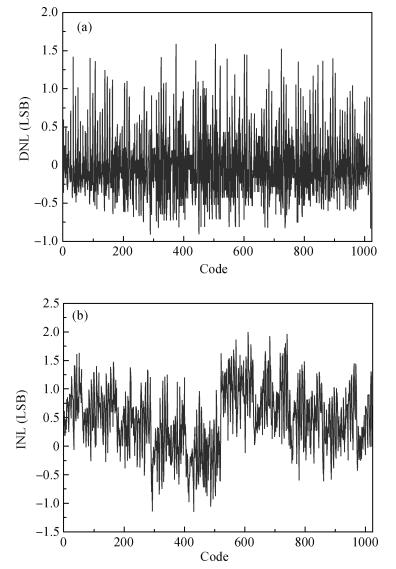

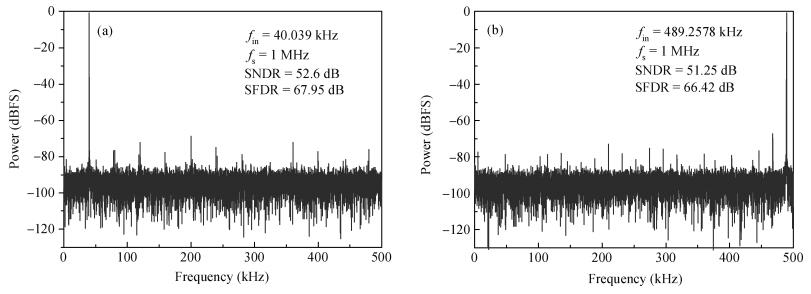

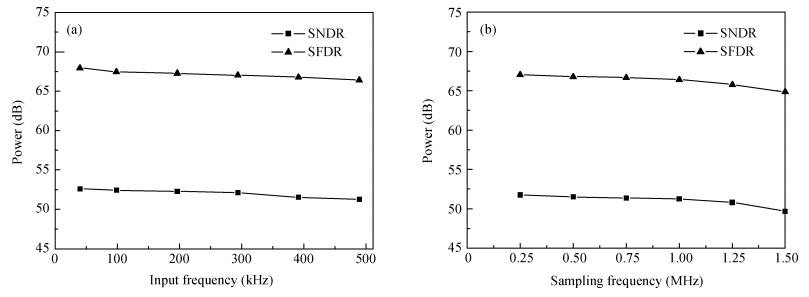

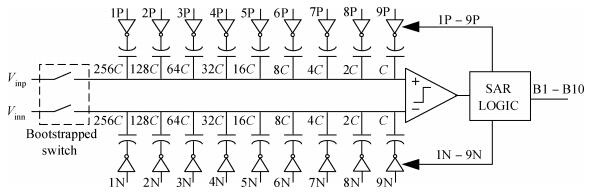

This paper presents a 0.6 V 10 bit successive approximation register (SAR) ADC design dedicated to the wireless sensor network application. It adopts a monotonic switching scheme in the DAC to save chip area and power consumption. The main drawback of the monotonic switching scheme is its large common mode shift and the associated comparator offset variation. Due to the limited headroom at the 0.6 V supply voltage, the conventional constant current biasing technique cannot be applied to the dynamic comparator. In this design, a common mode stabilizer is introduced to address this issue in low-voltage design. The effectiveness of this method is verified through both simulation and measurement results. Fabricated with 1P8M 0.13 μm CMOS technology, the proposed SAR ADC consumes 6.3 μW at 1 MS/s from a 0.6 V supply, and achieves 51.25 dB SNDR at the Nyquist frequency and FOM of 21 fJ/conversion-step. The core area is only 120×300 μm2. -

References

[1] Rajput S S, Jamuar S S. Low voltage analog circuit design techniques. IEEE Circuits Syst Mag, 2002, 2(1):24 doi: 10.1109/MCAS.2002.999703[2] Verma N, Chandrakasan A P. An ultra low energy 12-bit rate-resolution scalable SAR ADC for wireless sensor nodes. IEEE J Solid-State Circuits, 2007, 42(6):1196 doi: 10.1109/JSSC.2007.897157[3] Yip M, Chandrakasan A P. A resolution-reconfigurable 5-to-10-bit 0.4-to-1 V power scalable SAR ADC for sensor applications. IEEE J Solid-State Circuits, 2013, 48(6):1453 doi: 10.1109/JSSC.2013.2254551[4] Harpe P, Dolmans G, Philips K, et al. A 0.7 V 7-to-10 bit 0-to-2 MS/s flexible SAR ADC for ultra low-power wireless sensor nodes. IEEE European Solid-State Circuits Conference (ESSCIRC), 2012:373[5] Shikata A, Sekimoto R, Kuroda T, et al. A 0.5 V 1.1 MS/sec 6.3 fJ/conversion-step SAR-ADC with tri-level comparator in 40 nm CMOS. IEEE J Solid-State Circuits, 2012, 47(4):1022 doi: 10.1109/JSSC.2012.2185352[6] Lee S K, Park S J, Park H J, et al. A 1.3μW 0.6 V 8.7-ENOB successive approximation ADC in a 0.18μm CMOS. Symposium on VLSI Circuits Digest of Technical Papers, 2009:242 http://ieeexplore.ieee.org/document/5205346/[7] Lin G Y, Huang H Y, Hsieh C C, et al. A 0.05 mm2 0.6 V 500 kS/s 14.3 fJ/Conversion-step 11-bit two-step switching SAR ADC for 3-dimensional stacking CMOS imager. IEEE Asian Solid-State Circuits Conference (ASSCC), 2012:165[8] Liu C C, Chang S J, Huang G Y, et al. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J Solid-State Circuits, 2010, 45(4):731 doi: 10.1109/JSSC.2010.2042254[9] Zhu Y, Chan C H, Chio U F, et al. A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J Solid-State Circuits, 2010, 45(5):1111 http://ieeexplore.ieee.org/document/5482529/[10] Ginsburg B P, Chandrakasan A P. An energy-efficient charge recycling approach for a SAR converter with capacitive DAC. IEEE Int Symp Circuits and Systems (ISCAS), 2005:184 http://www.oalib.com/references/14375127[11] Liu C C, Chang S J, Huang G Y, et al. A 0.92 mW 10-bit 50-MS/s SAR ADC in 0.13μm CMOS process. Symposium on VLSI Circuits Digest of Technical Papers, 2009:236 http://ieeexplore.ieee.org/xpl/tocresult.jsp?sortType%3Dasc_p_Sequence%26filter%3DAND(p_IS_Number%3A6123555)%26rowsPerPage%3D75&pageNumber=1[12] Razavi B. Design of analog CMOS integrated circuits. New York: McGraw-Hill, Inc, 2000[13] Schinkel D, Mensink E, Klumperink E, et al. A double-tail latch-type voltage sense amplifier with 18 ps Setup+Hold time. IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2007:314 doi: 10.1007/s10470-011-9687-5[14] Chen S M, Brodersen R W. A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13-μm CMOS. IEEE J Solid-State Circuits, 2006, 41(12):2669 doi: 10.1109/JSSC.2006.884231[15] Promitzer G. 12-bit low-power fully differential noncalibrating successive approximation ADC with 1 MS/s. IEEE J Solid-State Circuits, 2001, 36(7):1138 doi: 10.1109/4.933473[16] Agnes A, Bonizzoni E, Malcovati P, et al. A 9.4-ENOB 1 V 3.8μW 100 kS/s SAR ADC with time-domain comparator. IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2008:246 doi: 10.1007/978-1-4614-1371-4_7 -

Proportional views

DownLoad:

DownLoad: