| Citation: |

Cong Shi, Zhe Chen, Jie Yang, Nanjian Wu, Zhihua Wang. A compact PE memory for vision chips[J]. Journal of Semiconductors, 2014, 35(9): 095002. doi: 10.1088/1674-4926/35/9/095002

****

C Shi, Z Chen, J Yang, N J Wu, Z H Wang. A compact PE memory for vision chips[J]. J. Semicond., 2014, 35(9): 095002. doi: 10.1088/1674-4926/35/9/095002.

|

-

Abstract

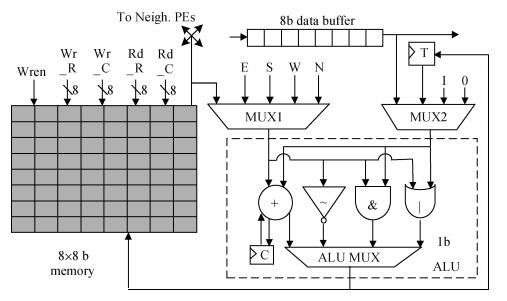

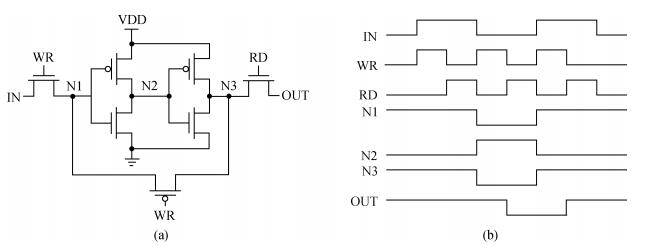

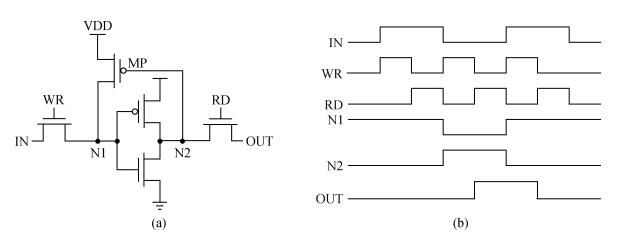

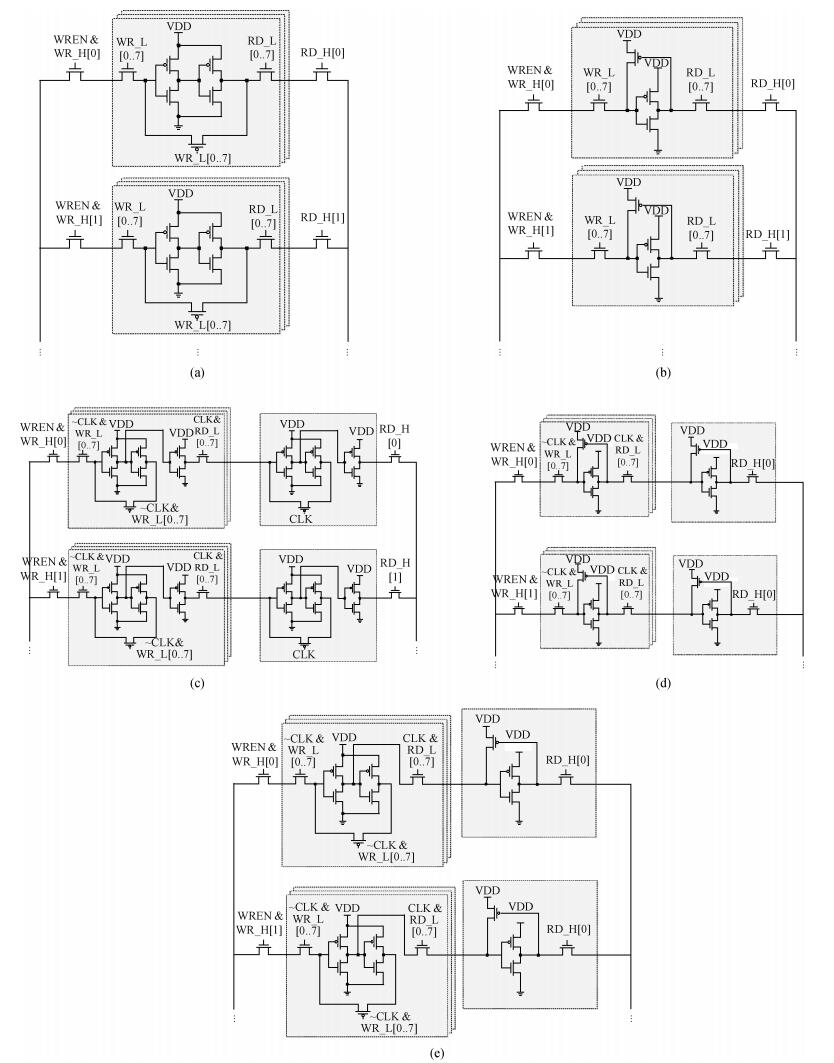

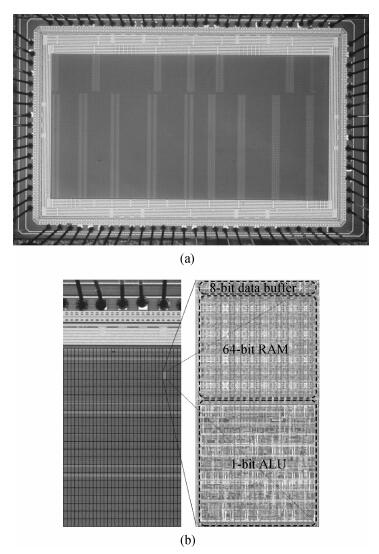

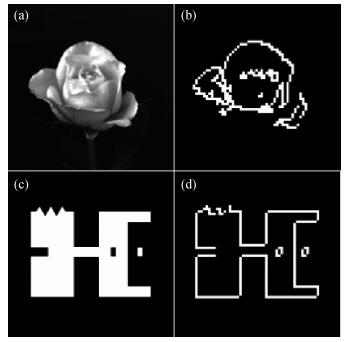

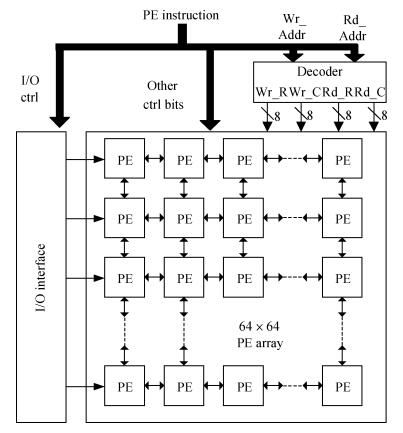

This paper presents a novel compact memory in the processing element (PE) for single-instruction multiple-data (SIMD) vision chips. The PE memory is constructed with 8×8 register cells, where one latch in the slave stage is shared by eight latches in the master stage. The memory supports simultaneous read and write on the same address in one clock cycle. Its compact area of 14.33 μm2/bit promises a higher integration level of the processor. A prototype chip with a 64×64 PE array is fabricated in a UMC 0.18 μm CMOS technology. Five types of the PE memory cell structure are designed and compared. The testing results demonstrate that the proposed PE memory architecture well satisfies the requirement of the vision chip in high-speed real-time vision applications, such as 1000 fps edge extraction.-

Keywords:

- vision chip,

- PE,

- memory architecture,

- SIMD,

- edge extraction

-

References

[1] Ishikawa M, Ogawa K, Komoro T. A CMOS vision chip with SIMD processing element array for 1 ms image processing. IEEE Int Solid State Circuits Conf (ISSCC), San Francisco, CA, 1999:206[2] Komuro T, Kagami S, Ishikawa M. A dynamically reconfigurable SIMD processor for a vision chip. IEEE J Solid-State Circuits, 2004, 39(1):265 doi: 10.1109/JSSC.2003.820876[3] Miao W, Lin Q, Zhang W, et al. A programmable SIMD vision chip for real-time vision applications. IEEE J Solid-State Circuits, 2008, 43(6):1470 doi: 10.1109/JSSC.2008.923621[4] Yamashita H, Sodini C. A CMOS imager with a programmable bit-serial column-parallel SIMD/MIMD processor. IEEE Trans Electron Devices, 2009, 56:2534 doi: 10.1109/TED.2009.2030718[5] Cheng C, Lin C, Li C, et al. iVisual:an intelligent visual sensor SoC with 2790 fps CMOS image sensor and 205 GOPS/W vision processor. IEEE J Solid-State Circuits, 2009, 44(1):127 doi: 10.1109/JSSC.2008.2007158[6] Lopich A, Dudek P. A SIMD cellular processor array vision chip with asynchronous processing capabilities. IEEE Trans Circuits Syst I:Regular Papers, 2011, 58(10):13[7] Zhang W, Fu Q, Wu N. A programmable vision chip based on multiple levels of parallel processors. IEEE J Solid-State Circuits, 2011, 46(9):2132 doi: 10.1109/JSSC.2011.2158024[8] Shi C, Yang J, Han Y, et al. A 1000 fps vision chip based on a dynamically reconfigurable hybrid architecture comprising a PE array and self-organizing map neural network. IEEE Int Solid State Circuits Conf (ISSCC), San Francisco, CA, 2014: 128 -

Proportional views

DownLoad:

DownLoad: