| Citation: |

Peng Qin, Jinbo Li, Jian Kang, Xiaoyong Li, Jianjun Zhou. Low noise frequency synthesizer with self-calibrated voltage controlled oscillator and accurate AFC algorithm[J]. Journal of Semiconductors, 2014, 35(9): 095007. doi: 10.1088/1674-4926/35/9/095007

****

P Qin, J B Li, J Kang, X Y Li, J J Zhou. Low noise frequency synthesizer with self-calibrated voltage controlled oscillator and accurate AFC algorithm[J]. J. Semicond., 2014, 35(9): 095007. doi: 10.1088/1674-4926/35/9/095007.

|

Low noise frequency synthesizer with self-calibrated voltage controlled oscillator and accurate AFC algorithm

DOI: 10.1088/1674-4926/35/9/095007

More Information

-

Abstract

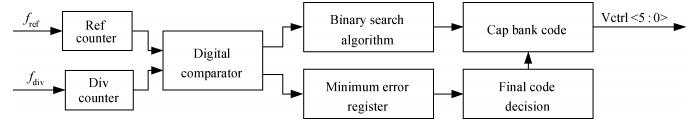

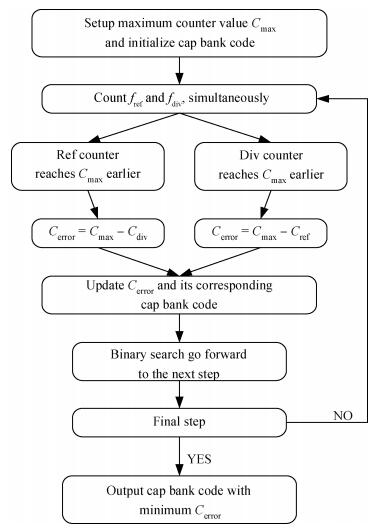

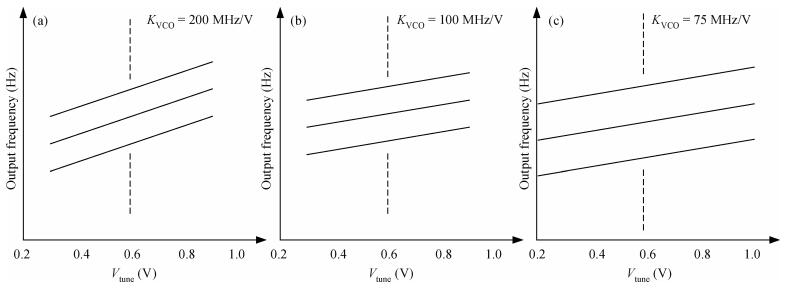

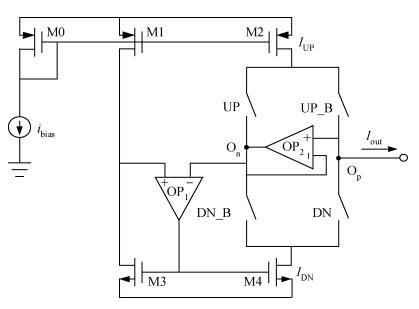

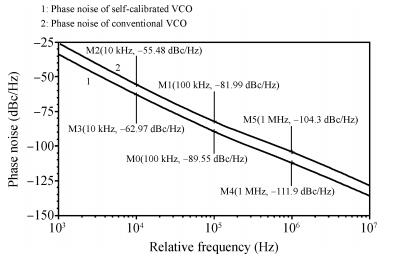

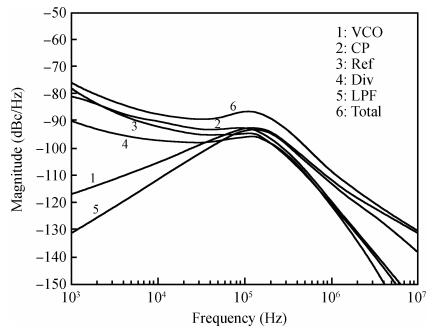

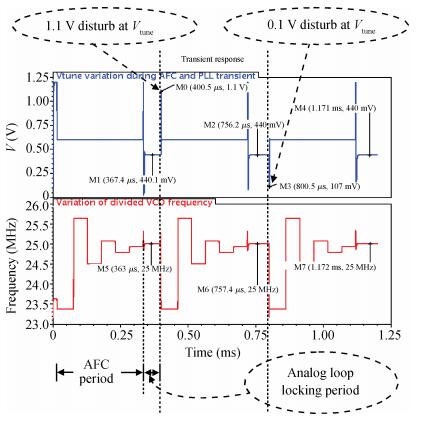

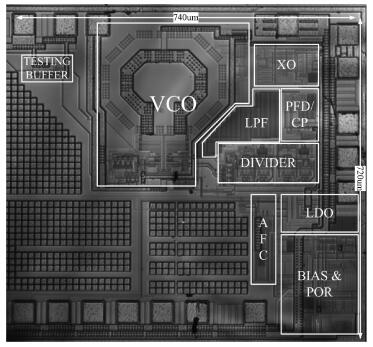

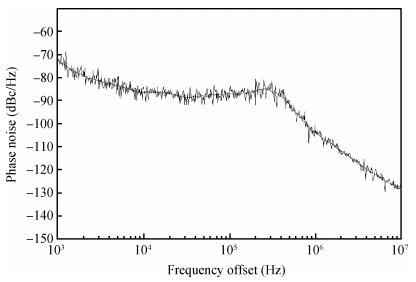

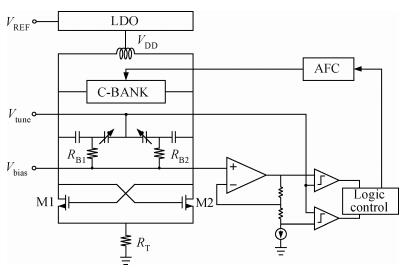

A low noise phase locked loop (PLL) frequency synthesizer implemented in 65 nm CMOS technology is introduced. A VCO noise reduction method suited for short channel design is proposed to minimize PLL output phase noise. A self-calibrated voltage controlled oscillator is proposed in cooperation with the automatic frequency calibration circuit, whose accurate binary search algorithm helps reduce the VCO tuning curve coverage, which reduces the VCO noise contribution at PLL output phase noise. A low noise, charge pump is also introduced to extend the tuning voltage range of the proposed VCO, which further reduces its phase noise contribution. The frequency synthesizer generates 9.75-11.5 GHz high frequency wide band local oscillator (LO) carriers. Tested 11.5 GHz LO bears a phase noise of -104 dBc/Hz at 1 MHz frequency offset. The total power dissipation of the proposed frequency synthesizer is 48 mW. The area of the proposed frequency synthesizer is 0.3 mm2, including bias circuits and buffers. -

References

[1] Peng Y S, Lu L H. A Ku-band frequency synthesizer in 0.18-μm CMOS technology. IEEE Microw Wireless Compon Lett, 2007, 17(4):256 doi: 10.1109/LMWC.2007.892953[2] Lee T H. The design of CMOS radio-frequency integrated circuits. 2nd ed. Cambridge University Press, 2004[3] Hegazi E, Abidi A A. Varactor characteristics, oscillator tuning curves, and AM-FM conversion. IEEE J Solid-State Circuits, 2003, 38(6):1033 doi: 10.1109/JSSC.2003.811968[4] Shin J, Shin H. A fast and high-precision VCO frequency calibration technique for wideband Δ Σ fractional-N frequency synthesizer. IEEE Trans Circuits Syst Ⅰ, Reg Papers, 2010, 57(7):1573 doi: 10.1109/TCSI.2009.2036057[5] Zargari M, Nathawad L Y, Samavati H, et al. A dual-band CMOS MIMO radio SoC for IEEE 802.11n wireless LAN. IEEE J Solid-State Circuits, 2008, 43(12):2882 doi: 10.1109/JSSC.2008.2005742[6] Terrovitis M, Mack M, Singh K, et al. A 3.2 to 4 GHz 0.25μm CMOS frequency synthesizer for IEEE 802.11a/b/g WLAN. ISSCC Dig Tech Papers, San Francisco, CA, February 2004:98 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=1332612[7] Rhee W. Design of high-performance CMOS charge pumps in phase-locked loops. IEEE International Symposium on Circuit and System, 1999, 2:545 http://ieeexplore.ieee.org/xpl/abstractKeywords.jsp?reload=true&arnumber=780807[8] Zanuso M, Levantino S, Samori C, et al. A wideband 3.6 GHz digital Δ Σ fractional-N PLL with phase interpolation divider and digital spur cancellation. IEEE J Solid-State Circuits, 2011, 46:627 doi: 10.1109/JSSC.2010.2104270[9] Lin D, Xu N, Rhee W, et al. An 11.7-17.2 GHz digitally-controlled oscillator in 65 nm CMOS for high-band UWB applications. ICSICT Dig Tech Papers, 2012:1 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=6466667[10] Richard O, Siligaris A, Badets F, et al. A 17.5-to-20.94 GHz and 35-to-41.88 GHz PLL in 65 nm CMOS for wireless HD applications. ISSCC Dig Tech Papers, 2010:252 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=5433941[11] Yang S, Chen W, Lu T. A 7.1 mW, 10 GHz all digital frequency synthesizer with dynamically reconfigured digital loop filter in 90 nm CMOS technology. IEEE J Solid-State Circuits, 2010, 45:578 doi: 10.1109/JSSC.2009.2039530 -

Proportional views

DownLoad:

DownLoad: