| Citation: |

Yuejun Zhang, Zhidi Jiang, Pengjun Wang, Xuelong Zhang. High accuracy digital aging monitor based on PLL-VCO circuit[J]. Journal of Semiconductors, 2015, 36(1): 015004. doi: 10.1088/1674-4926/36/1/015004

****

Y J Zhang, Z D Jiang, P J Wang, X L Zhang. High accuracy digital aging monitor based on PLL-VCO circuit[J]. J. Semicond., 2015, 36(1): 015004. doi: 10.1088/1674-4926/36/1/015004.

|

High accuracy digital aging monitor based on PLL-VCO circuit

DOI: 10.1088/1674-4926/36/1/015004

More Information

-

Abstract

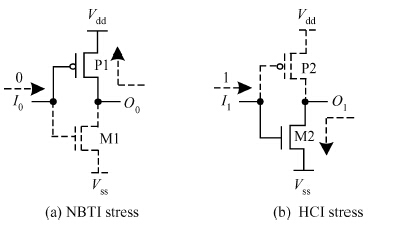

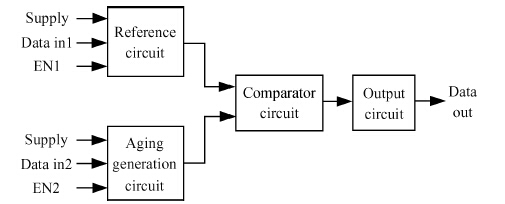

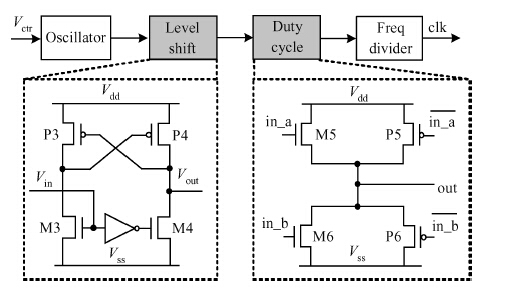

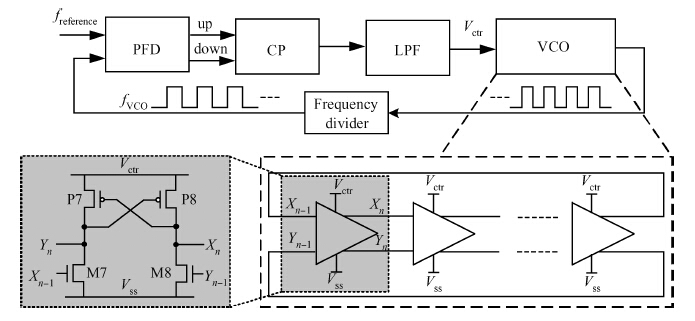

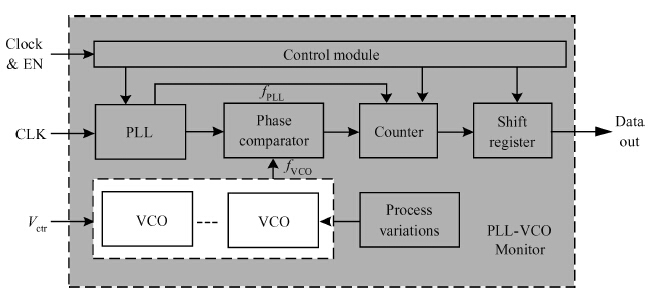

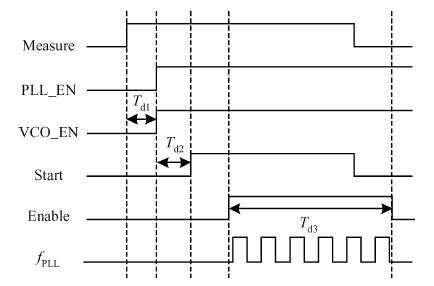

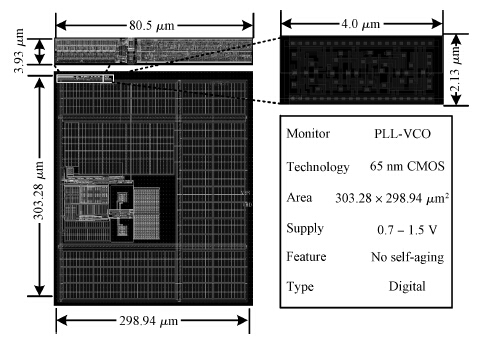

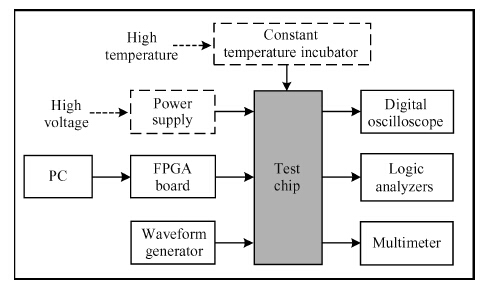

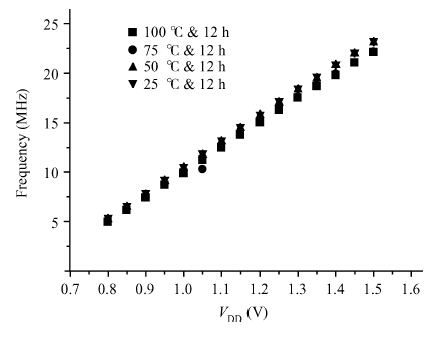

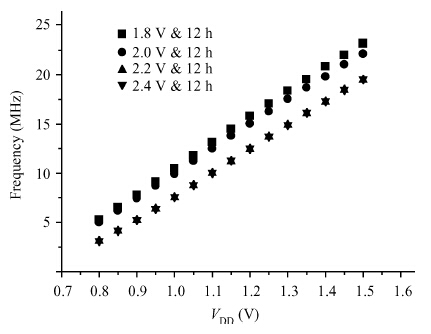

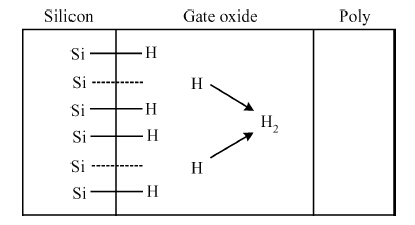

As the manufacturing process is scaled down to the nanoscale, the aging phenomenon significantly affects the reliability and lifetime of integrated circuits. Consequently, the precise measurement of digital CMOS aging is a key aspect of nanoscale aging tolerant circuit design. This paper proposes a high accuracy digital aging monitor using phase-locked loop and voltage-controlled oscillator (PLL-VCO) circuit. The proposed monitor eliminates the circuit self-aging effect for the characteristic of PLL, whose frequency has no relationship with circuit aging phenomenon. The PLL-VCO monitor is implemented in TSMC low power 65 nm CMOS technology, and its area occupies 303.28 × 298.94 μm2. After accelerating aging tests, the experimental results show that PLL-VCO monitor improves accuracy about high temperature by 2.4% and high voltage by 18.7%.-

Keywords:

- nanoscale,

- aging monitor,

- PLL-VCO,

- circuit design

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] -

Proportional views

DownLoad:

DownLoad: