| Citation: |

Wei Liu, Tingcun Wei, Bo Li, Panjie Guo, Yongcai Hu. A 12-bit 1 MS/s SAR-ADC for multi-channel CdZnTe detectors[J]. Journal of Semiconductors, 2015, 36(4): 045007. doi: 10.1088/1674-4926/36/4/045007

****

W Liu, T C Wei, B Li, P J Guo, Y C Hu. A 12-bit 1 MS/s SAR-ADC for multi-channel CdZnTe detectors[J]. J. Semicond., 2015, 36(4): 045007. doi: 10.1088/1674-4926/36/4/045007.

|

A 12-bit 1 MS/s SAR-ADC for multi-channel CdZnTe detectors

DOI: 10.1088/1674-4926/36/4/045007

More Information

-

Abstract

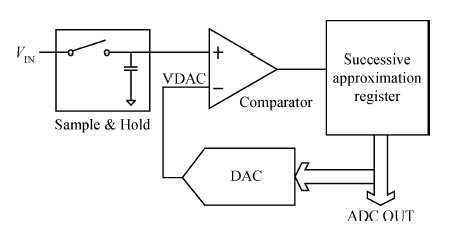

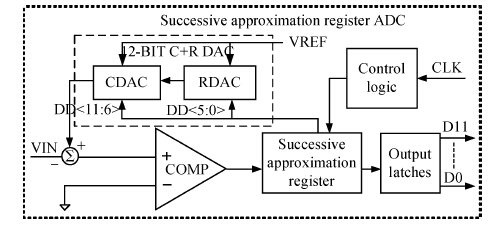

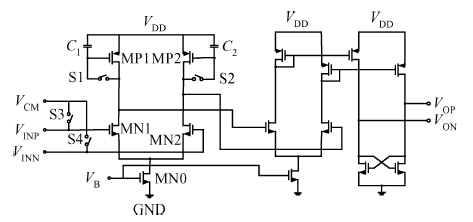

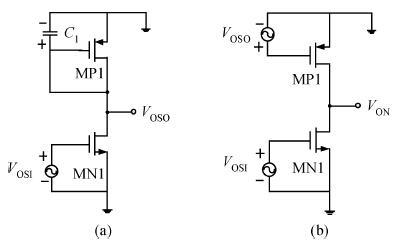

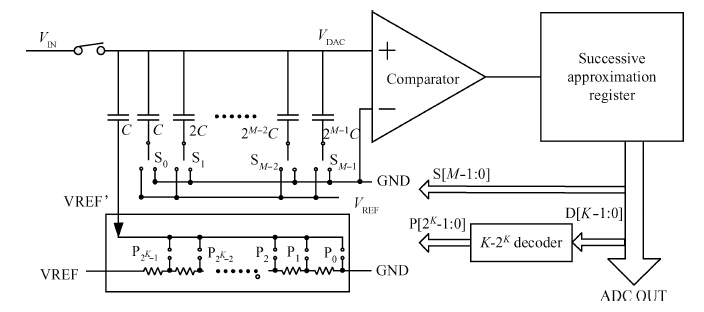

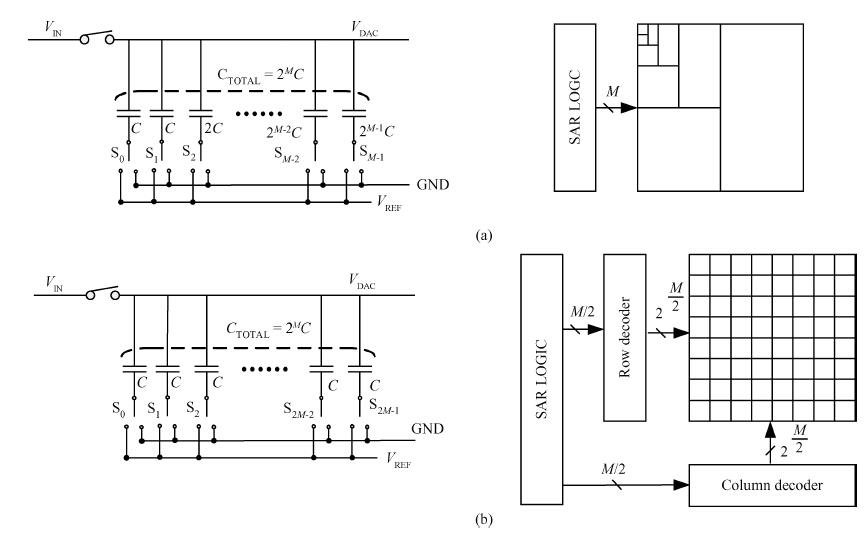

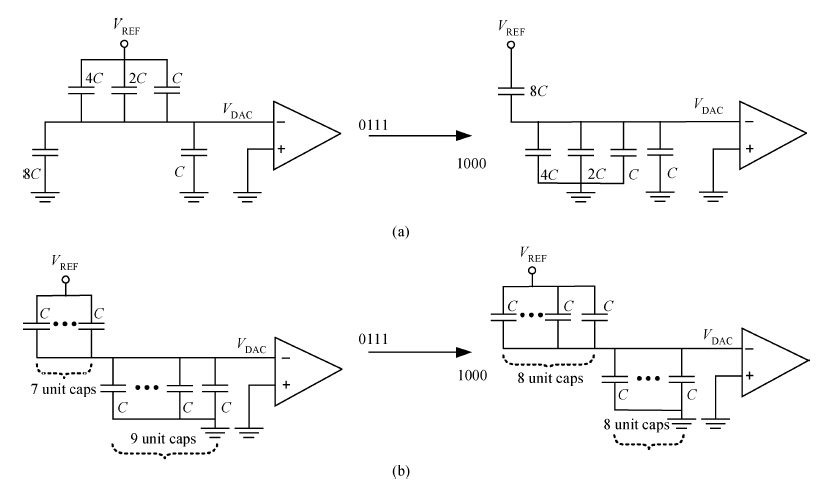

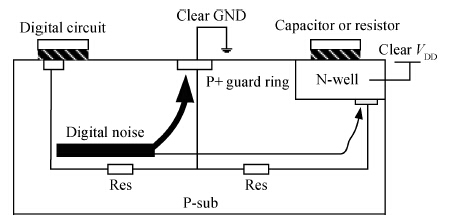

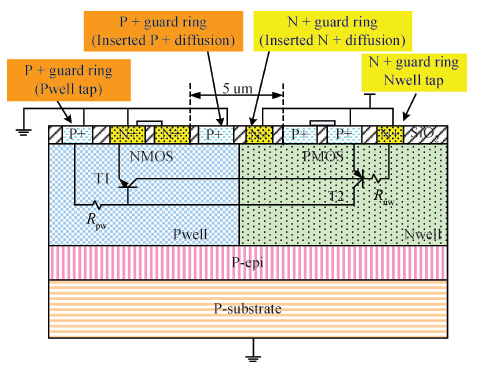

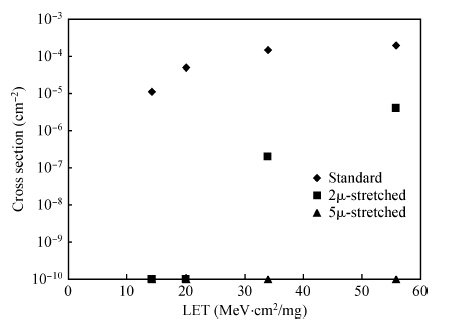

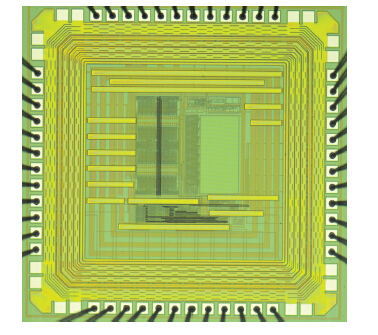

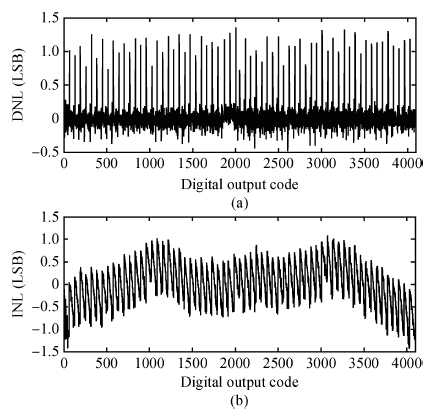

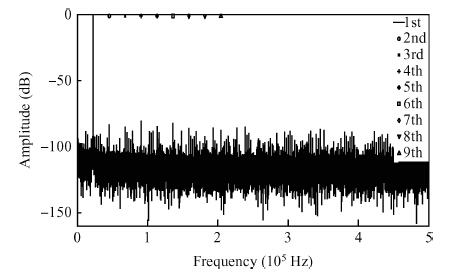

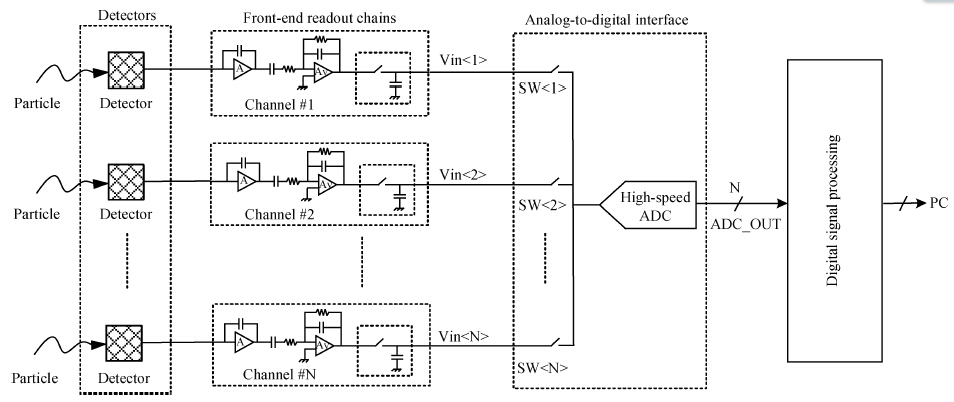

This paper presents a low power, area-efficient and radiation-hardened 12-bit 1 MS/s successive approximation register (SAR) analog-to-digital converter (ADC) for multi-channel CdZnTe (CZT) detector applications. In order to improve the SAR-ADC's accuracy, a novel comparator is proposed in which the offset voltage is self-calibrated and also a new architecture for the unit capacitor array is proposed to reduce the capacitance mismatches in the charge-redistribution DAC. The ability to radiation-harden the SAR-ADC is enhanced through circuit and layout design technologies. The prototype chip was fabricated using a TSMC 0.35 μm 2P4M CMOS process. At a 3.3/5 V power supply and a sampling rate of 1 MS/s, the proposed SAR-ADC achieves a peak signal to noise and distortion ratio (SINAD) of 67.64 dB and consumes only 10 mW power. The core of the prototype chip occupies an active area of 1180 × 1080 μm2.-

Keywords:

- SAR,

- ADC,

- radiation-hardness,

- low power,

- CZT detectors

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] -

Proportional views

DownLoad:

DownLoad: