| Citation: |

Yong Wang, Jianyun Zhang, Rui Yin, Yuhang Zhao, Wei Zhang. A 0.23 pJ 11.05-bit ENOB 125-MS/s pipelined ADC in a 0.18 μ m CMOS process[J]. Journal of Semiconductors, 2015, 36(5): 055013. doi: 10.1088/1674-4926/36/5/055013

****

Y Wang, J Y Zhang, R Yin, Y H Zhao, W Zhang. A 0.23 pJ 11.05-bit ENOB 125-MS/s pipelined ADC in a 0.18 μ m CMOS process[J]. J. Semicond., 2015, 36(5): 055013. doi: 10.1088/1674-4926/36/5/055013.

|

A 0.23 pJ 11.05-bit ENOB 125-MS/s pipelined ADC in a 0.18 μ m CMOS process

DOI: 10.1088/1674-4926/36/5/055013

More Information

-

Abstract

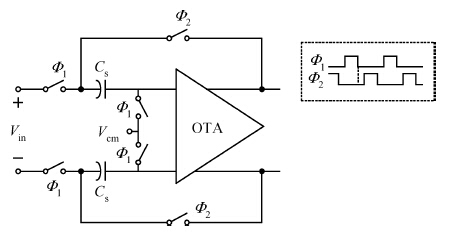

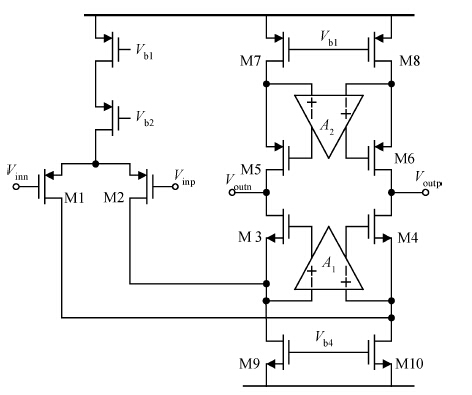

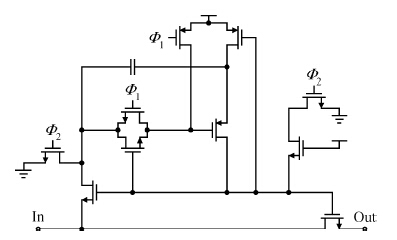

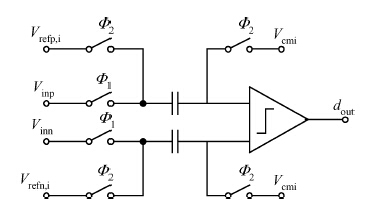

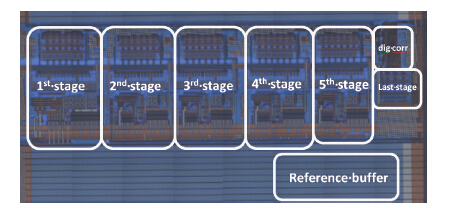

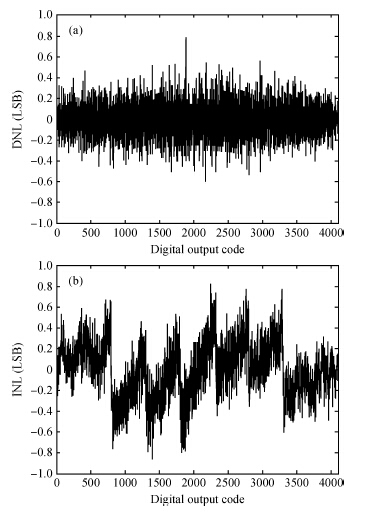

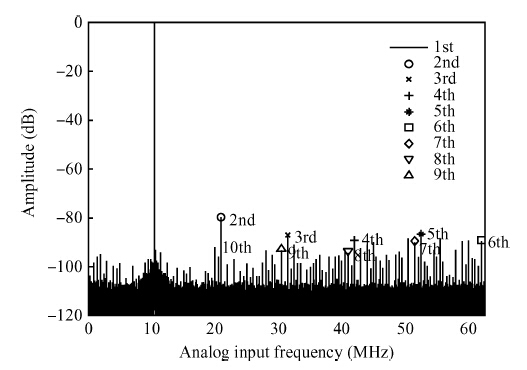

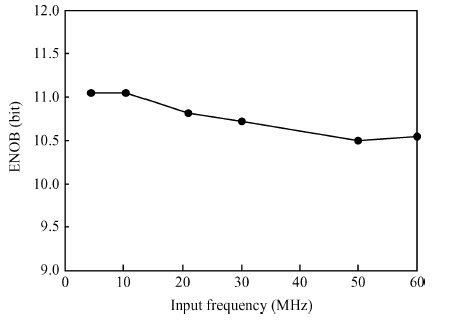

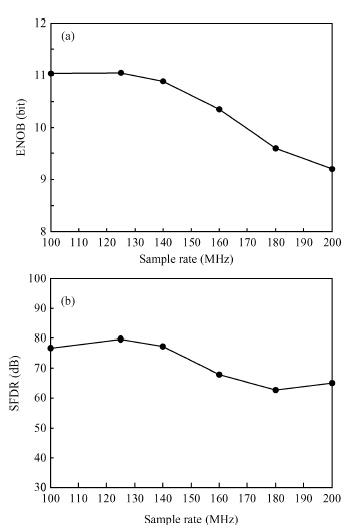

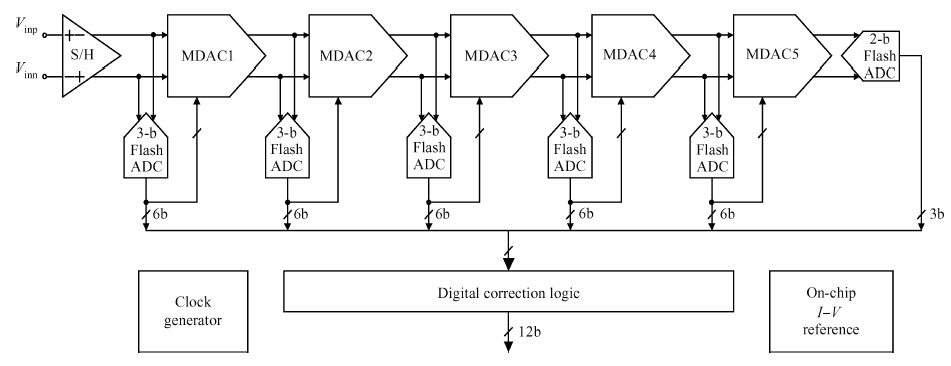

This paper describes a 12-bit 125-MS/s pipelined analog-to-digital converter (ADC) that is implemented in a 0.18 μ m CMOS process. A gate-bootstrapping switch is used as the bottom-sampling switch in the first stage to enhance the sampling linearity. The measured differential and integral nonlinearities of the prototype are less than 0.79 least significant bit (LSB) and 0.86 LSB, respectively, at the full sampling rate. The ADC exhibits an effective number of bits (ENOB) of more than 11.05 bits at the input frequency of 10.5 MHz. The ADC also achieves a 10.5 bits ENOB with the Nyquist input frequency at the full sample rate. In addition, the ADC consumes 62 mW from a 1.9 V power supply and occupies 1.17 mm2, which includes an on-chip reference buffer. The figure-of-merit of this ADC is 0.23 pJ/step. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] -

Proportional views

DownLoad:

DownLoad: