| Citation: |

Zonghua Zheng, Lingling Sun, Jun Liu, Shengzhou Zhang. A novel loss compensation technique analysis and design for 60 GHz CMOS SPDT switch[J]. Journal of Semiconductors, 2016, 37(1): 015001. doi: 10.1088/1674-4926/37/1/015001

****

Z H Zheng, L L Sun, J Liu, S Z Zhang. A novel loss compensation technique analysis and design for 60 GHz CMOS SPDT switch[J]. J. Semicond., 2016, 37(1): 015001. doi: 10.1088/1674-4926/37/1/015001.

|

A novel loss compensation technique analysis and design for 60 GHz CMOS SPDT switch

DOI: 10.1088/1674-4926/37/1/015001

More Information

-

Abstract

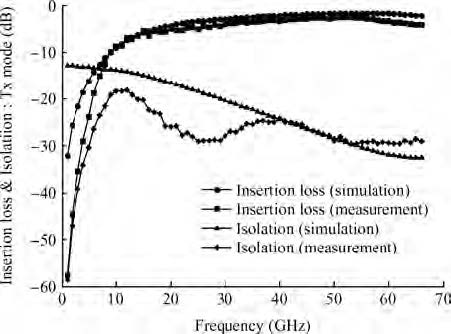

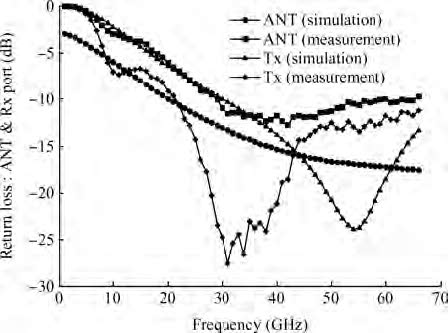

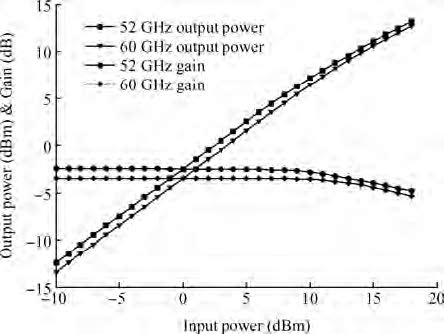

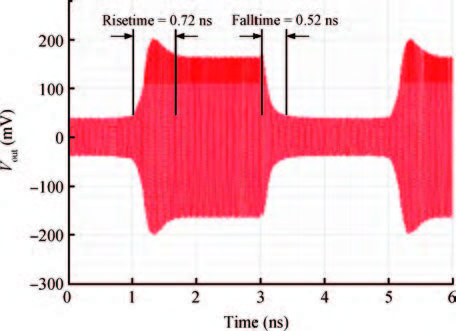

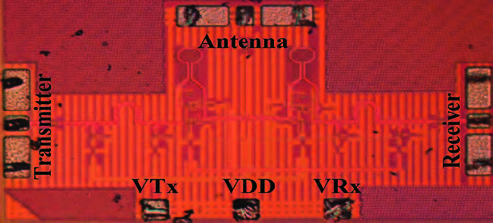

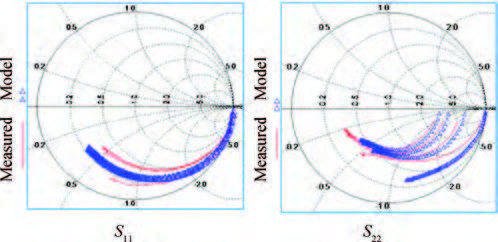

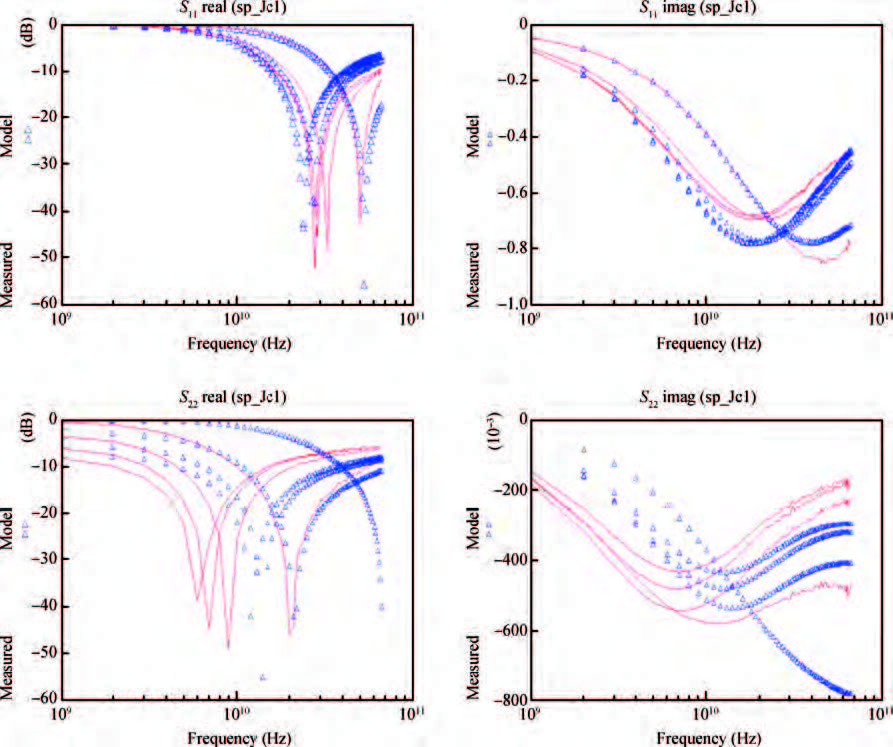

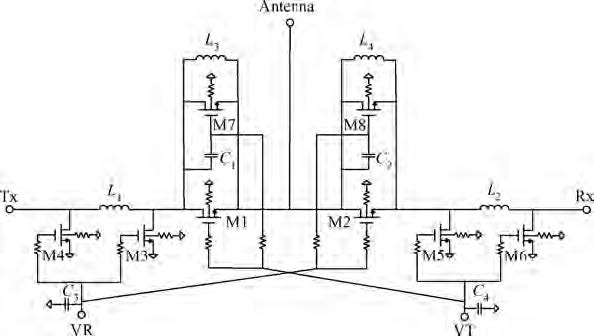

A novel loss compensation technique for a series-shunt single-pole double-throw (SPDT) switch is presented operating in the 60 GHz. The feed-forward compensation network which is composed of an NMOS, a couple capacitance and a shunt inductance can reduce the impact of the feed forward capacitance to reduce the insertion loss and improve the isolation of the SPDT switch. The measured insertion loss and isolation characteristics of the switch somewhat deviating from the 60 GHz are analyzed revealing that the inaccuracy of the MOS model can greatly degrade the performance of the switch. The switch is implemented in TSMC 90-nm CMOS process and exhibits an isolation of above 27 dB at transmitter mode, and the insertion loss of 1.8-3 dB at 30-65 GHz by layout simulation. The measured insertion loss is 2.45 dB at 52 GHz and keeps<4 dB at 30-64 GHz. The measured isolation is better than 25 dB at 30-64 GHz and the measured return loss is better than 10 dB at 30-65 GHz. A measured input 1 dB gain compression point of the switch is 13 dBm at 52 GHz and 15 dBm at 60 GHz. The simulated switching speed with rise time and fall time are 720 and 520 ps, respectively. The active chip size of the proposed switch is 0.5×0.95 mm2. -

References

[1] [2] [3] [4] [5] [6] [7] [8] -

Proportional views

DownLoad:

DownLoad: