| Citation: |

S. Intekhab Amin, R. K. Sarin. Direct tunneling gate current model for symmetric double gate junctionless transistor with SiO2/high-k gate stacked dielectric[J]. Journal of Semiconductors, 2016, 37(3): 034001. doi: 10.1088/1674-4926/37/3/034001

****

S. I. Amin, R. K. Sarin. Direct tunneling gate current model for symmetric double gate junctionless transistor with SiO2/high-k gate stacked dielectric[J]. J. Semicond., 2016, 37(3): 034001. doi: 10.1088/1674-4926/37/3/034001.

|

Direct tunneling gate current model for symmetric double gate junctionless transistor with SiO2/high-k gate stacked dielectric

DOI: 10.1088/1674-4926/37/3/034001

More Information

-

Abstract

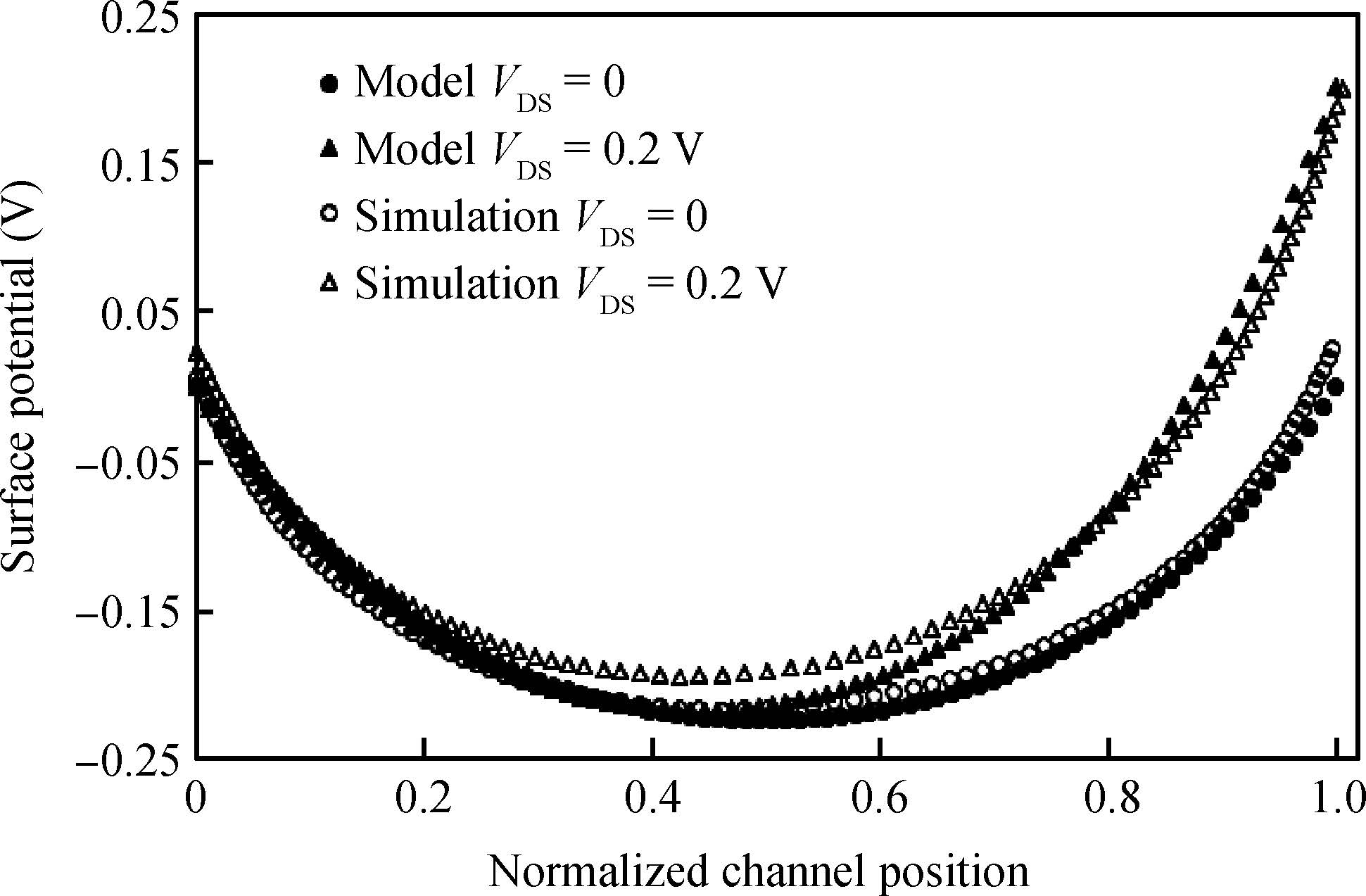

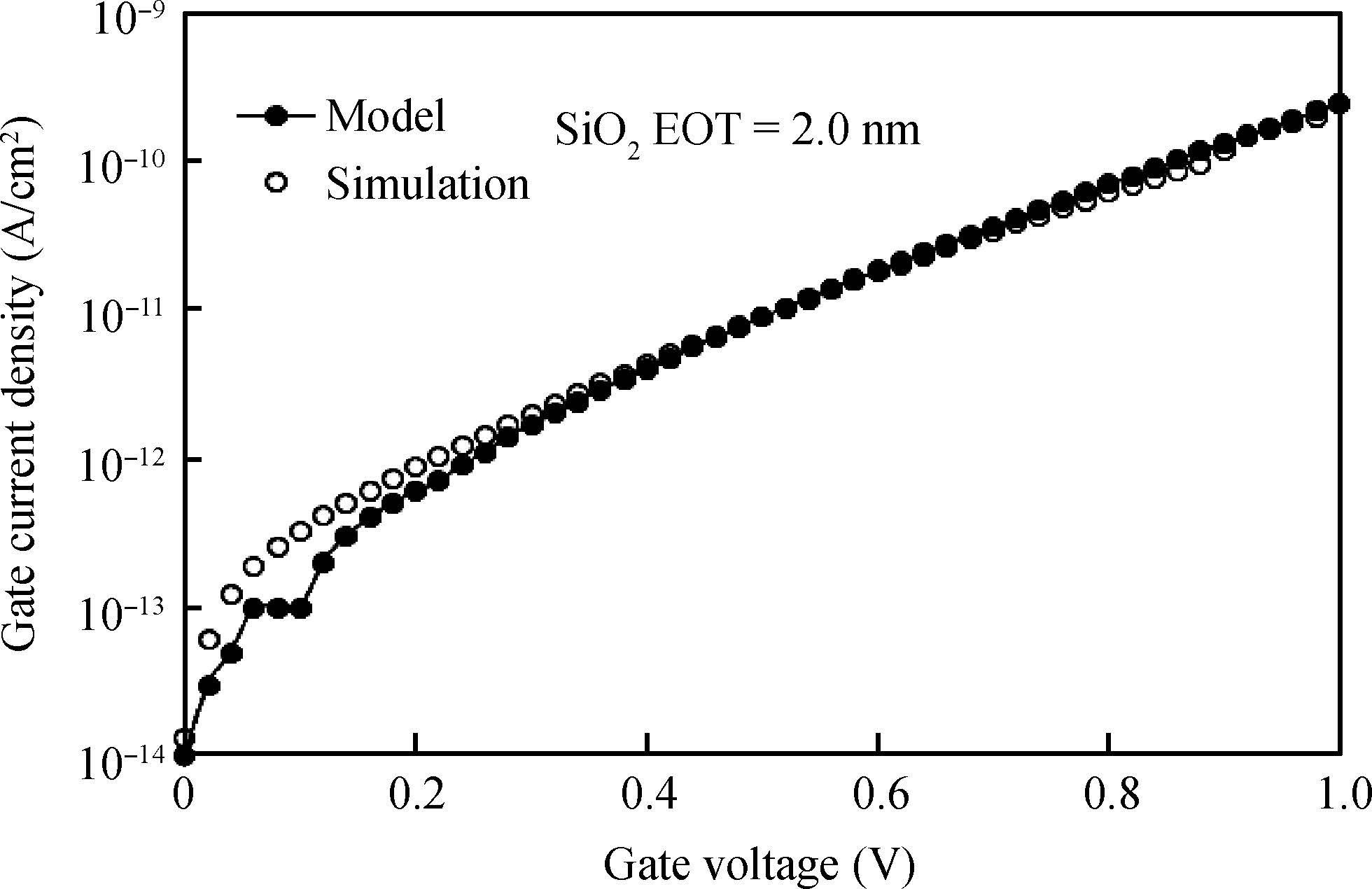

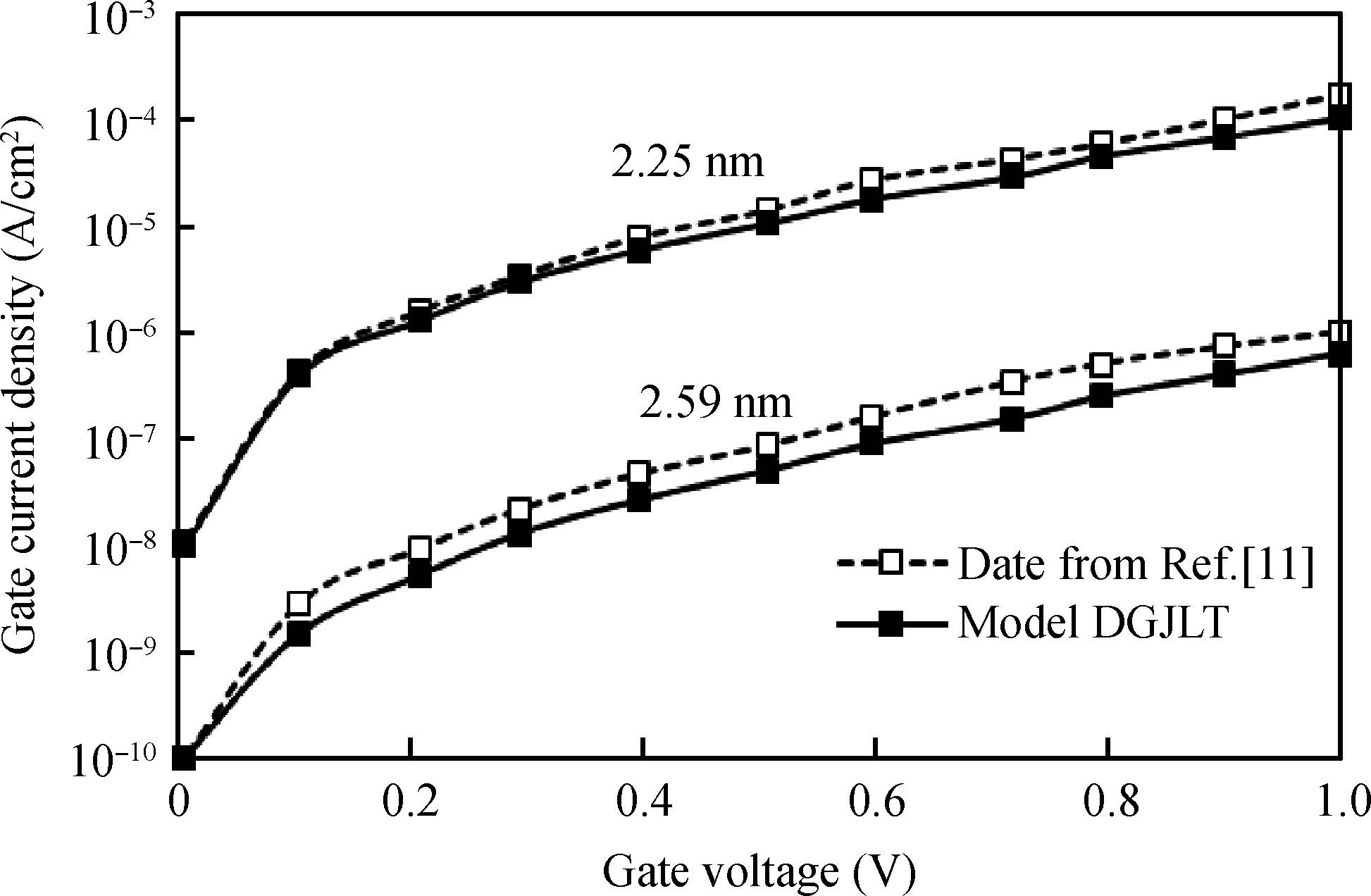

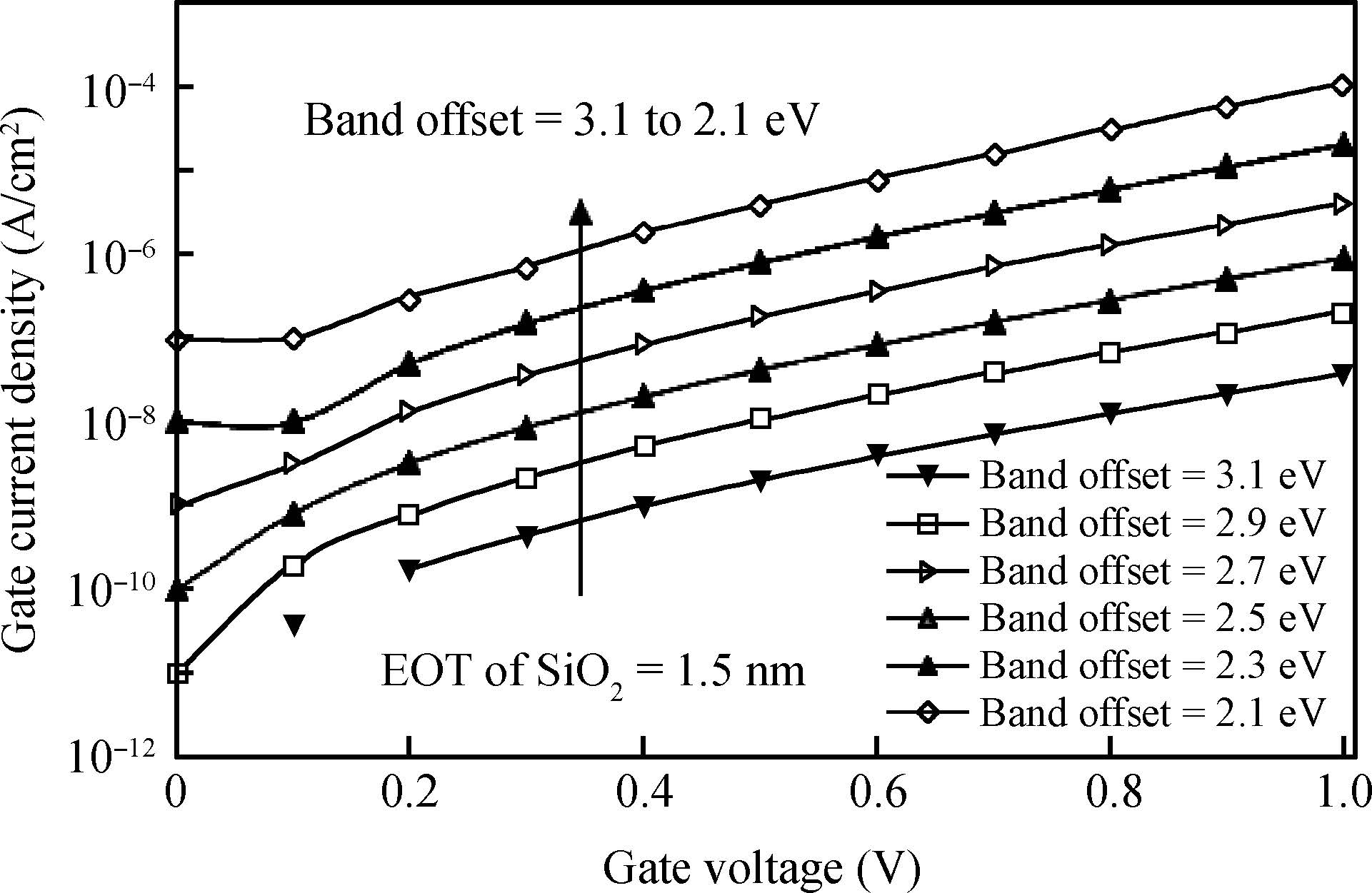

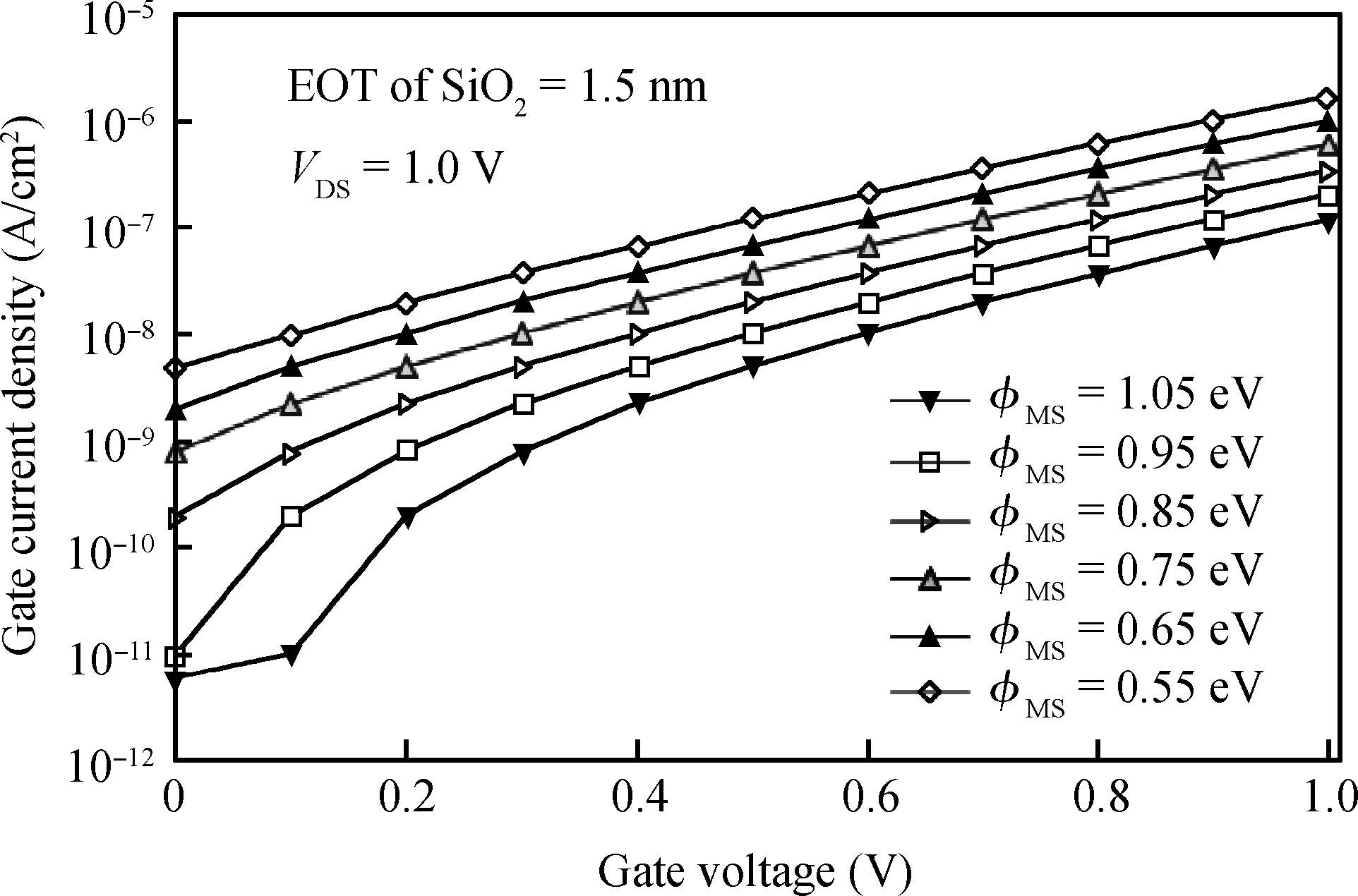

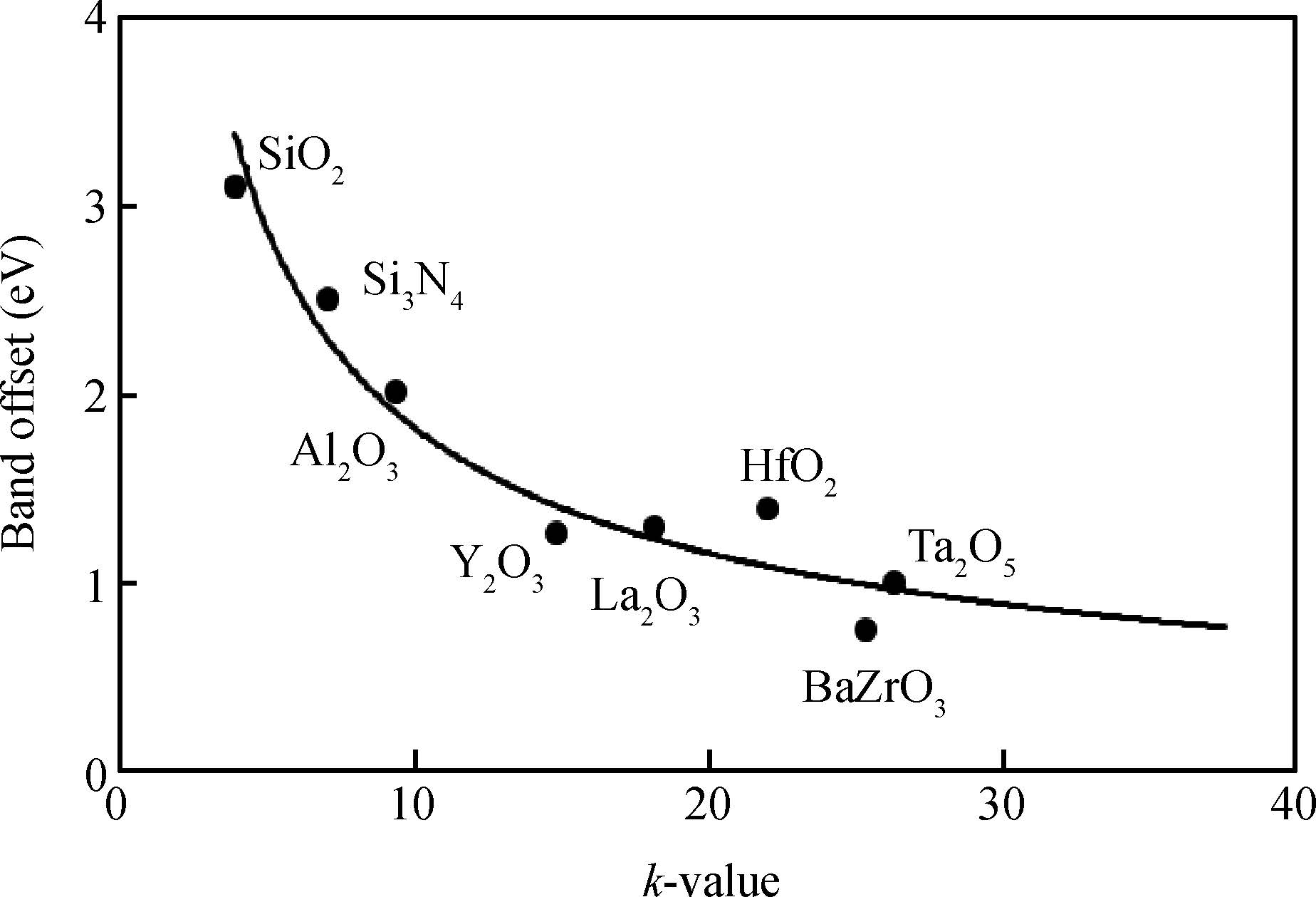

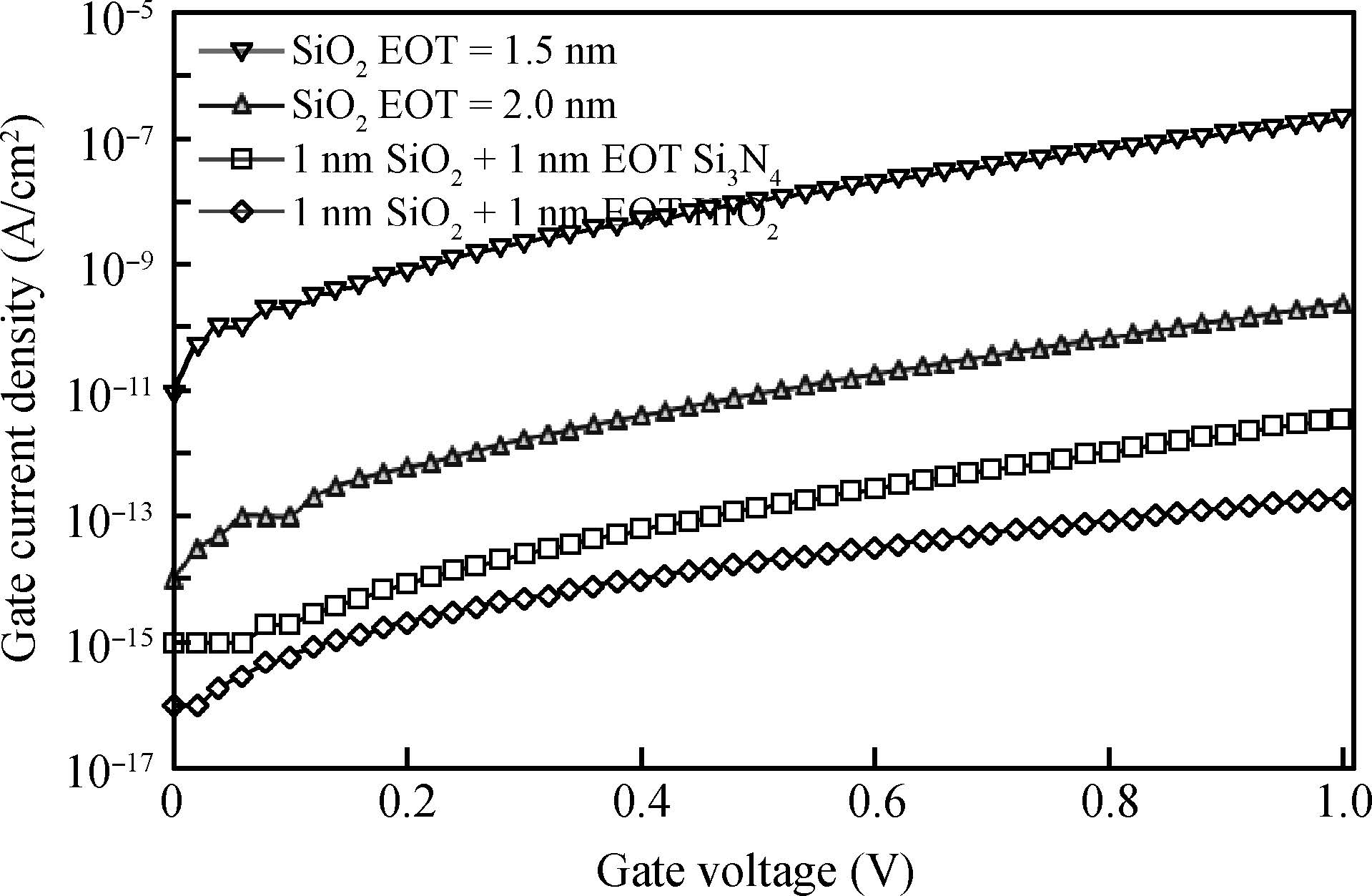

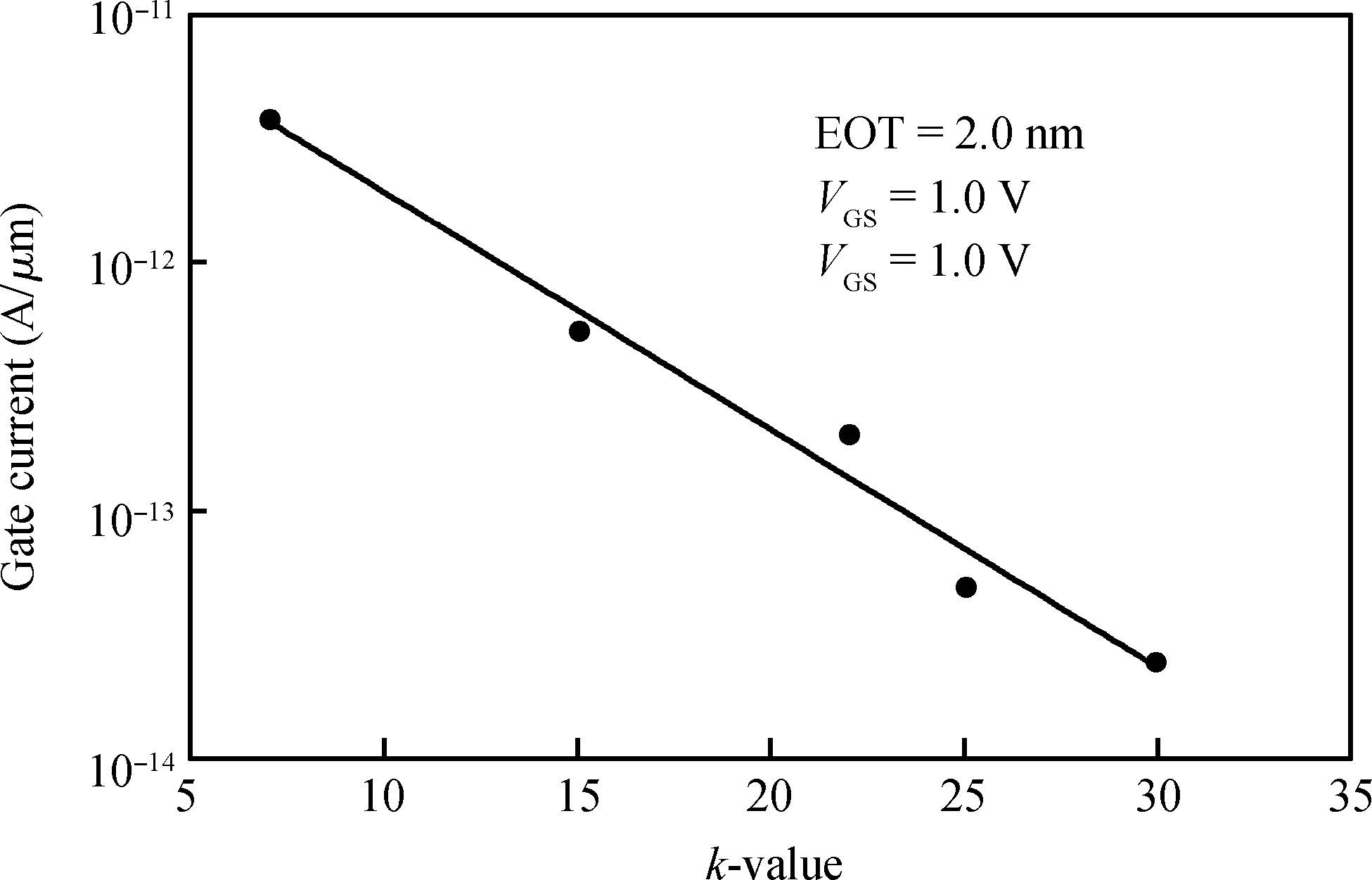

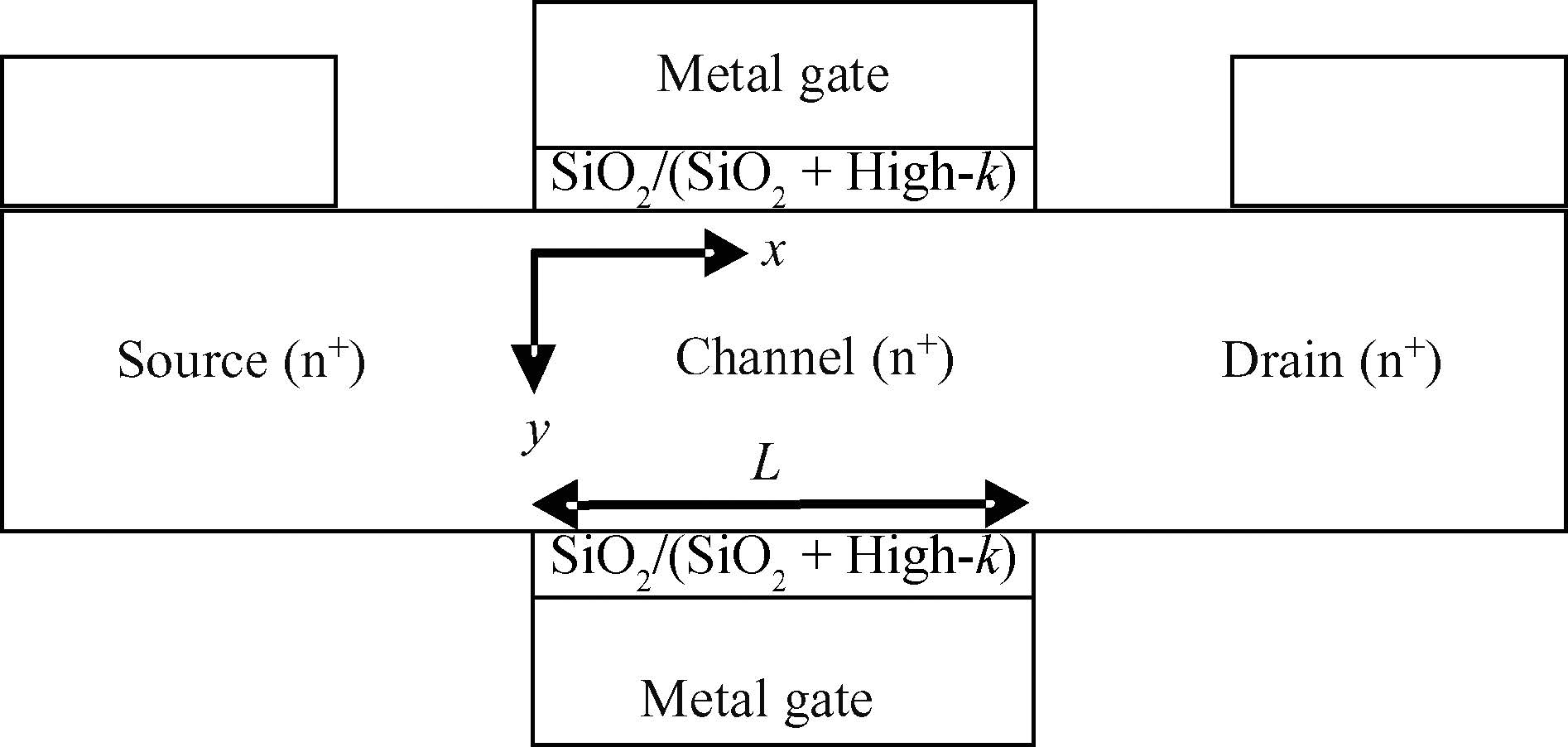

A junctionless transistor is emerging as a most promising device for the future technology in the decananometer regime. To explore and exploit the behavior completely, the understanding of gate tunneling current is of great importance. In this paper we have explored the gate tunneling current of a double gate junctionless transistor(DGJLT) for the first time through an analytical model, to meet the future requirement of expected high-k gate dielectric material that could replace SiO2. We therefore present the high-k gate stacked architecture of the DGJLT to minimize the gate tunneling current. This paper also demonstrates the impact of conduction band offset, workfunction difference and k-values on the tunneling current of the DGJLT. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] -

Proportional views

DownLoad:

DownLoad: