| Citation: |

Xiuju He, Xian Gu, Weitao Li, Hanjun Jiang, Fule Li, Zhihua Wang. An 11-bit 200 MS/s subrange SAR ADC with low-cost integrated reference buffer[J]. Journal of Semiconductors, 2017, 38(10): 105007. doi: 10.1088/1674-4926/38/10/105007

****

X J He, X Gu, W T Li, H J Jiang, F L Li, Z H Wang. An 11-bit 200 MS/s subrange SAR ADC with low-cost integrated reference buffer[J]. J. Semicond., 2017, 38(10): 105007. doi: 10.1088/1674-4926/38/10/105007.

|

An 11-bit 200 MS/s subrange SAR ADC with low-cost integrated reference buffer

DOI: 10.1088/1674-4926/38/10/105007

More Information

-

Abstract

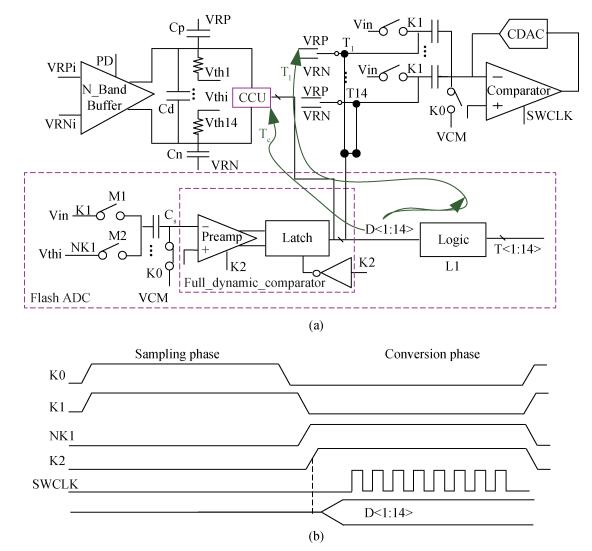

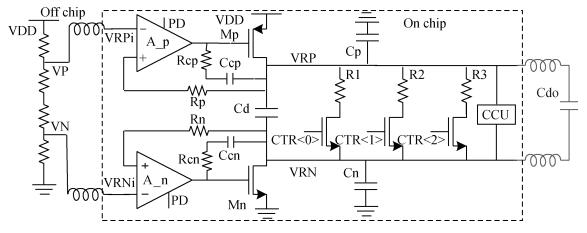

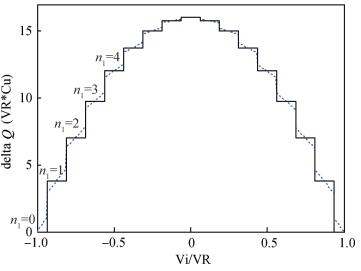

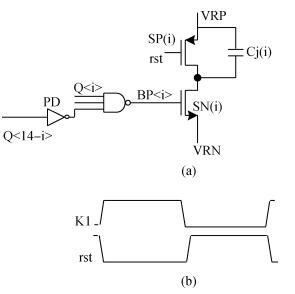

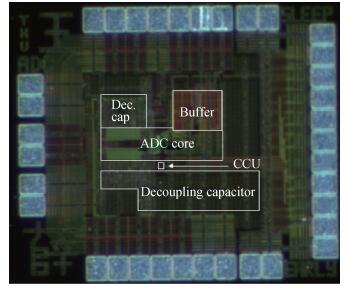

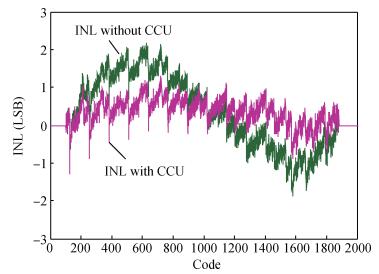

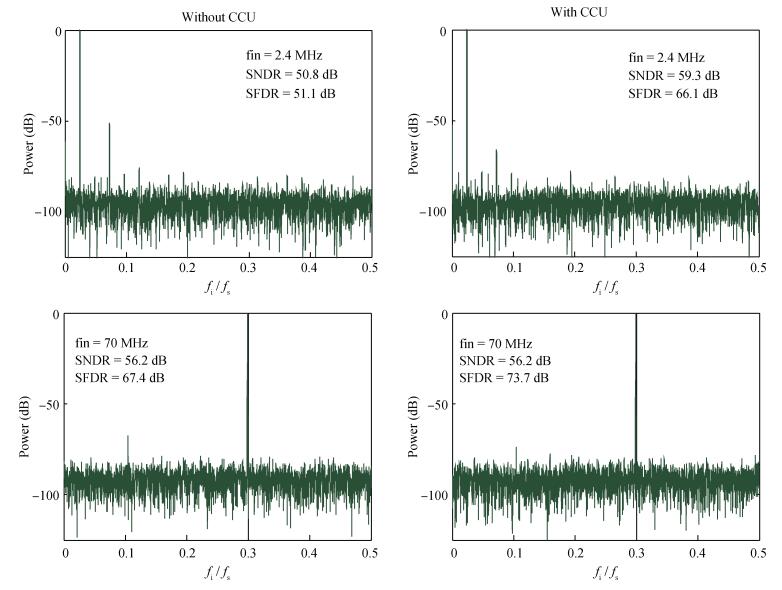

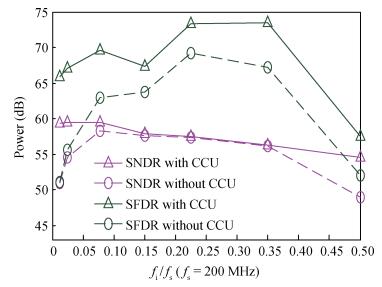

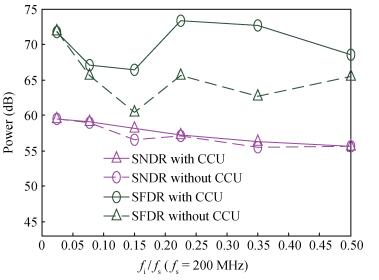

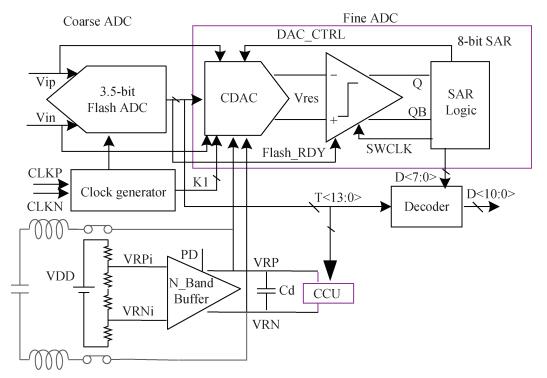

This paper presents an 11-bit 200 MS/s subrange SAR ADC with an integrated reference buffer in 65 nm CMOS. The proposed ADC employs a 3.5-bit flash ADC for coarse conversion, and a compact timing scheme at the flash/SAR boundary to speed up the conversion. The flash decision is used to control charge compensating for the reference voltage to reduce its input-dependent fluctuation. Measurement results show that the fabricated ADC has achieved significant improvement by applying the reference charge compensation. In addition, the ADC achieves a maximum signal-to-noise-and-distortion ratio of 59.3 dB at 200 MS/s. It consumes 3.91 mW from a 1.2 V supply, including the reference buffer. -

References

[1] Ding M, Harpe P, Liu Y H, et al. A 46μW 13 b 6.4 MS/s SAR ADC with background mismatch and offset calibration. IEEE J Solid-State Circuits, 2016, 52:423 https://www.narcis.nl/publication/RecordID/oai%3Alibrary.tue.nl%3A863979[2] Delgado-Restituto M, Carrasco-Robles M, Fiorelli R, et al. A 76 nW, 4 kS/s 10-bit SAR ADC with offset cancellation for biomedical applications. IEEE Asia Pacific Conference on Circuits and Systems, 2016:421 doi: 10.1007/s10470-015-0591-2[3] Liu C C, Huang M C, Tu Y H. A 12 bit 100 MS/s SAR-assisted digital-slope ADC. IEEE J Solid-State Circuits, 2016, 51(12):2941 doi: 10.1109/JSSC.2016.2591822[4] Muratore D G, Bonizzoni E, Maloberti F. A pipeline ADC for very high conversion rates. IEEE International Symposium on Circuits and Systems, 2016:1446 http://ieeexplore.ieee.org/document/7527529/[5] Chen H W, Liu Y H, Lin Y H, et al. A 3 mW 12 b 10 MS/s subrange SAR ADC. IEEE Asian Solid-State Circuits Conference, 2009:153 doi: 10.1088/1674-4926/37/7/075005[6] Lee C H, Hou C H, Huang C P, et al. A 2.5-bit/cycle 10-bit 160-MS/s SAR ADC in 90-nm CMOS process. International Symposium on VLSI Design, Automation and Test (VLSI-DAT), 2016:1 http://www.doc88.com/p-0791363464543.html[7] Gao J, Li G, Huang L, et al. An amplifier-free pipeline-SAR ADC architecture with enhanced speed and energy efficiency. IEEE Trans Circuits Syst Ⅱ, 2016, 63(4):341 doi: 10.1109/TCSII.2015.2503705[8] Daly D C, Chandrakasan A P. A 6-bit, 0.2 V to 0.9 V highly digital flash ADC with comparator redundancy. IEEE J Solid-State Circuits, 2009, 44(11):3030 doi: 10.1109/JSSC.2009.2032699[9] Lin Y Z, Liu C C, Huang G Y, et al. A 9-bit 150-MS/s subrange ADC based on SAR architecture in 90-nm CMOS. IEEE Trans Circuits Syst I, 2013, 60(3):570 doi: 10.1109/TCSI.2012.2215756[10] Wei S S, Ju Y, Li F L, et al. An 11-bit 200 MS/s subrange SAR ADC with charge-compensation-based reference buffer. IEEE International New Circuits and Systems Conference, 2016:1 doi: 10.1088/1674-4926/37/7/075005/meta[11] Li W T, Li F L, Yang C Y, et al. A power efficient reference buffer with wide swing for switched-capacitor ADC. Microelectron J, 2015, 46:410 doi: 10.1016/j.mejo.2015.03.005[12] Li W, Li F, Yang C, et al. An 85 mW 14-bit 150 MS/s pipelined ADC with a merged first and second MDAC. Chin Commun, 2015, 12(5):14 doi: 10.1109/CC.2015.7112040[13] van Elzakker M, van Tuijl E, Geraedts P, et al. A 10-bit charge-redistribution ADC consuming 1.9μW at 1 MS/s. IEEE J SolidState Circuits, 2010, 45(5):1007 doi: 10.1109/JSSC.2010.2043893[14] Wang Y, Li F, Xue C, et al. Charge-compensation-based reference technique for switched-capacitor ADCs. IEEE International Symposium on Circuits and Systems, 2015:2257 http://ieeexplore.ieee.org/document/7169132/[15] Wei H, Chan C H, Chio U F, et al. A 0.024 mm2 8 b 400 MS/s SAR ADC with 2b/cycle and resistive DAC in 65 nm CMOS. IEEE International Solid-State Circuits Conference, 2011:188 http://www.fst.umac.mo/en/staff/fstsws.html -

Proportional views

DownLoad:

DownLoad: