| Citation: |

Han Wang, Chao Gou, Kai Luo. A fully on-chip fast-transient NMOS low dropout voltage regulator with quasi floating gate pass element[J]. Journal of Semiconductors, 2017, 38(4): 045002. doi: 10.1088/1674-4926/38/4/045002

****

H Wang, C Gou, K Luo. A fully on-chip fast-transient NMOS low dropout voltage regulator with quasi floating gate pass element[J]. J. Semicond., 2017, 38(4): 045002. doi: 10.1088/1674-4926/38/4/045002.

|

A fully on-chip fast-transient NMOS low dropout voltage regulator with quasi floating gate pass element

DOI: 10.1088/1674-4926/38/4/045002

More Information

-

Abstract

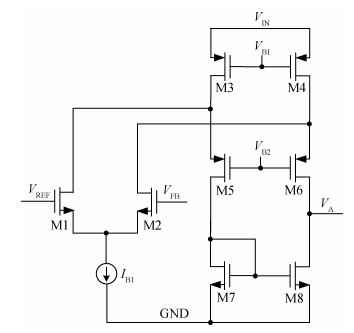

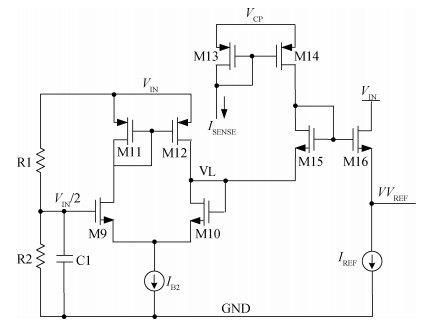

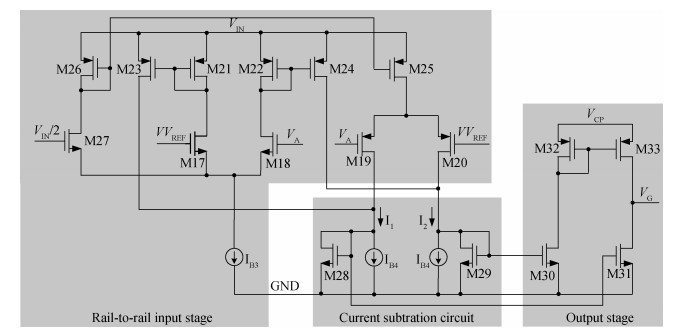

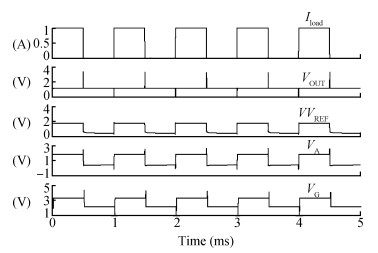

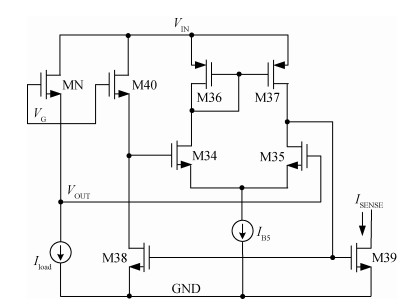

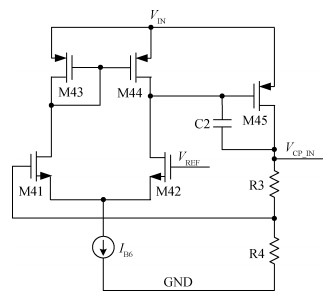

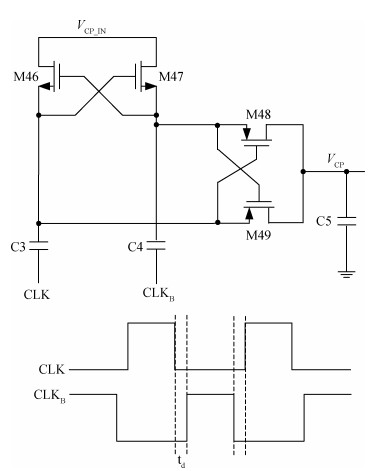

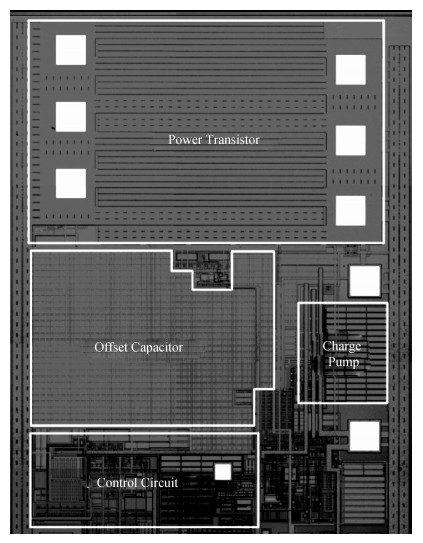

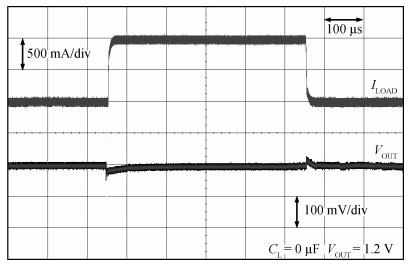

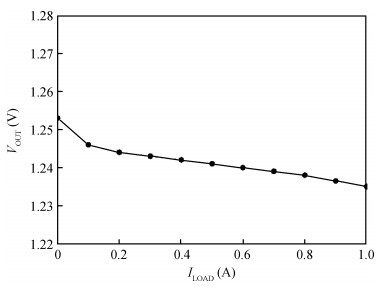

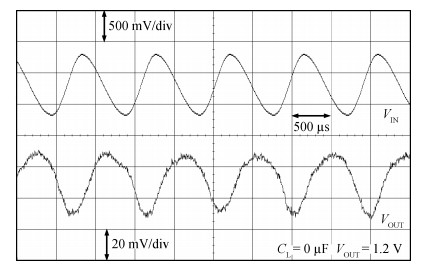

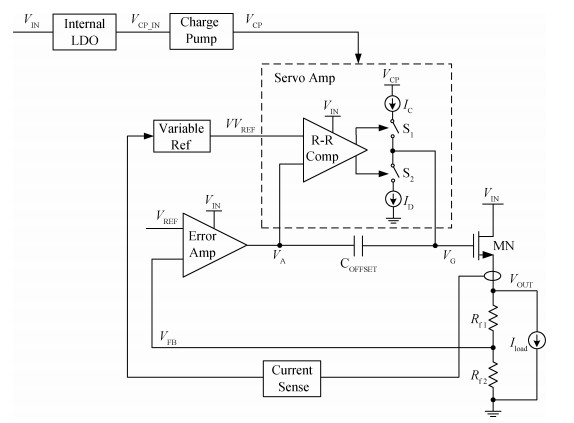

This paper presents a fully on-chip NMOS low-dropout regulator (LDO) for portable applications with quasi floating gate pass element and fast transient response. The quasi floating gate structure makes the gate of the NMOS transistor only periodically charged or refreshed by the charge pump, which allows the charge pump to be a small economical circuit with small silicon area. In addition, a variable reference circuit is introduced enlarging the dynamic range of error amplifier during load transient. The proposed LDO has been implemented in a 0.35 μm BCD process. From experimental results, the regulator can operate with a minimum dropout voltage of 250 mV at a maximum 1 A load and IQ of 395 μA. Under full-range load current step, the voltage undershoot and overshoot of the proposed LDO are reduced to 50 and 26 mV, respectively. -

References

[1] Guo J P, Leung K N. A 6-μW chip-area-efficient output-capacitorless LDO in 90-nm CMOS technology. IEEE J Solid-State Circuits, 2010, 45(9): 1896 http://amsc.tamu.edu/news/Top_JSSC_Feb_10.mht[2] Ma H F, Zhou F. Full on-chip and area-efficient CMOS LDO with zero to maximum load stability using adaptive frequency compensation. J Semicond, 2010, 31(1): 015006 http://www.oalib.com/paper/1522279[3] Gao L S, Zhou Y M, Wu B. A full on-chip CMOS low-dropout voltage regulator with VCCS compensation. J Semicond, 2010, 31(8): 085006 doi: 10.1088/1674-4926/31/8/085006[4] Zhou Q N, Wang Y S, Lai F C. A capacitor-free CMOS LDO regulator with AC-boosting and active-feedback frequency compensation. J Semicond, 2009, 30(4): 45006 doi: 10.1088/1674-4926/30/4/045006[5] Han P, Wang Z G, Xu Y. A capacitor-free CMOS low-dropout regulator for system-on-chip application. J Semicond, 2008, 29(8): 1507 http://en.cnki.com.cn/Article_en/CJFDTOTAL-BDTX200808018.htm[6] Chong S S, Chan P K. A 0.9-μA quiescent current output-capacitorless LDO regulator with adaptive power transistors in 65-nm CMOS. IEEE Trans Circuits Syst I, 2013, 60(4): 1072[7] Kim Y I, Lee S S. A capacitorless LDO regulator with fast feedback technique and low-quiescent current error amplifier. IEEE Trans Circuits Syst Ⅱ, 2013, 60(6): 326 doi: 10.1109/TCSII.2013.2258250[8] Zhan C C, Ki W H. An output-capacitor-free adaptively biased low-dropout regulator with subthreshold under shoot-reduction for SoC. IEEE Trans Circuits Syst I, 2012, 59(5): 1119[9] Ming X, Li A, Zhou Z K, et al. An ultrafast adaptively biased capacitorless LDO with dynamic charging control. IEEE Trans Circuits Syst Ⅱ, 2012, 59(1): 40 https://www.infona.pl/resource/bwmeta1.element.ieee-art-000006112675[10] Qu X, Zhou Z K, Zhang B, et al. An ultralow-power fast-transient capacitor-free low-dropout regulator with assistant push-pull output stage. IEEE Trans Circuits Syst Ⅱ, 2013, 60(2): 96 https://www.researchgate.net/publication/260667054_An_Ultralow-Power_Fast-Transient_Capacitor-Free_Low-Dropout_Regulator_With_Assistant_Push-Pull_Output_Stage[11] Man T Y, Leung K N, Leung C Y. Development of single-transistor-control LDO based on flipped voltage follower for SoC. IEEE Trans Circuits Syst I, 2008, 55(5): 1392 https://www.researchgate.net/publication/3451873_Development_of_Single-Transistor-Control_LDO_Based_on_Flipped_Voltage_Follower_for_SoC[12] Or P Y, Leung K N. An output-capacitorless low-dropout regulator with direct voltage-spike detection. IEEE J Solid-State Circuits, 2010, 45(2): 458 http://www.wenkuxiazai.com/doc/026bc8ea4a7302768f993986.html[13] Rincon-Mora G A. Analog IC design with low-dropout regulators. New York: The McGraw-Hill Companies, 2009[14] Wang H, Tan L. A transient-enhanced NMOS low dropout voltage regulator with parallel feedback compensation. J Semicond, 2016, 37(2): 025005 http://industry.wanfangdata.com.cn/yj/Detail/Periodical?id=Periodical_bdtxb201602024[15] Camacho D, Gui P, Moreira P. Fully on-chip switched capacitor NMOS low dropout voltage regulator. Analog Integrated Circuits and Signal Processing, 2010, 65: 141 doi: 10.1007/s10470-009-9439-y[16] Giustolisi G, Falconi C, D'Amico A. On-chip low drop-out voltage regulator with NMOS power transistor and dynamic biasing technique. Analog Integrated Circuits and Signal Processing, 2009, 58: 81 doi: 10.1007/s10470-008-9234-1[17] Nagaraj K. Constant transconductance CMOS amplifier input stage with rail-to-rail input common mode voltage range. IEEE Trans Circuits Syst Ⅱ, 1995, 42(5): 366 http://www.ipcsit.com/vol11/8-ICNEE2011-N016.pdf[18] Wu W C S, Helms W J, Kuhn J A. digital-compatible high-performance operational amplifier with rail-to-rail input and output ranges. IEEE J Solid-State Circuits, 1994, 29(1): 63 https://www.researchgate.net/publication/226163012_Rail-to-rail_input_and_output_amplifiers[19] Nakagome Y, Tanaka H, Takeuchi K. An experimental 1.5 V 64 Mb DRAM. IEEE J Solid-State Circuits, 1991, 26(4): 465 doi: 10.1109/4.75040[20] Favrat P, Deval P, Declercq M J. A high-efficiency CMOS voltage doubler. IEEE J Solid-State Circuits, 1998, 33(3): 410 https://www.researchgate.net/publication/3701440_A_new_high_efficiency_CMOS_voltage_doubler -

Proportional views

DownLoad:

DownLoad: