| Citation: |

Shaoming Lin, Shaoying Ke, Yujie Ye, Donglin Huang, Jinyong Wu, Songyan Chen, Cheng Li, Jianyuan Wang, Wei Huang. Electrical properties of Si/Si bonded wafers based on an amorphous Ge interlayer[J]. Journal of Semiconductors, 2018, 39(11): 113001. doi: 10.1088/1674-4926/39/11/113001

****

S M Lin, S Y Ke, Y J Ye, D L Huang, J Y Wu, S Y Chen, C Li, J Y Wang, W Huang, Electrical properties of Si/Si bonded wafers based on an amorphous Ge interlayer[J]. J. Semicond., 2018, 39(11): 113001. doi: 10.1088/1674-4926/39/11/113001.

|

Electrical properties of Si/Si bonded wafers based on an amorphous Ge interlayer

DOI: 10.1088/1674-4926/39/11/113001

More Information

-

Abstract

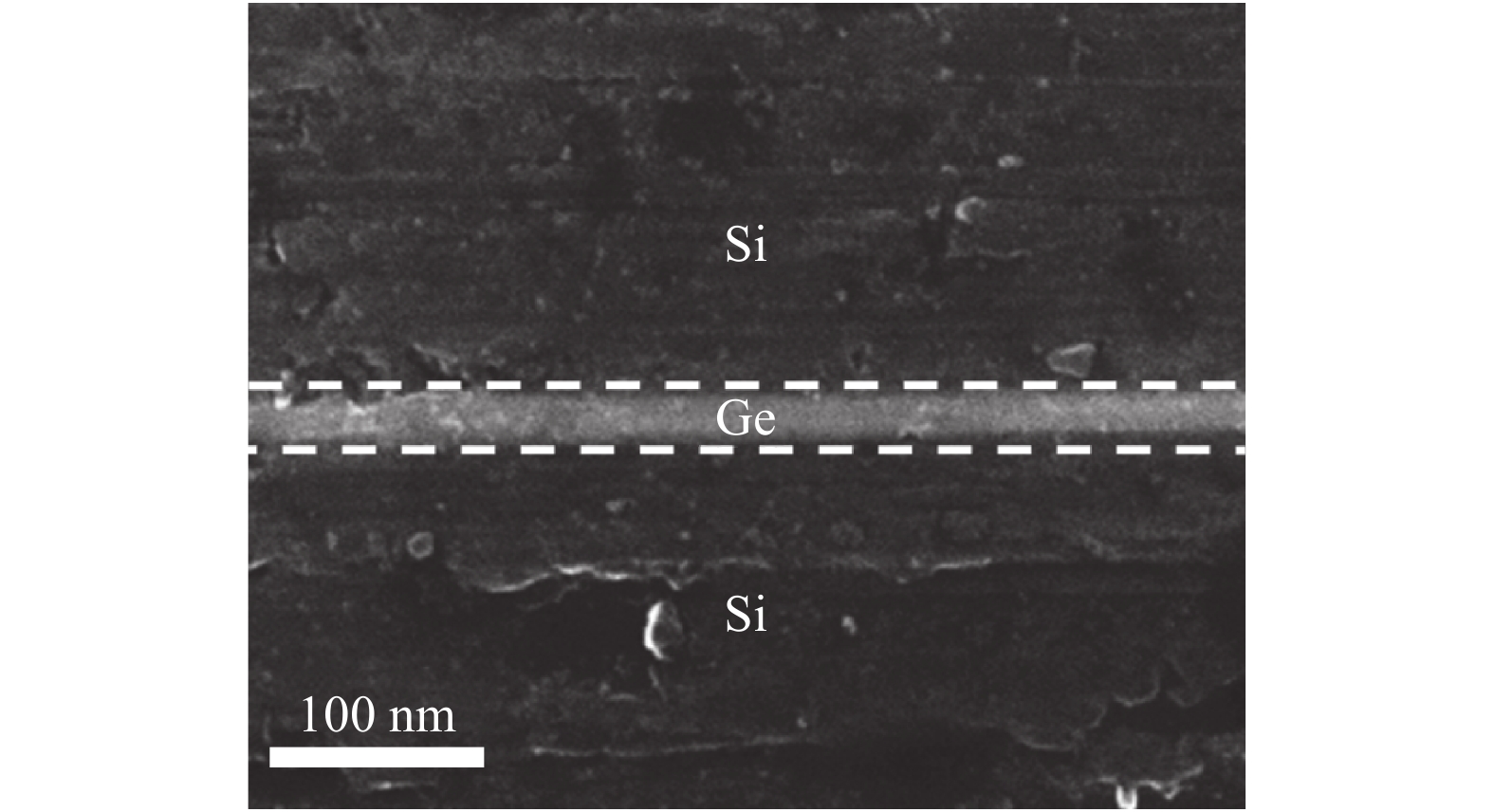

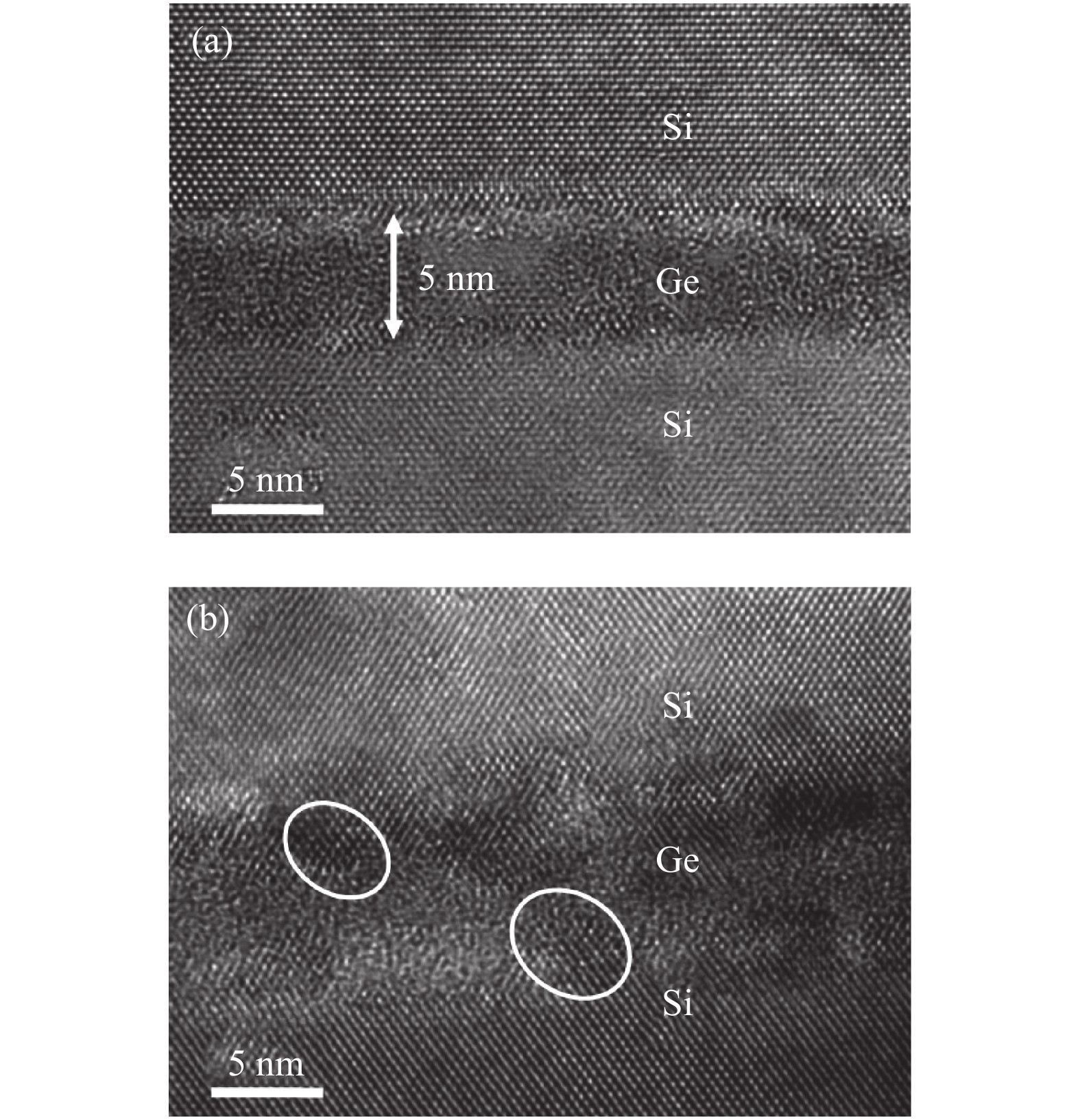

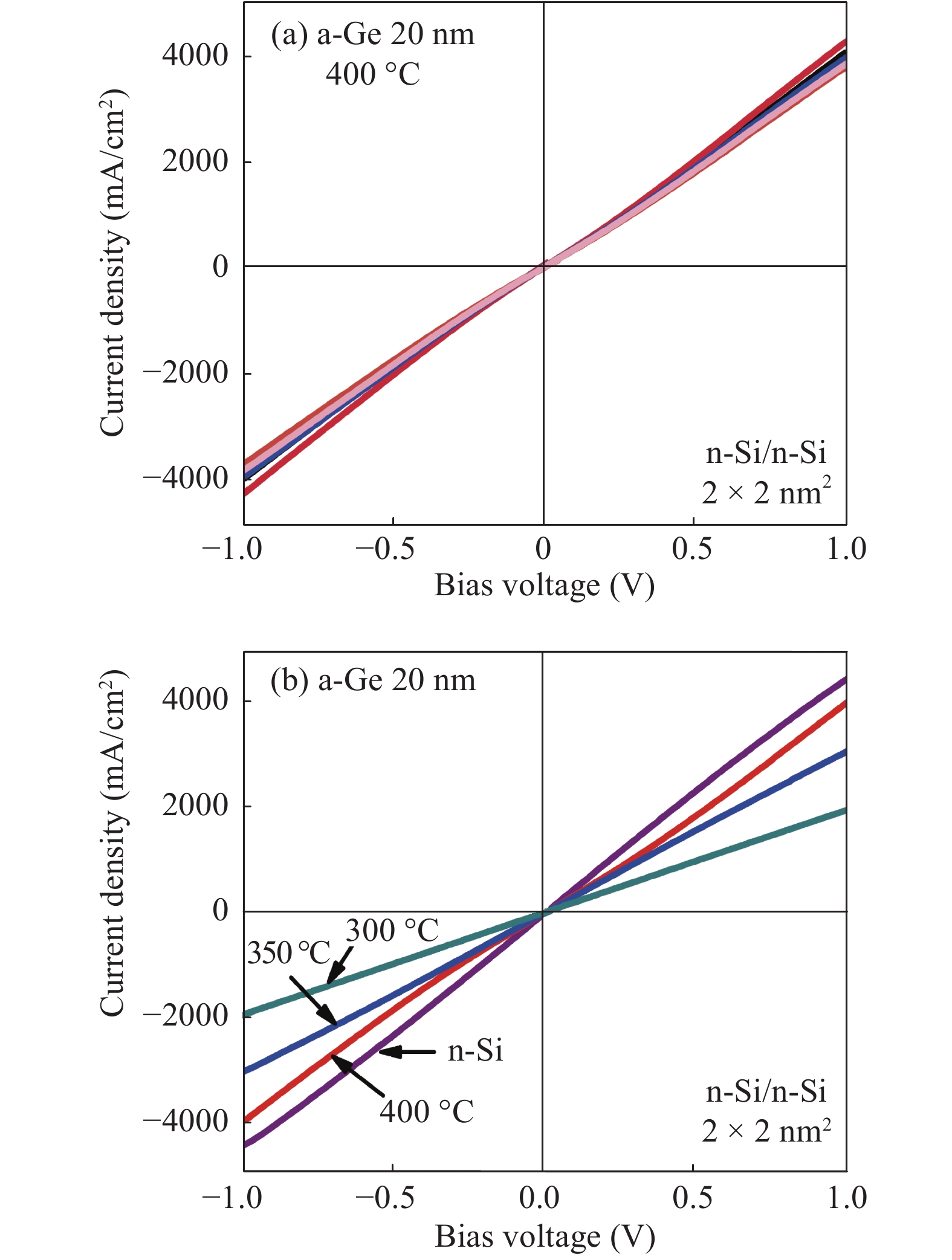

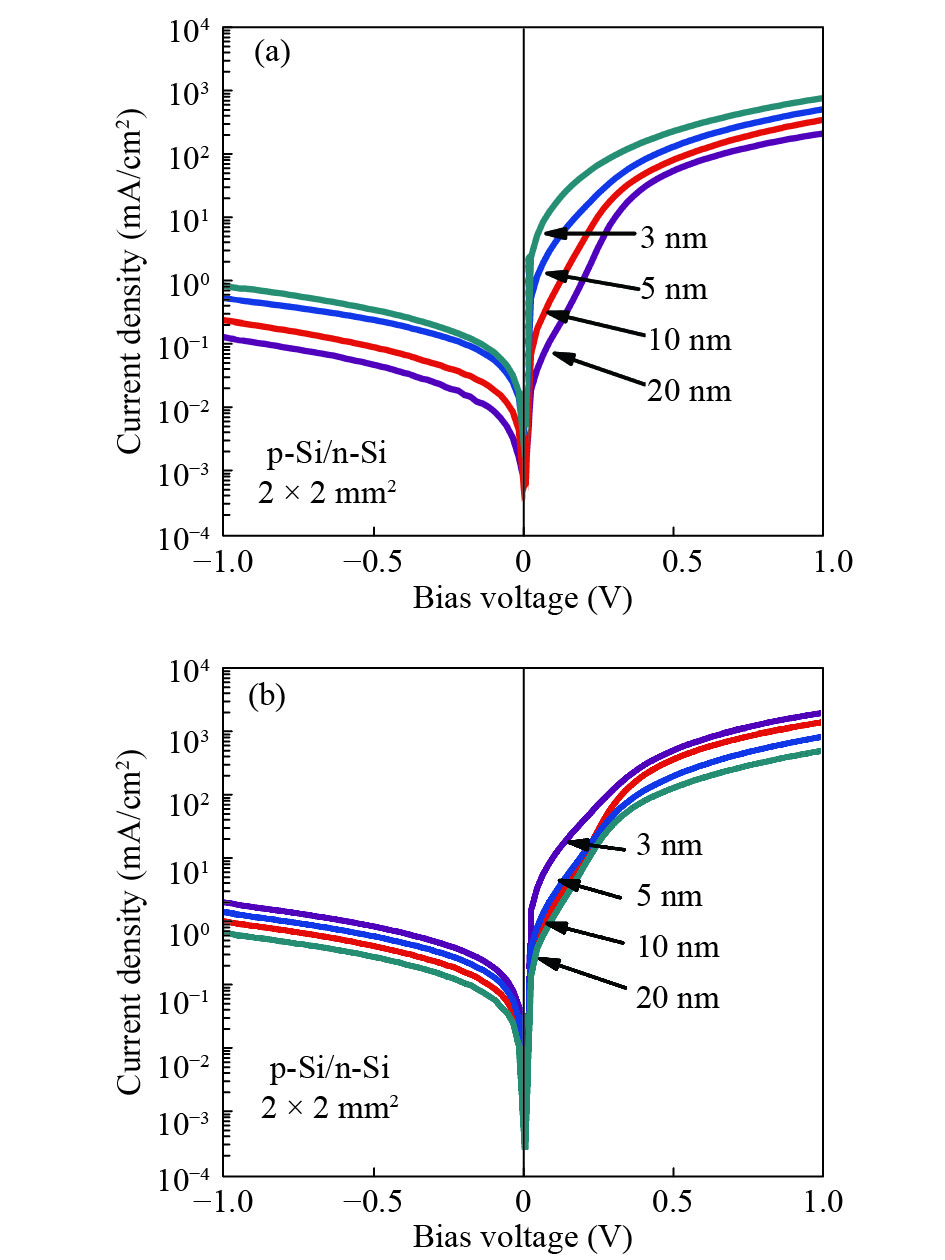

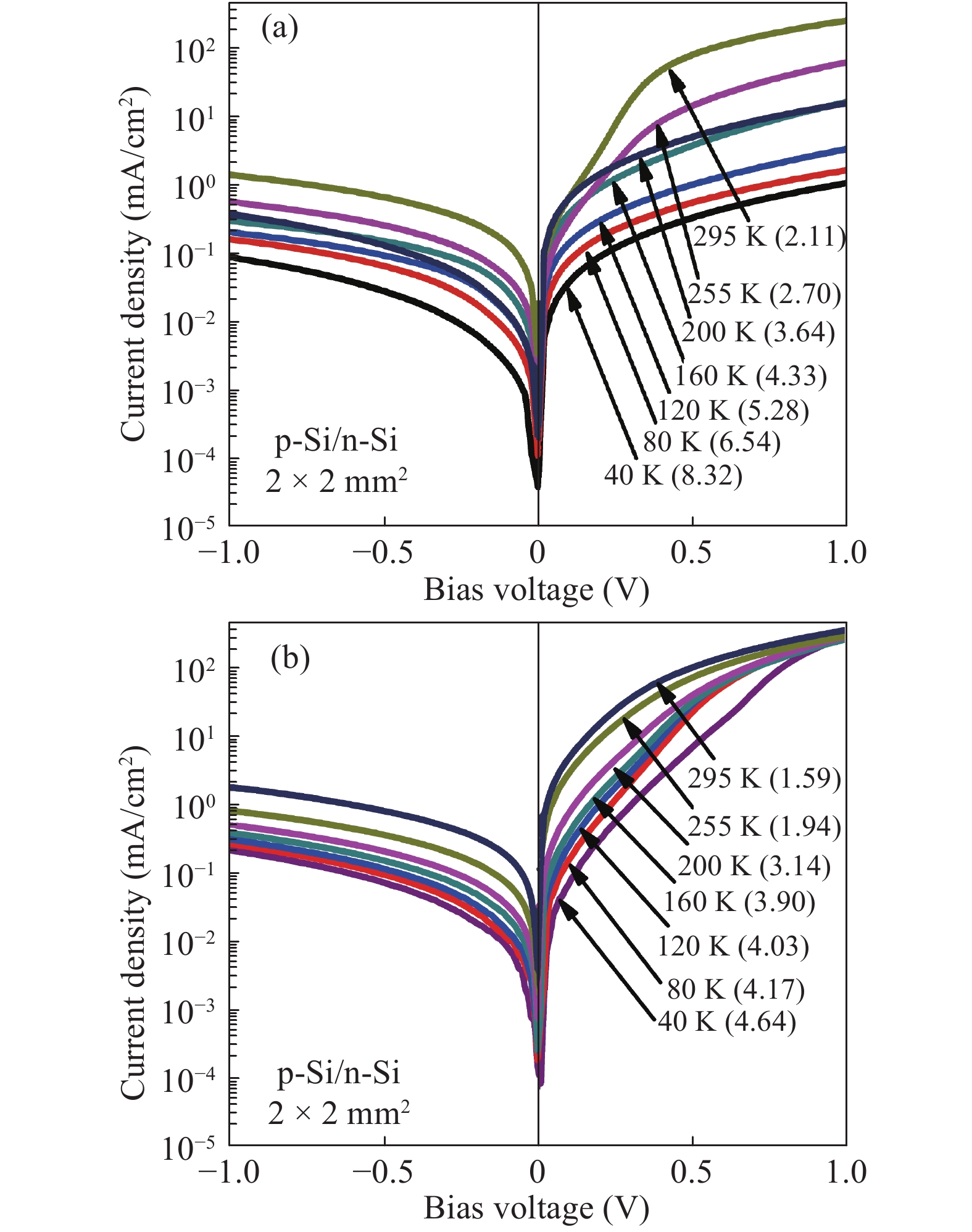

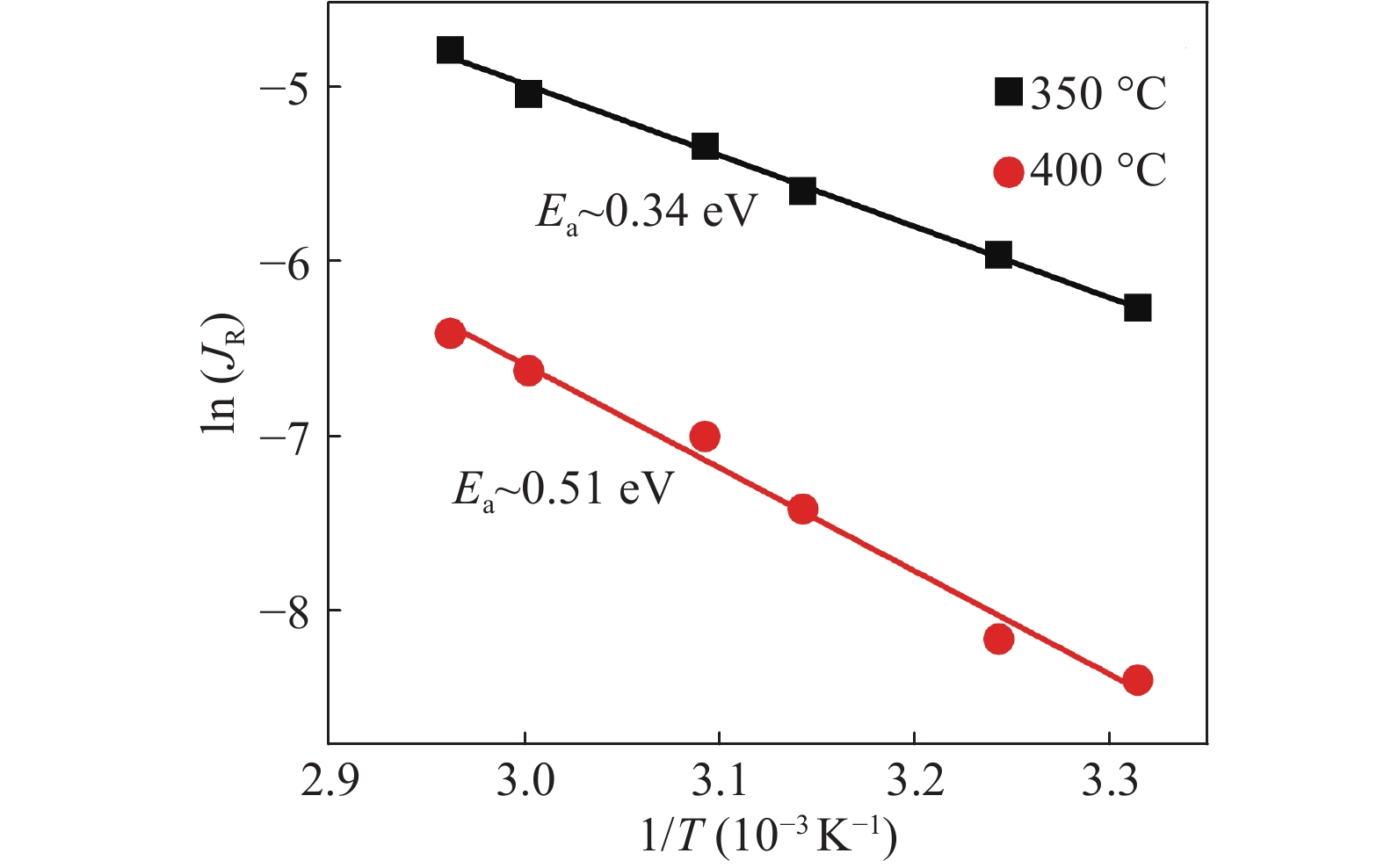

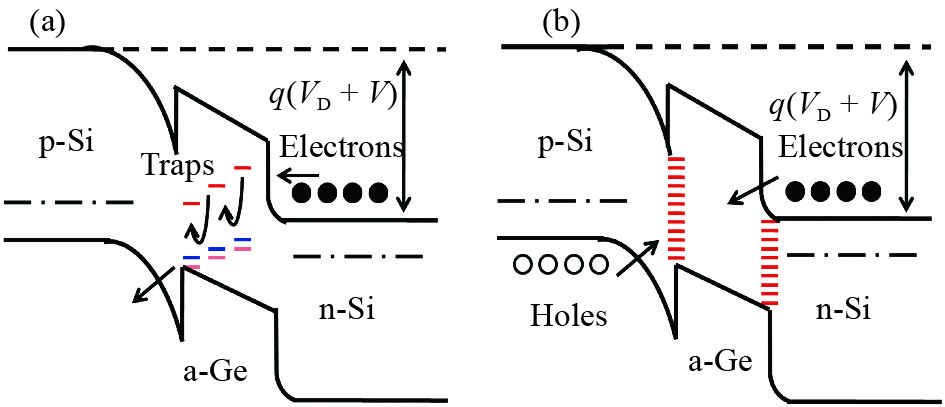

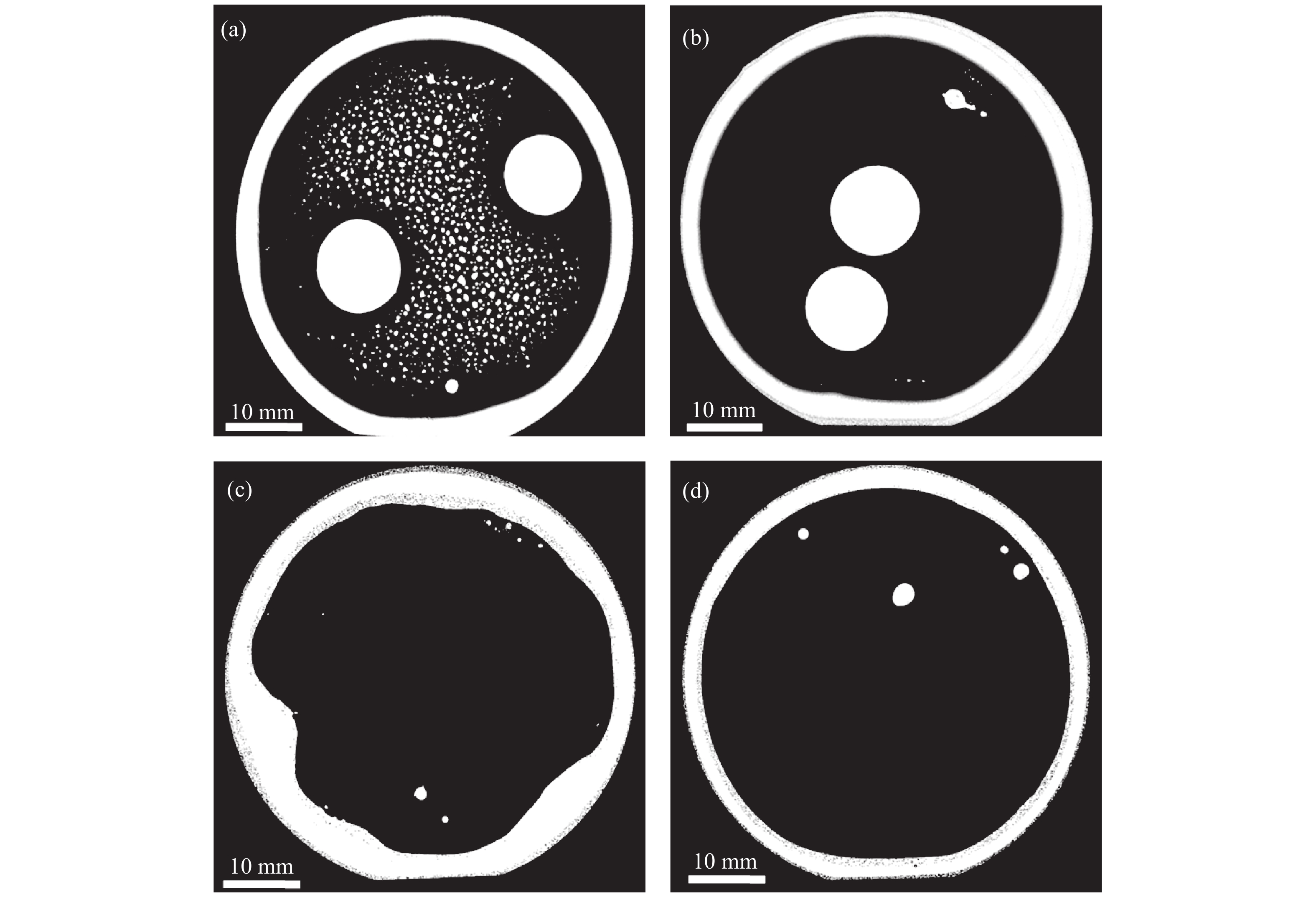

An amorphous Ge (a-Ge) intermediate layer is introduced into the Si bonded interface to lower the annealing temperature and achieve good electrical characteristics. The interface and electrical characteristics of n-Si/n-Si and p-Si/n-Si junctions manufactured by low-temperature wafer bonding based on a thin amorphous Ge are investigated. It is found that the bubble density tremendously decreases when the a-Ge film is not immersed in DI water. This is due to the decrease of the –OH groups. In addition, when the samples are annealed at 400 °C for 20 h, the bubbles totally disappear. This can be explained by the appearance of the polycrystalline Ge (absorption of H2) at the bonded interface. The junction resistance of the n-Si/n-Si bonded wafers decreases with the increase of the annealing temperature. This is consistent with the recrystallization of the a-Ge when high-temperature annealing is conducted. The carrier transport of the Si-based PN junction annealed at 350 °C is consistent with the trap-assisted tunneling model and that annealed at 400 °C is related to the carrier recombination model. -

References

[1] Iyer S S, Auberton-Herve A J. Silicon wafer bonding technology for VLSI and MEMS applications: INSPEC. The Institute of Electrical Engineers, London, United Kingdom, 2002[2] Miki N, Zhang X, Khanna R, et al. Multi-stack silicon-direct wafer bonding for 3D MEMS manufacturing. Sens Actuators A, 2003, 103(1/2): 194[3] Gity F, Yeol Byun K, Lee K H, et al. Characterization of germanium/silicon p-n junction fabricated by low temperature direct wafer bonding and layer exfoliation. Appl Phys Lett, 2012, 100(9): 092102 doi: 10.1063/1.3688174[4] Tseng C K, Chen W T, Chen K H, et al. A self-assembled microbonded germanium/silicon heterojunction photodiode for 25 Gb/s high-speed optical interconnects. Sci Rep, 2013, 3: 3225 doi: 10.1038/srep03225[5] Maszara W P. Silicon-on-insulator by wafer bonding: a review. J Electrochem Soc, 1991, 138(1): 341 doi: 10.1149/1.2085575[6] Lasky J B. Wafer bonding for silicon-on-insulator technologies. Appl Phys Lett, 1986, 48(1): 78 doi: 10.1063/1.96768[7] Hayashi S, Goorsky M, Noori A, et al. materials issues for the heterogeneous integration of III–V compounds exfoliation and layer transfer. J Electrocheml Soc, 2006, 153(12): G1011 doi: 10.1149/1.2353607[8] Howlader M M R, Kagami G, Lee S H, et al. Sequential plasma-activated bonding mechanism of silicon/silicon wafers. J Microelectromechan Syst, 2010, 19(4): 840 doi: 10.1109/JMEMS.2010.2049731[9] Miao G J, Zhang Z H, Ren T L, et al. Electrical properties measurement for interface research in silicon bonding. ECS Trans, 2010, 25(33): 203[10] Liang J, Chai L, Nishida S, et al. Investigation on the interface resistance of Si/GaAs heterojunctions fabricated by surface-activated bonding. Jpn J Appl Phys, 2015, 54(3): 030211 doi: 10.7567/JJAP.54.030211[11] Yablonovitch E, Allara D L, Chang C C, et al. Unusually low surface-recombination velocity on silicon and germanium surfaces. Phys Rev Lett, 1986, 57(2): 249 doi: 10.1103/PhysRevLett.57.249[12] Howlader M M R, Zhang F. Void-free strong bonding of surface activated silicon wafers from room temperature to annealing at 600 °C. Thin Solid Films, 2010, 519(2): 804 doi: 10.1016/j.tsf.2010.08.144[13] Bengtsson S, Engström O. Interface charge control of directly bonded silicon structures. J Appl Phys, 1989, 66(3): 1231 doi: 10.1063/1.343469[14] Esser R H, Hobart K D, Kub F J. Direct wafer bonded abrupt junction tunnel diodes. J Electrochem Soc, 2004, 151(6): G387 doi: 10.1149/1.1731558[15] Esser R H, Hobart K D, Kub F J. Rapid thermal processing of wafer bonded abrupt junction tunnel diodes. New Jersey: Electrochemical Society, 2003[16] Ke S, Lin S, Ye Y, et al. Bubble evolution mechanism and stress-induced crystallization in low-temperature silicon wafer bonding based on a thin intermediate amorphous Ge layer. J Phys D, 2017, 50(40): 405305 doi: 10.1088/1361-6463/aa81ee[17] Ke S, Ye Y, Lin S, et al. Low-temperature oxide-free silicon and germanium wafer bonding based on a sputtered amorphous Ge. Appl Phys Lett, 2018, 112(4): 041601 doi: 10.1063/1.4996800[18] Hekmatshoar B, Shahrjerdi D, Mohajerzadeh S, et al. Low temperature crystallization of germanium on plastic by externally applied compressive stress. J Vac Sci Technol A, 2003, 21(3): 752 doi: 10.1116/1.1569923[19] Morimoto M, Liang J, Nishida S, et al. Effects of annealing on electrical properties of Si/Si junctions by surface-activated bonding. Jpn J Appl Phys, 2015, 54(3): 030212 doi: 10.7567/JJAP.54.030212[20] Liang J, Miyazaki T, Morimoto M, et al. Electrical properties of Si/Si interfaces by using surface-activated bonding. J Appl Phys, 2013, 114(18): 183703 doi: 10.1063/1.4829676[21] Thareja G, Cheng S L, Kamins T, et al. Electrical characteristics of germanium n+/p junctions obtained using rapid thermal annealing of coimplanted P and Sb. IEEE Electron Device Lett, 2011, 32(5): 608 doi: 10.1109/LED.2011.2119460[22] Tauc J, Grigorovici R, Vancu A. Optical properties and electronic structure of amorphous germanium. Physic Status Solidi B, 1966, 15(2): 627 doi: 10.1002/(ISSN)1521-3951[23] Brodsky M. Amorphous semiconductors. Springer Verlag, 1979[24] Mott N F. Conduction in non-crystalline systems: IV. Anderson localization in a disordered lattice. Philosophical Magazine, 1970, 22(175): 7 doi: 10.1080/14786437008228147 -

Proportional views

DownLoad:

DownLoad: