| Citation: |

Feng Zhang, Ting Zhao, Chunyu Ma, Dongfang Pan. 4-port digital isolator based on on-chip transformer[J]. Journal of Semiconductors, 2018, 39(11): 115003. doi: 10.1088/1674-4926/39/11/115003

****

F Zhang, T Zhao, C Y Ma, D F Pan, 4-port digital isolator based on on-chip transformer[J]. J. Semicond., 2018, 39(11): 115003. doi: 10.1088/1674-4926/39/11/115003.

|

4-port digital isolator based on on-chip transformer

DOI: 10.1088/1674-4926/39/11/115003

More Information

-

Abstract

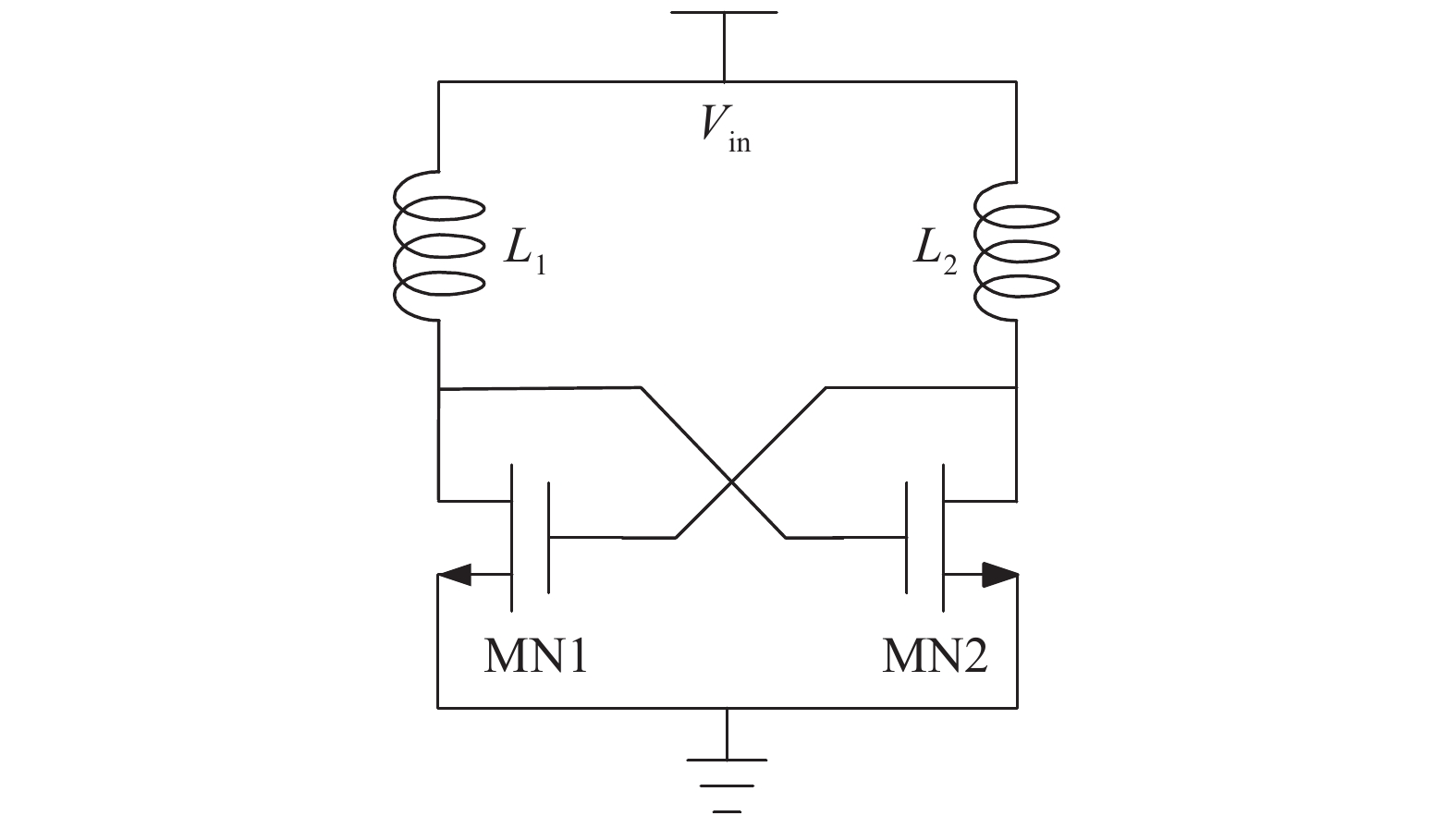

The design and fabrication results of a 4-port digital isolator based on an on-chip transformer for galvanic isolation are presented. An ON–OFF keying modulation scheme is used to transmit the digital signal. The proposed digital isolator is fabricated by the 0.18 μm CMOS process. A test chip can achieve a 1 MHz signal bandwidth, a 40 ns propagation delay, a 35.5 mW input power and a 50 mA drive output current. The proposed digital isolator is pin-compatible, of small volume and low power replacement for the common 4-port optocoupler.-

Keywords:

- optocoupler,

- 4-port,

- digital isolator,

- on-chip transformer

-

References

[1] Kaeriyama S, Uchida S, Furumiya M, et al. A 2.5 kV isolation 35 kV/μs CMR 250 Mbps digital isolator in standard CMOS with a small transformer driving technique. IEEE J Solid-State Circuits, 2012, 47(2): 435 doi: 10.1109/JSSC.2011.2170775[2] Coyne E, Lynch S, McGuinness P, et al. Low gate drive IGBT enabling direct control through digital isolator power. IEEE Symposium on Bipolar/BiCMOS Circuits and Technology Meeting, New Brunswick, NJ, USA, 2016: 134[3] Fandrich C L. An on-chip transformer-based digital isolator system. Master's thesis. The University of Tennessee, Knoxville, USA, 2013[4] Lumio M. Applicability of CMOS digital isolators in variable-frequency drives. Master's Thesis, Aalto University, Finland, 2016[5] Uchida S, Kaeriyama S, Nagase H, et al. A face-to-face chip stacking 7 kV RMS digital isolator for automotive and industrial motor drive applications. IEEE 26th International Symposium on Power Semiconductor Devices & IC's, Waikoloa, Hawaii, 2014: 442[6] Yun R, Sun J, Gaalaas E, et al. A transformer-based digital isolator with 20 kV PK surge capability and > 200 kV/ μS common mode transient immunity. IEEE Symposium on VLSI Circuits, Honolulu, Hawaii, USA, 2016: 1[7] To D N, Rouger N, Lembeye Y, et al. Modeling and characterization of 0.35 μm CMOS coreless transformer for gate drivers. IEEE 26th International Symposium on Power Semiconductor Devices & IC's, Waikoloa, Hawaii, USA, 2014: 330[8] Culurciello E, Pouliquen P O, Andreou A G. Digital isolation amplifier in silicon-on-sapphire CMOS. Electron Lett, 2007, 43(8): 451 doi: 10.1049/el:20070509[9] Moghe Y, Terry A, Luzon D. Monolithic 2.5 kV RMS, 1.8–3.3 V dual-channel 640 Mbps digital isolator in 0.5 μm SOS. IEEE International SOI Conference, Napa, California, USA, 2012: 1[10] Park S, Kim J, Jo S. Modeling of giant magnetoresistance isolator for high speed digital data transmission utilizing spin valves. J Appl Phys, 2005, 97(10): 2773[11] Daliri M, Maymandi-Nejad M. Analytical model for CMOS cross-coupled LC-tank oscillator. IET Circuits, Devices Syst, 2013, 8(1): 1[12] PC817 Series, High density mounting type photocoupler, Data Sheet, SHARP[13] PS2501-1,-2,-4,PS2501l-1,-2,-4, High isolation voltage single transistor type multi photocoupler series, Data Sheet PN10225EJ03V0DS, NEC -

Proportional views

DownLoad:

DownLoad: