| Citation: |

Xin Cheng, Yu Zhang, Guangjun Xie, Yizhong Yang, Zhang Zhang. An ultra-low power output capacitor-less low-dropout regulator with slew-rate-enhanced circuit[J]. Journal of Semiconductors, 2018, 39(3): 035002. doi: 10.1088/1674-4926/39/3/035002

****

X Cheng, Y Zhang, G J Xie, Y Z Yang, Z Zhang. An ultra-low power output capacitor-less low-dropout regulator with slew-rate-enhanced circuit[J]. J. Semicond., 2018, 39(3): 035002. doi: 10.1088/1674-4926/39/3/035002.

|

An ultra-low power output capacitor-less low-dropout regulator with slew-rate-enhanced circuit

DOI: 10.1088/1674-4926/39/3/035002

More Information

-

Abstract

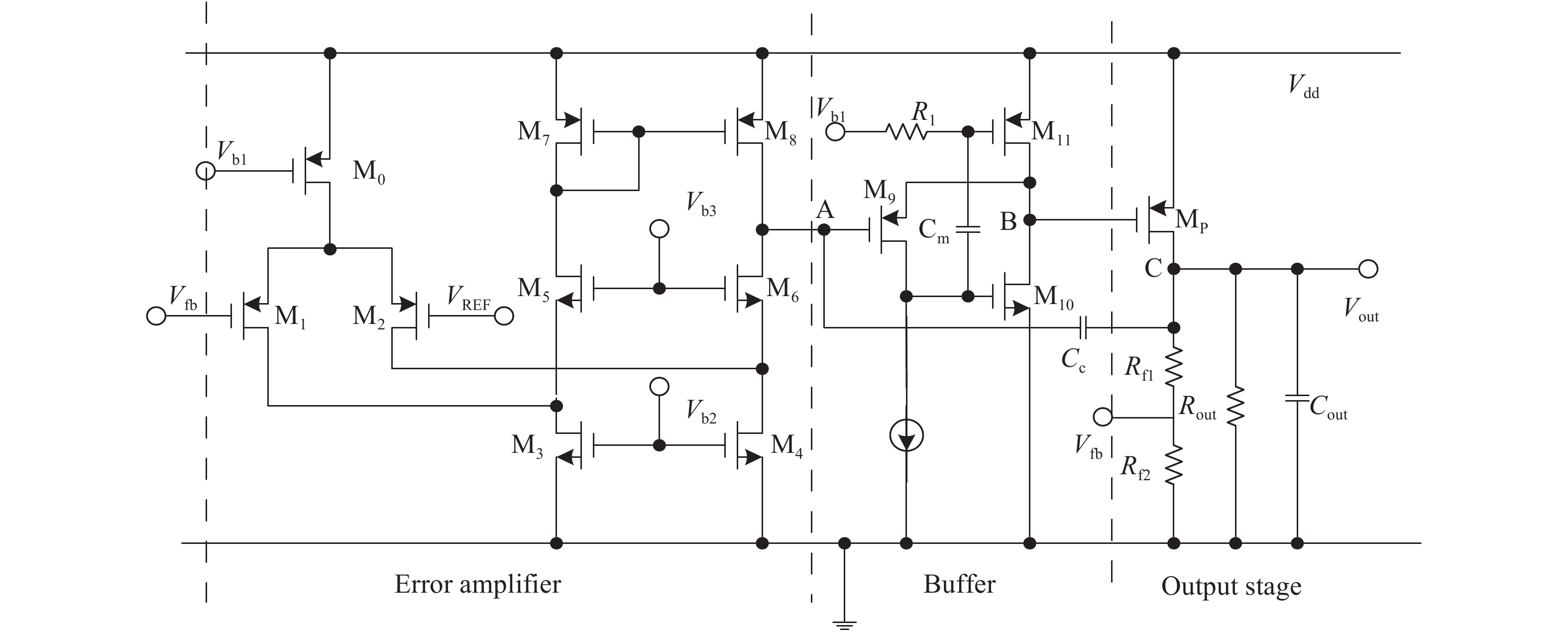

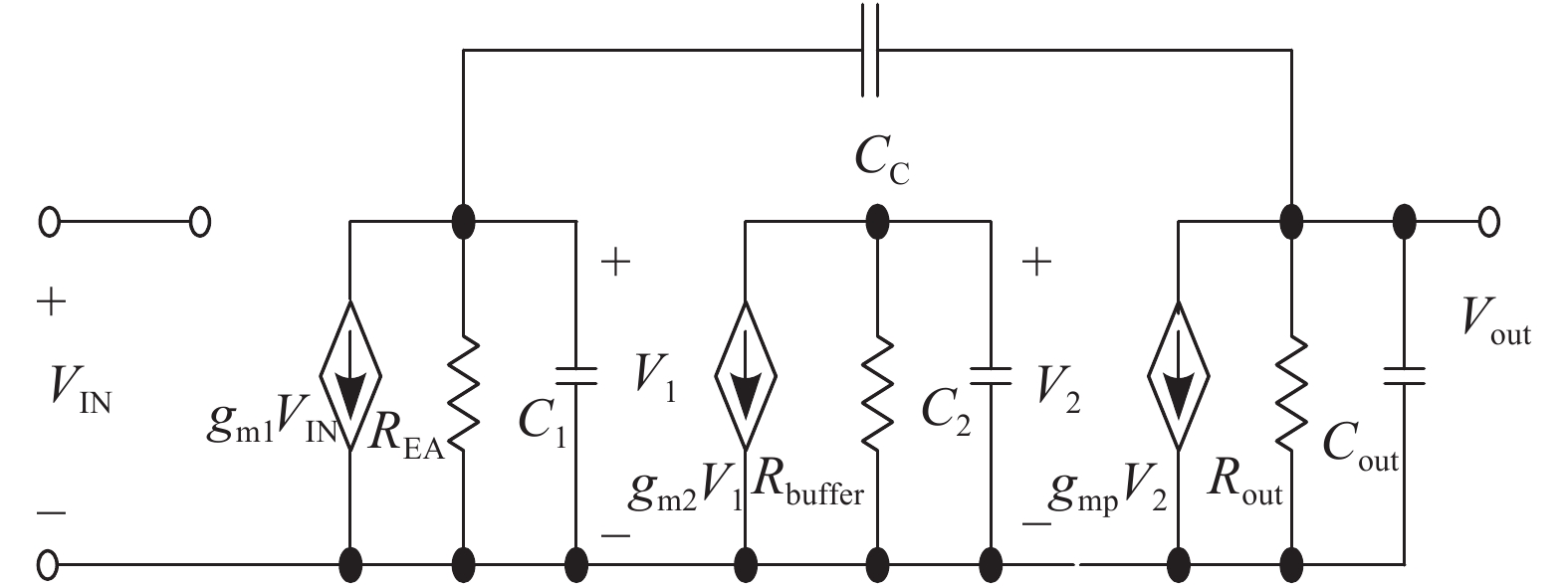

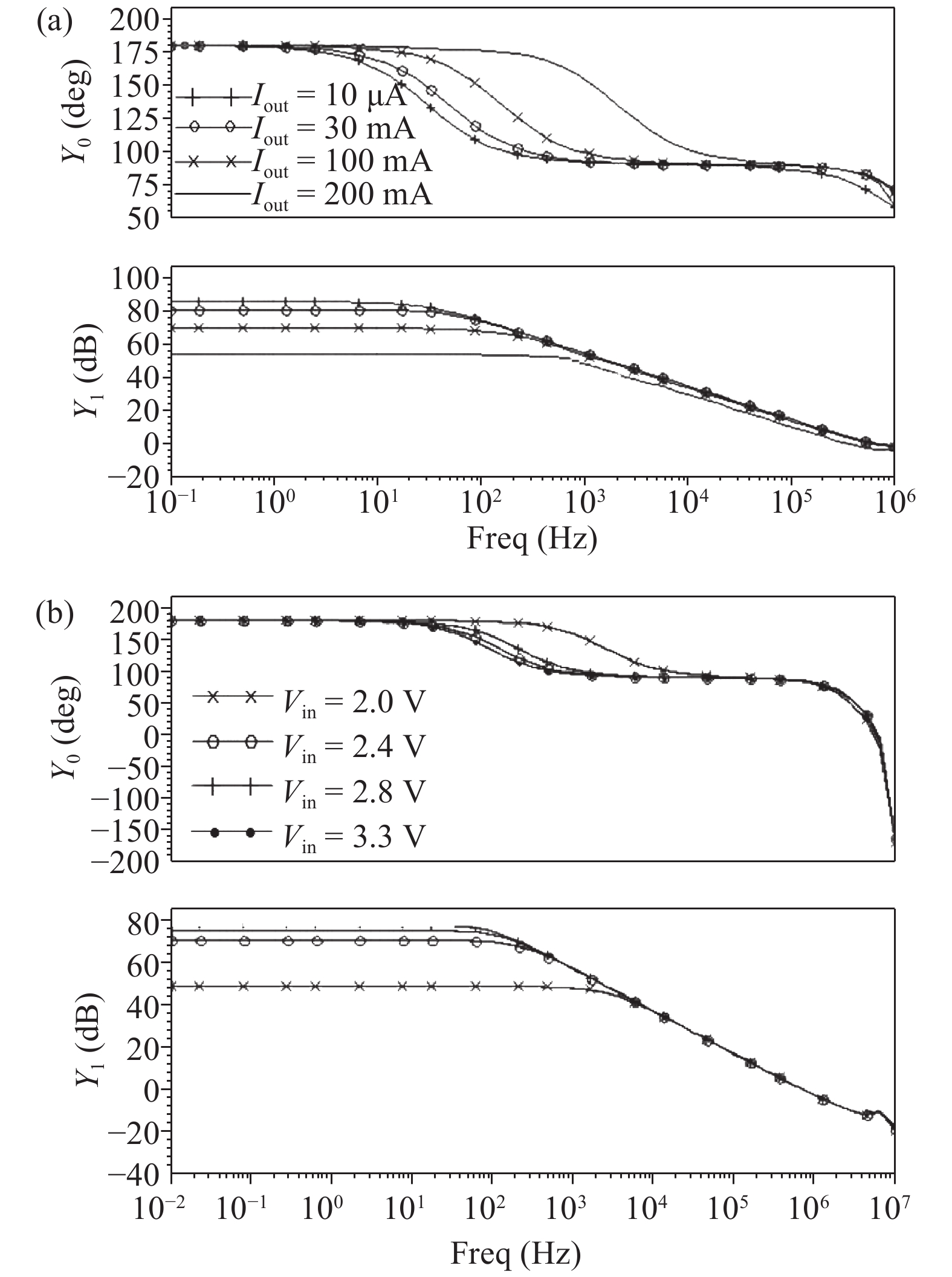

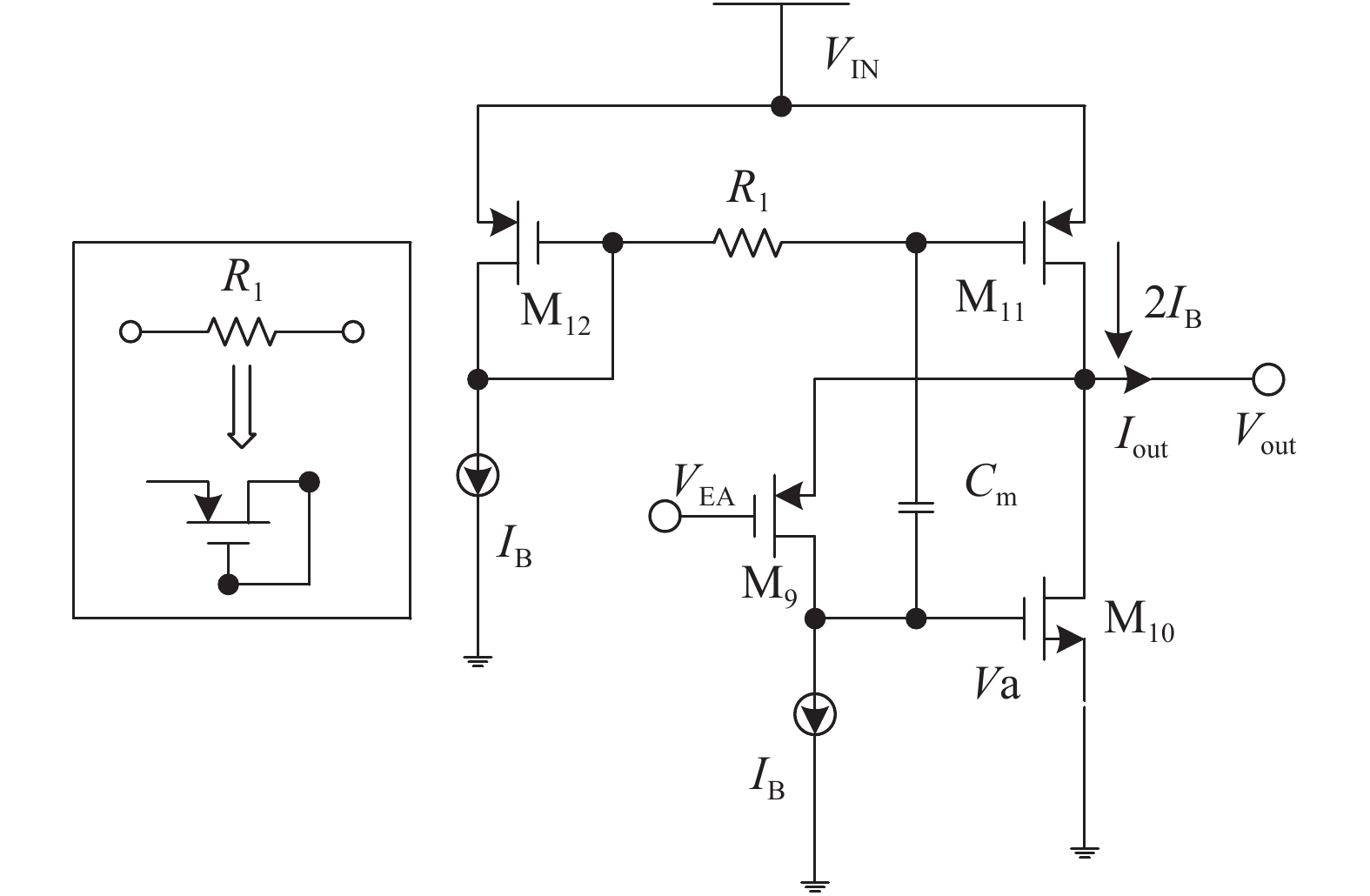

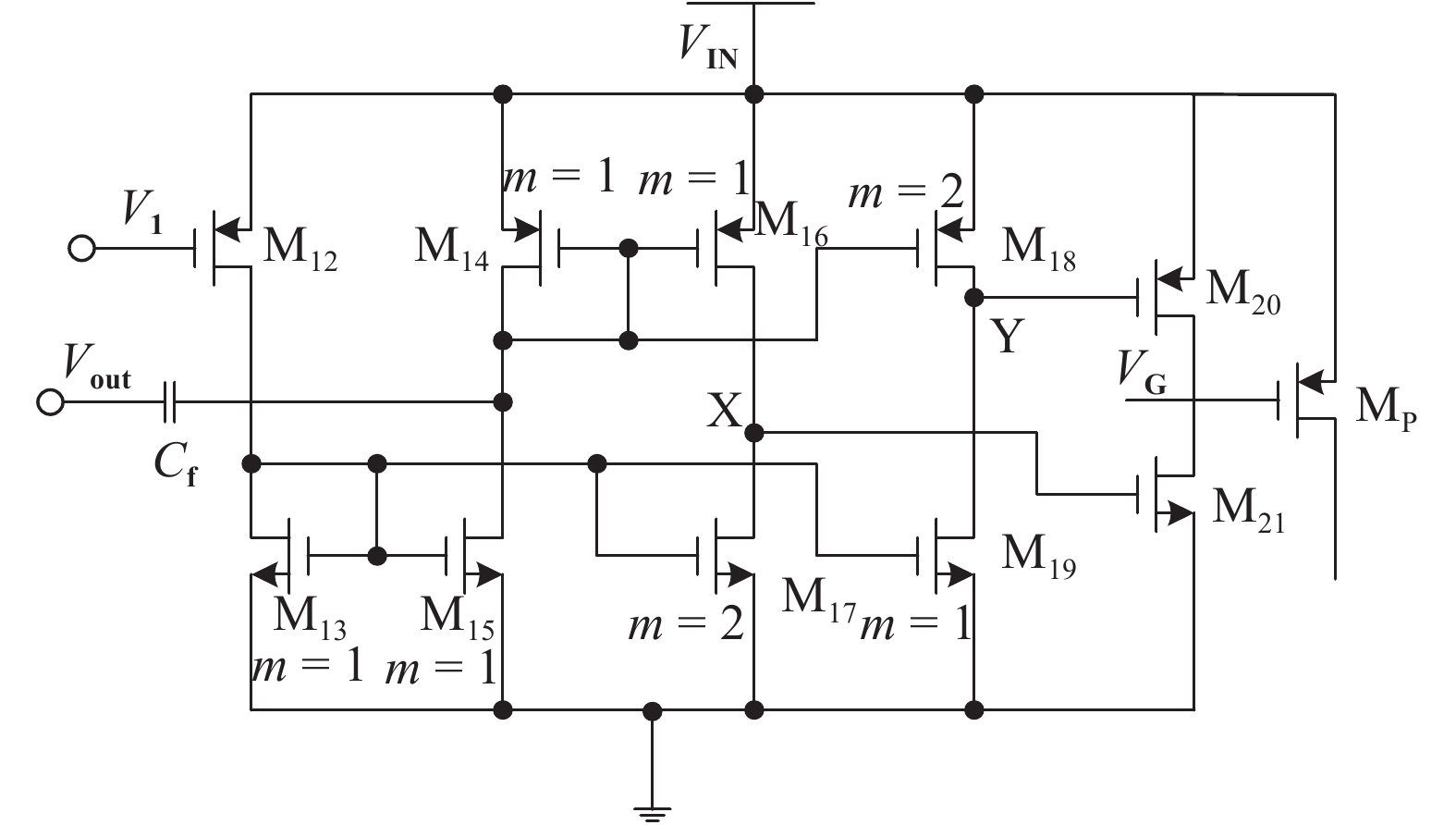

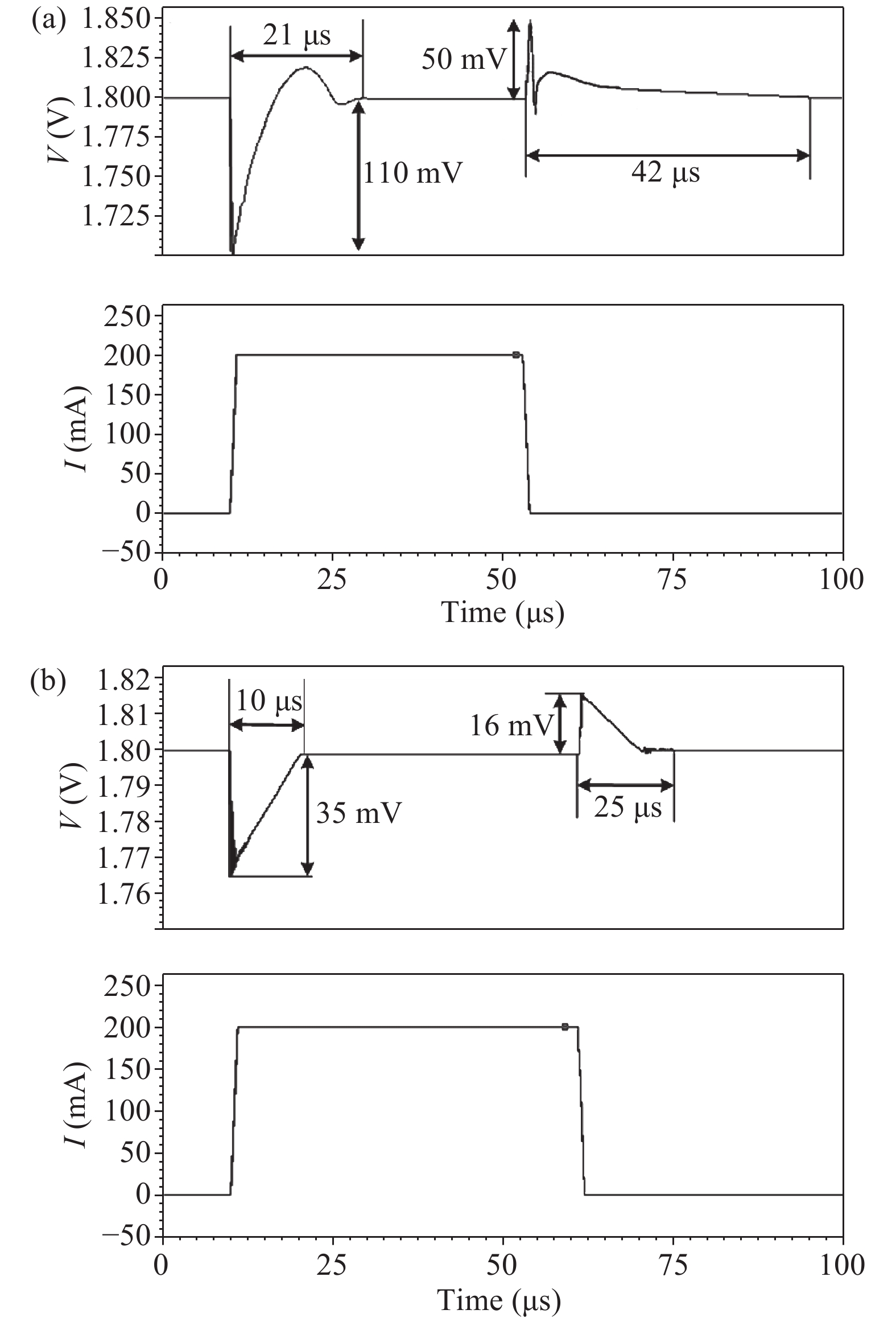

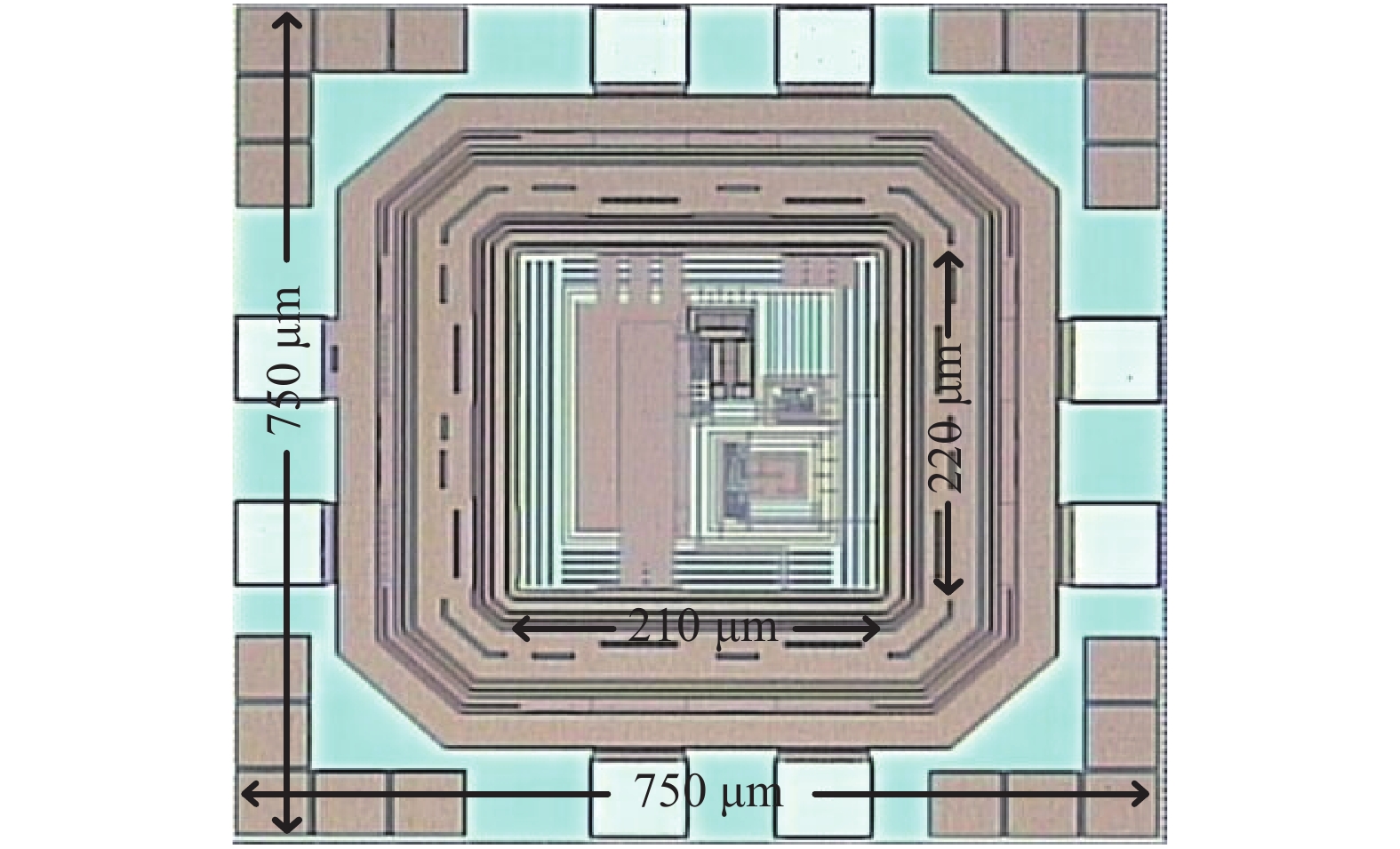

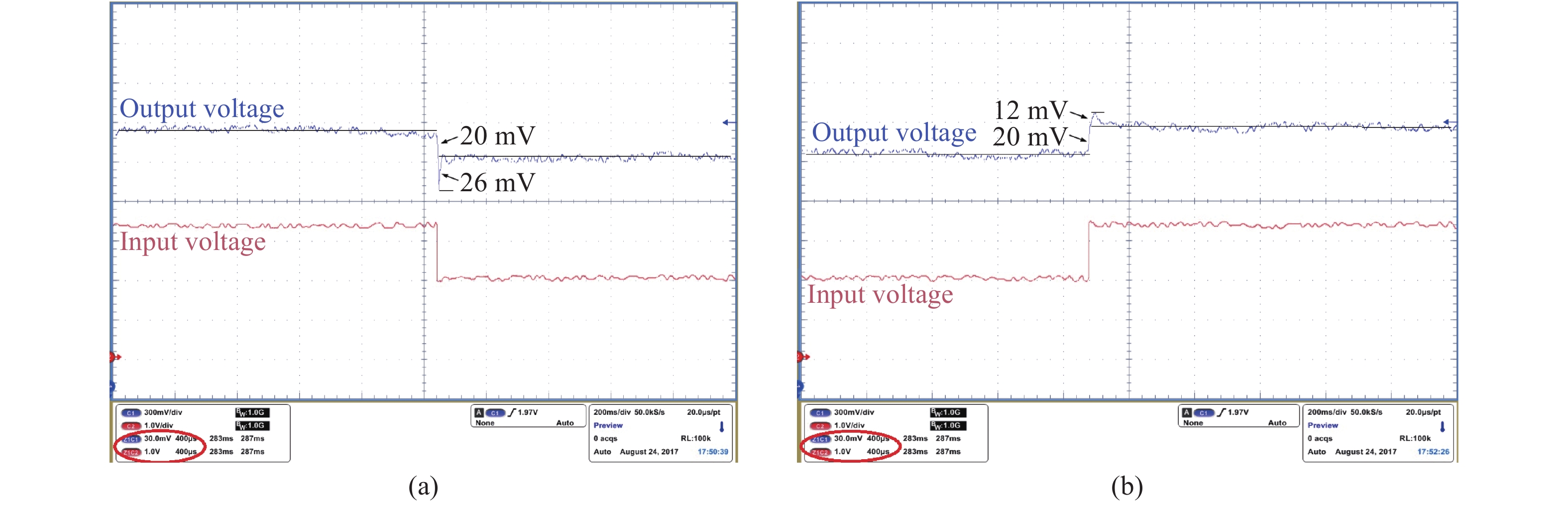

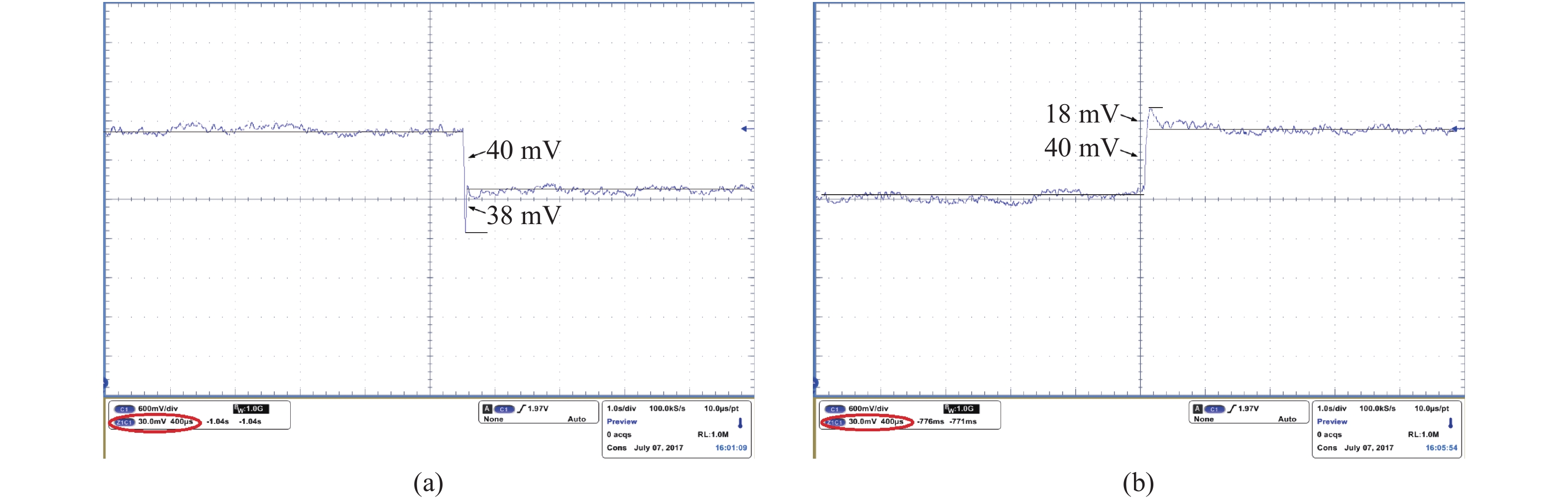

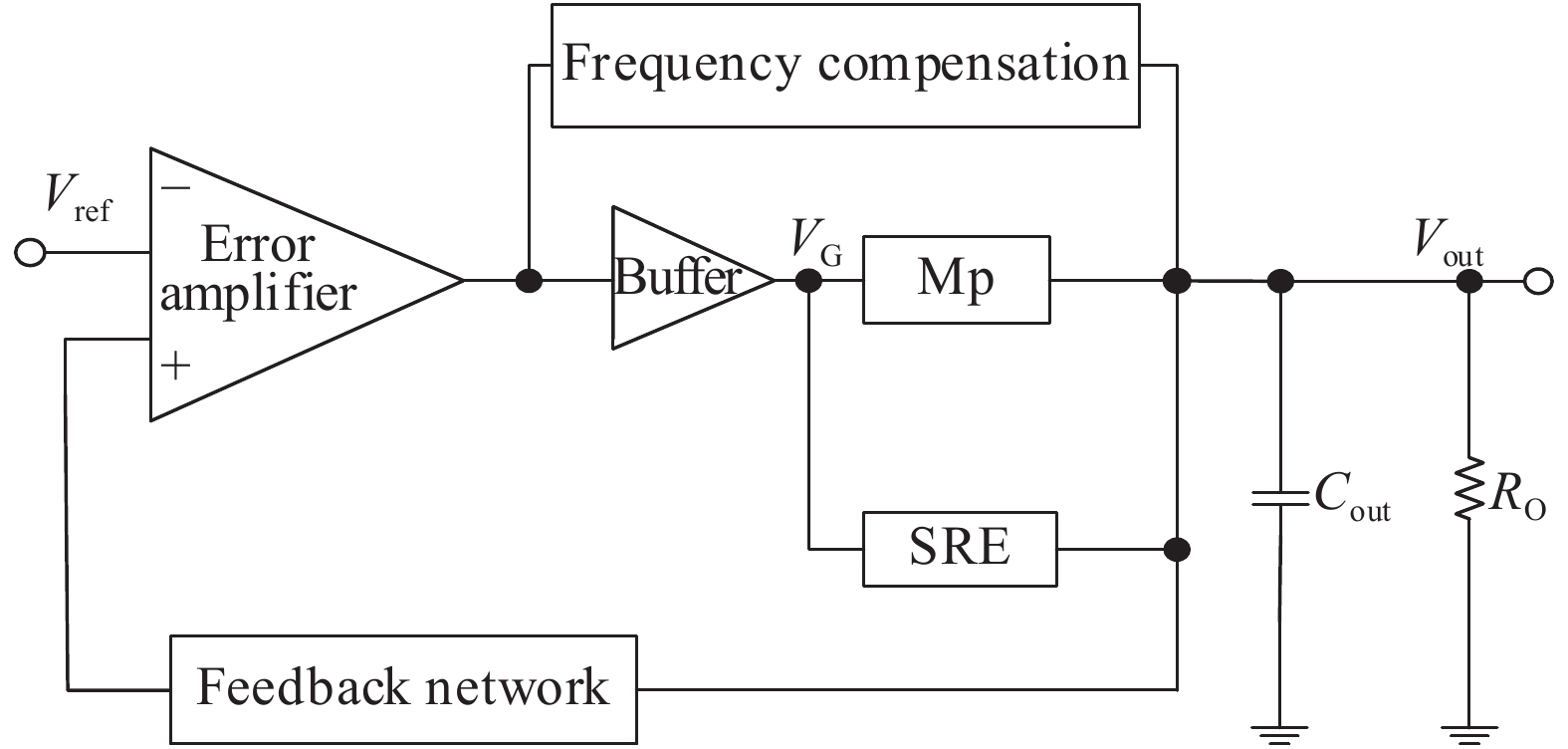

An ultra-low power output-capacitorless low-dropout (LDO) regulator with a slew-rate-enhanced (SRE) circuit is introduced. The increased slew rate is achieved by sensing the transient output voltage of the LDO and then charging (or discharging) the gate capacitor quickly. In addition, a buffer with ultra-low output impedance is presented to improve line and load regulations. This design is fabricated by SMIC 0.18 μm CMOS technology. Experimental results show that, the proposed LDO regulator only consumes an ultra-low quiescent current of 1.2 μA. The output current range is from 10 μA to 200 mA and the corresponding variation of output voltage is less than 40 mV. Moreover, the measured line regulation and load regulation are 15.38 mV/V and 0.4 mV/mA respectively.-

Keywords:

- LDO,

- output capacitorless,

- ultra-low power,

- slew rate

-

References

[1] Ho M, Leung K N, Mak K L. A low-power fast-transient 90-nm low-dropout regulator with multiple small-gain stages. IEEE J Solid-State Circuits, 2010, 45(11): 2466[2] Fan S Q, Xue Z M, Lu H, et al. A novel buck/LDO dual-mode DC-DC converter for efficiency improvement. J Semicond, 2013, 34(10): 105002 doi: 10.1088/1674-4926/34/10/105002[3] Garimella A, Furth P M, Surkanti P R. Current buffer compensation topologies for LDOs with improved transient performance. Anal Integr Circuits Signal Process, 2012, 73(1): 131 doi: 10.1007/s10470-011-9811-6[4] Hwang Y S, Lin M S, Hwang B H. A 0.35 μm CMOS sub-1 V low-quiescent-current low-dropout regulator. Proc Asian Solid-State Circuits Conf, 2008: 153[5] Wang H, Tan L. A transient-enhanced NMOS low dropout voltage regulator with parallel feedback compensation. J Semicond, 2016, 37(2): 025005[6] Ho M, Leung K N. Dynamic bias-current boosting technique for ultra low-power low-dropout regulator in biomedical applications. IEEE Trans Circuits Syst II, 2011, 58(3): 174 doi: 10.1109/TCSII.2011.2110330[7] Duan Z, Hu J G, Ding Y, et al. A novel dual-feed low-dropout regulator. J Semicond, 2015, 36(6): 065003 doi: 10.1088/1674-4926/36/6/065003[8] Man T Y, Leung K N, Leung C Y, et al. Development of single-transistor-control LDO based on flipped voltage follower for SoC. IEEE Trans Circuits Syst I, 2008, 55(5): 1392 doi: 10.1109/TCSI.2008.916568[9] Leung K N, Ng Y S. A CMOS low-dropout regulator with a momentarily current-boosting voltage buffer. IEEE Trans Circuits Syst I, 2010, 57(9): 2312 doi: 10.1109/TCSI.2010.2043171[10] Man T Y, Mok P K T, Chan M. A high slew-rate push-pull output amplifier for low-quiescent current low-dropout regulators with transient response improvement. IEEE Trans Circuits Syst II, 2007, 54(9): 755 doi: 10.1109/TCSII.2007.900347[11] Or P Y, Leung K N. An output-capacitorless low-dropout regulator with direct voltage-spike detection. IEEE J Solid-State Circuits, 2010, 45(2): 458 doi: 10.1109/JSSC.2009.2034805[12] Qu X, Zhou Z K, Zhang B. An ultralow-power fast-transient capacitor-free low-dropout regulator with assistant push-pull output stage. IEEE Trans Circuits Syst II, 2013, 60(2): 96 doi: 10.1109/TCSII.2012.2235732[13] Ming X, Li Q, Zhou Z K. An ultrafast adaptively biased capacitorless LDO with dynamic charging control. IEEE Trans Circuits Syst II, 2012, 59(1): 40 doi: 10.1109/TCSII.2011.2177698[14] Wei H L, Liu Y B, Guo Z J, et al. A micro-power LDO with piecewise voltage foldback current limit protection. J Semicond, 2012, 33(11): 115012 doi: 10.1088/1674-4926/33/11/115012[15] Wang H, Gou C, Luo K. A fully on-chip fast-transient NMOS low dropout voltage regulator with quasi floating gate pass element. J Semicond, 2017, 38(4): 045002 doi: 10.1088/1674-4926/38/4/045002[16] Nguyen L, Le K, Pham-Nguyen L. An ultra-small capacitor-less LDO with controlled-resistance technique and MOSFET-only bandgap. Int Conf Adv Technol Commun, 2016: 372[17] Abiri E, Salehi M R, Mohammadalinejadi S. A low dropout voltage regulator with enhanced transconductance error amplifier and small output voltage variations. Iran Electr Eng Conf, 2013: 1[18] Lopez-Martin A J, Ramırez-Angulo J. Power-efficient class AB CMOS buffer. Electron Lett, 2009, 45(2): 89 doi: 10.1049/el:20092270 -

Proportional views

DownLoad:

DownLoad: