| Citation: |

Fuyou Liao, Hongjuan Wang, Xiaojiao Guo, Zhongxun Guo, Ling Tong, Antoine Riaud, Yaochen Sheng, Lin Chen, Qingqing Sun, Peng Zhou, David Wei Zhang, Yang Chai, Xiangwei Jiang, Yan Liu, Wenzhong Bao. Charge transport and quantum confinement in MoS2 dual-gated transistors[J]. Journal of Semiconductors, 2020, 41(7): 072904. doi: 10.1088/1674-4926/41/7/072904

****

F Y Liao, H J Wang, X J Guo, Z X Guo, L Tong, A Riaud, Y C Sheng, L Chen, Q Q Sun, P Zhou, D W Zhang, Y Chai, X W Jiang, Y Liu, W Z Bao, Charge transport and quantum confinement in MoS2 dual-gated transistors[J]. J. Semicond., 2020, 41(7): 072904. doi: 10.1088/1674-4926/41/7/072904.

|

Charge transport and quantum confinement in MoS2 dual-gated transistors

DOI: 10.1088/1674-4926/41/7/072904

More Information

-

Abstract

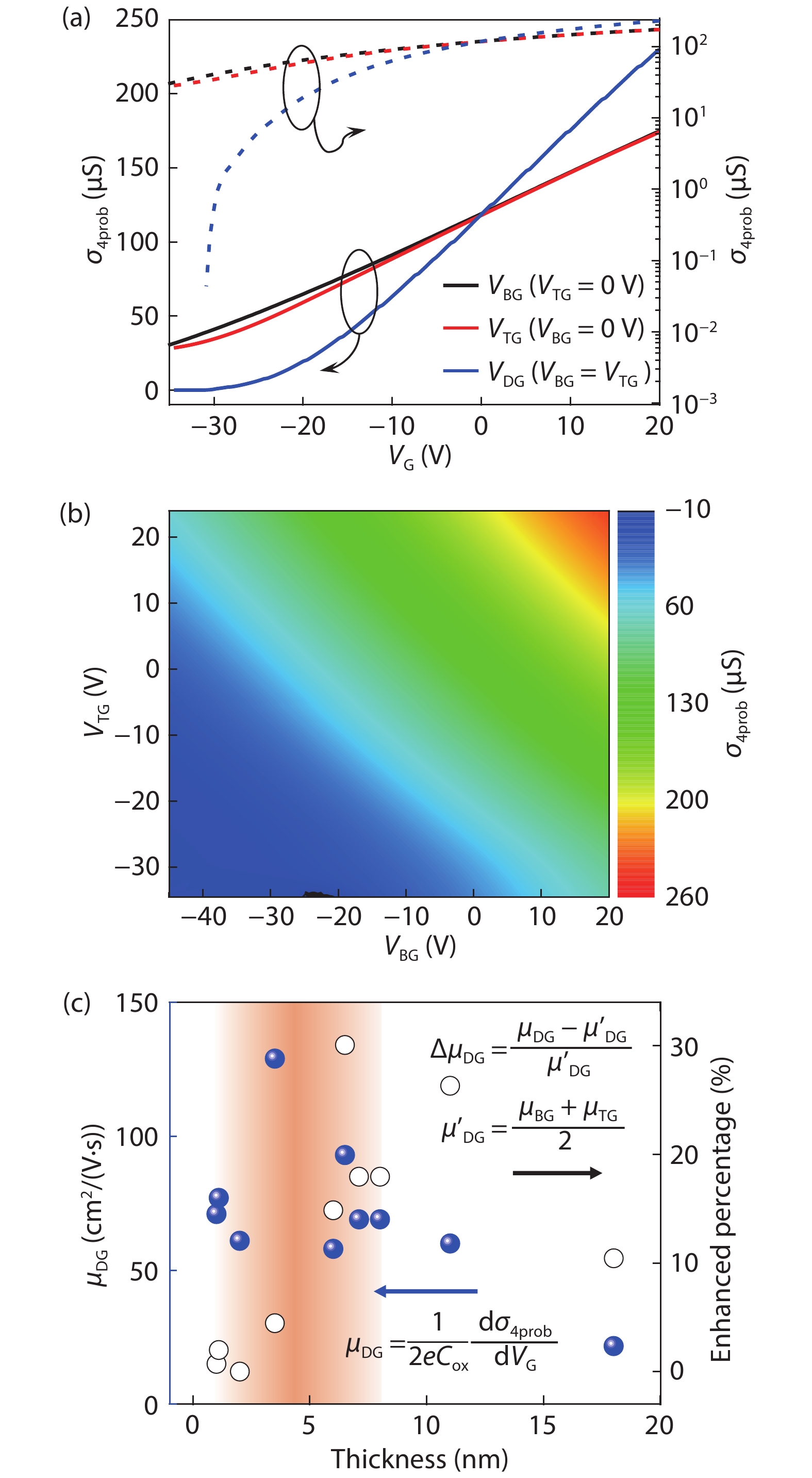

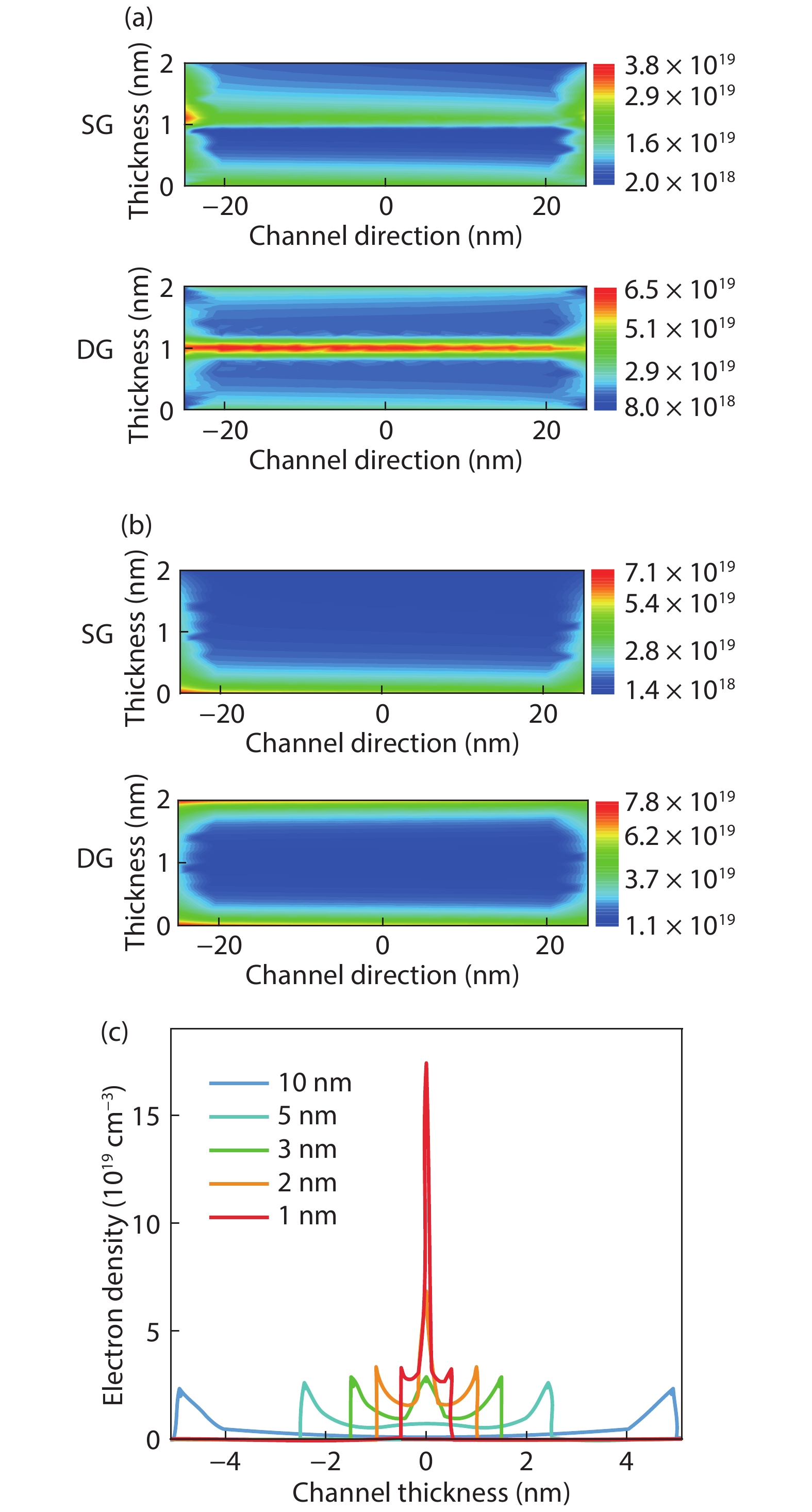

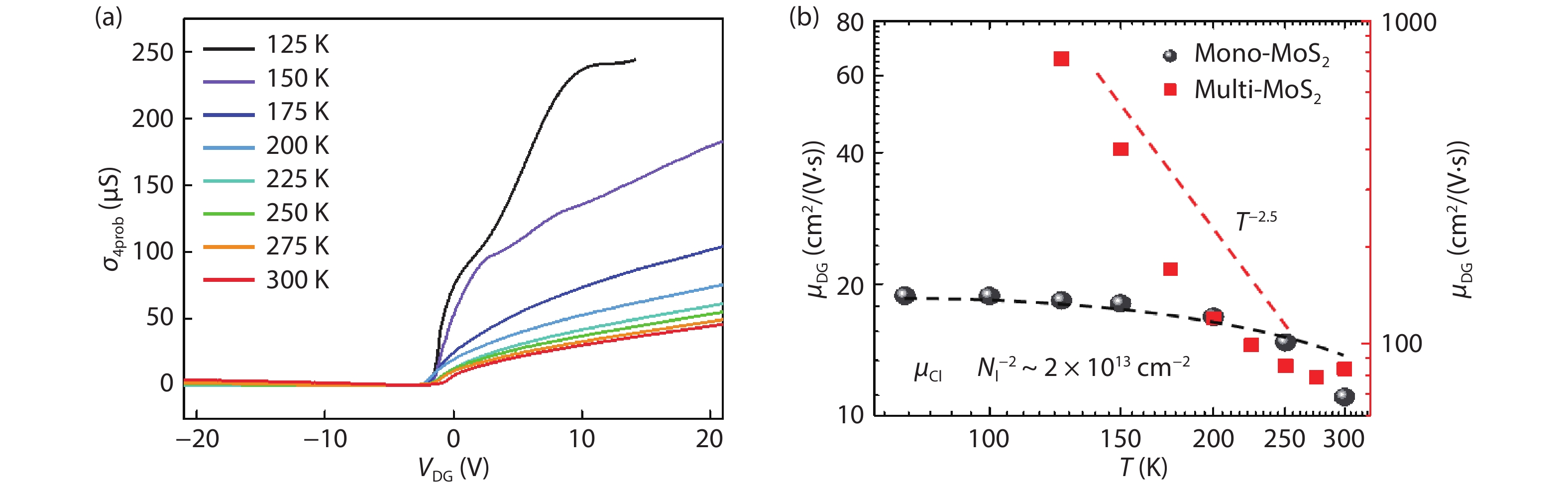

Semiconductive two dimensional (2D) materials have attracted significant research attention due to their rich band structures and promising potential for next-generation electrical devices. In this work, we investigate the MoS2 field-effect transistors (FETs) with a dual-gated (DG) architecture, which consists of symmetrical thickness for back gate (BG) and top gate (TG) dielectric. The thickness-dependent charge transport in our DG-MoS2 device is revealed by a four-terminal electrical measurement which excludes the contact influence, and the TCAD simulation is also applied to explain the experimental data. Our results indicate that the impact of quantum confinement effect plays an important role in the charge transport in the MoS2 channel, as it confines charge carriers in the center of the channel, which reduces the scattering and boosts the mobility compared to the single gating case. Furthermore, temperature-dependent transfer curves reveal that multi-layer MoS2 DG-FET is in the phonon-limited transport regime, while single layer MoS2 shows typical Coulomb impurity limited regime.-

Keywords:

- MoS2,

- field effect transistors,

- dual-gate,

- quantum confinement,

- Coulomb impurity

-

References

[1] Novoselov K S, Geim A K, Morozov S V, et al. Electric field effect in atomically thin carbon films. Science, 2004, 306(5696), 666 doi: 10.1126/science.1102896[2] Radisavljevic B, Radenovic A, Brivio J, et al. Single-layer MoS2 transistors. Nat Nanotechnol, 2011, 6(3), 147 doi: 10.1038/nnano.2010.279[3] Wang Q H, Kalantar-Zadeh K, Kis A, et al. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat Nanotechnol, 2012, 7(11), 699 doi: 10.1038/nnano.2012.193[4] Wu G, Wang X, Chen Y, et al. MoTe2 p–n homojunctions defined by ferroelectric polarization. Adv Mater, 2020, 32(16), 1907937 doi: 10.1002/adma.201907937[5] Tu L, Cao R, Wang X, et al. Ultrasensitive negative capacitance phototransistors. Nat Commun, 2020, 11(1), 101 doi: 10.1038/s41467-019-13769-z[6] Wu G, Tian B, Liu L, et al. Programmable transition metal dichalcogenide homojunctions controlled by nonvolatile ferroelectric domains. Nat Electron, 2020, 3(1), 43 doi: 10.1038/s41928-019-0350-y[7] Desai S B, Madhvapathy S R, Sachid A B, et al. MoS2 transistors with 1-nanometer gate lengths. Science, 2016, 354(6308), 99 doi: 10.1126/science.aah4698[8] Ahmed F, Choi M S, Liu X, et al. Carrier transport at the metal-MoS2 interface. Nanoscale, 2015, 7(20), 9222 doi: 10.1039/C5NR01044F[9] Baugher B W, Churchill H O, Yang Y, et al. Intrinsic electronic transport properties of high-quality monolayer and bilayer MoS2. Nano Lett, 2013, 13(9), 4212 doi: 10.1021/nl401916s[10] Saad I, Ahmadi M T, Ismail R, et al. Ballistic carrier transport in a quasi-two-dimensional nanoscale field effect transistor (FET). IEEE International Conference on Semiconductor Electronics, 2008, 470[11] Liu H, Neal A T, Ye P D. Channel length scaling of MoS2 MOSFETs. ACS Nano, 2012, 6(10), 8563 doi: 10.1021/nn303513c[12] Lee C, Yan H, Brus L E, et al. Anomalous lattice vibrations of single- and few-layer MoS2. ACS Nano, 2010, 4(5), 2695 doi: 10.1021/nn1003937[13] Mak K F, Lee C, Hone J, et al. Atomically thin MoS2: A new direct-gap semiconductor. Phys Rev Lett, 2010, 105(13), 136805 doi: 10.1103/PhysRevLett.105.136805[14] Han S W, Kwon H, Kim S K, et al. Band-gap transition induced by interlayer van der Waals interaction in MoS2. Phys Rev B, 2011, 84(4), S312 doi: 10.1103/PhysRevB.84.045409[15] Bolshakov P, Khosravi A, Zhao P, et al. Dual-gate MoS2 transistors with sub-10 nm top-gate high-k dielectrics. Appl Phys Lett, 2018, 112(25), 253502 doi: 10.1063/1.5027102[16] Zou X, Xu J, Huang H, et al. A comparative study on top-gated and bottom-gated multilayer MoS2 transistors with gate stacked dielectric of Al2O3/HfO2. Nanotechnology, 2018, 29(24), 245201 doi: 10.1088/1361-6528/aab9cb[17] Nourbakhsh A, Zubair A, Huang S, et al. 15-nm channel length MoS2 FETs with single-and double-gate structures. 2015 Symposium on VLSI Technology (VLSI Technology), 2015, T28[18] Lee G H, Cui X, Kim Y D, et al. Highly stable, dual-gated MoS2 transistors encapsulated by hexagonal boron nitride with gate-controllable contact, resistance, and threshold voltage. ACS Nano, 2015, 9(7), 7019 doi: 10.1021/acsnano.5b01341[19] Liu H, Ye P D. MoS2 dual-gate MOSFET with atomic-layer-deposited Al2O3 as top-gate dielectric. IEEE Electron Device Lett, 2012, 33(4), 546 doi: 10.1109/LED.2012.2184520[20] Liao F, Deng J, Chen X, et al. A dual-gate MoS2 photodetector based on interface coupling effect. Small, 2020, 16(1), 1904369 doi: 10.1002/smll.201904369[21] Liao F, Guo Z, Wang Y, et al. High-performance logic and memory devices based on a dual-gated MoS2 architecture. ACS Appl Electron Mater, 2020, 2, 111 doi: 10.1021/acsaelm.9b00628[22] Liao F, Sheng Y, Guo Z, et al. MoS2 dual-gate transistors with electrostatically doped contacts. Nano Res, 2019, 12, 2515 doi: 10.1007/s12274-019-2478-5[23] Bao W, Liu G, Zhao Z, et al. Lithography-free fabrication of high quality substrate-supported and freestanding graphene devices. Nano Res, 2010, 3(2), 98 doi: 10.1007/s12274-010-1013-5[24] Das S, Chen H Y, Penumatcha A V, et al. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett, 2013, 13(1), 100 doi: 10.1021/nl303583v[25] Liu Y, Guo J, Zhu E, et al. Approaching the Schottky–Mott limit in van der Waals metal –semiconductor junctions. Nature, 2018, 557(7707), 696 doi: 10.1038/s41586-018-0129-8[26] Bao W, Cai X, Kim D, et al. High mobility ambipolar MoS2 field-effect transistors: Substrate and dielectric effects. Appl Phys Lett, 2012, 102(4), 042104 doi: 10.1063/1.4789365[27] Lin M W, Kravchenko I I, Fowlkes J, et al. Thickness-dependent charge transport in few-layer MoS2 field-effect transistors. Nanotechnology, 2016, 27(16), 165203 doi: 10.1088/0957-4484/27/16/165203[28] Anconaand M G, Iafrate G J. Quantum correction to the equation of state of an electron gas in a semiconductor. Phys Rev B, 1989, 39(13), 9536 doi: 10.1103/PhysRevB.39.9536[29] Uchida K, Koga J, Takagib S. Experimental study on electron mobility in ultrathin-body silicon-on-insulator metal–oxide–semiconductor field-effect transistors. J Appl Phys, 2007, 102(7), 074510 doi: 10.1063/1.2785957[30] Fivaz R, Mooser E. Mobility of charge carriers in semiconducting layer structures. Phys Rev, 1967, 163(3), 743 doi: 10.1103/PhysRev.163.743[31] Kaasbjerg K, Thygesen K S, Jacobsen K W. Phonon-limited mobility in n-type single-layer MoS2 from first principles. Phys Rev B, 2012, 85(11), 115317 doi: 10.1103/PhysRevB.85.115317[32] Ma N, Jena D. Charge scattering and mobility in atomically thin semiconductors. Phys Rev X, 2014, 4(1), 011043 doi: 10.1103/physrevx.4.011043[33] Ong Z Y, Fischetti M V. Mobility enhancement and temperature dependence in top-gated single-layer MoS2. Physics, 2013, 88(16), 1653 doi: 10.1103/PhysRevB.88.165316 -

Proportional views

DownLoad:

DownLoad: