| Citation: |

Zhaohui Sun, Yang Feng, Peng Guo, Zheng Dong, Junyu Zhang, Jing Liu, Xuepeng Zhan, Jixuan Wu, Jiezhi Chen. Flash-based in-memory computing for stochastic computing in image edge detection[J]. Journal of Semiconductors, 2023, 44(5): 054101. doi: 10.1088/1674-4926/44/5/054101

****

Z H Sun, Y Feng, P Guo, Z Dong, J Y Zhang, J Liu, X P Zhan, J X Wu, J Z Chen. Flash-based in-memory computing for stochastic computing in image edge detection[J]. J. Semicond, 2023, 44(5): 054101. doi: 10.1088/1674-4926/44/5/054101

|

Flash-based in-memory computing for stochastic computing in image edge detection

DOI: 10.1088/1674-4926/44/5/054101

More Information

-

Abstract

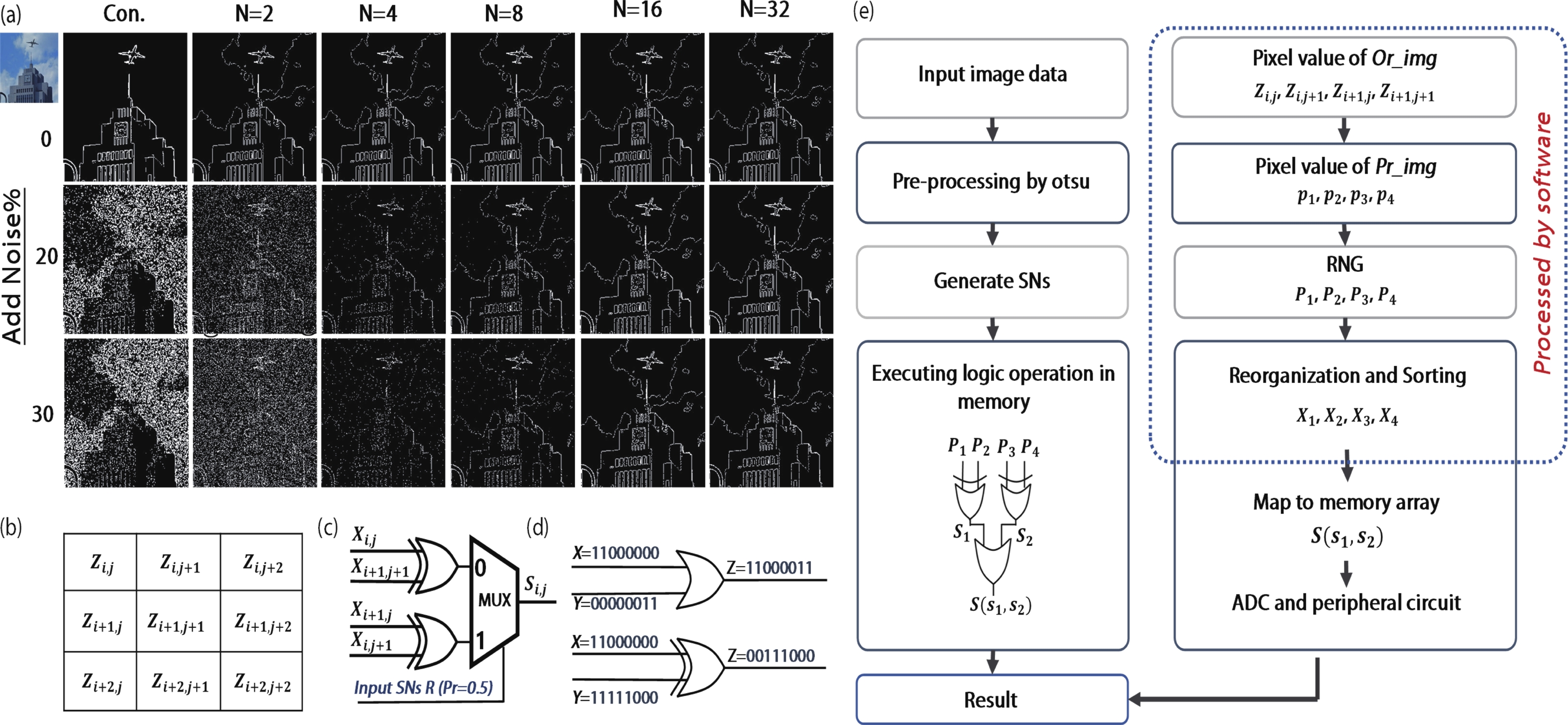

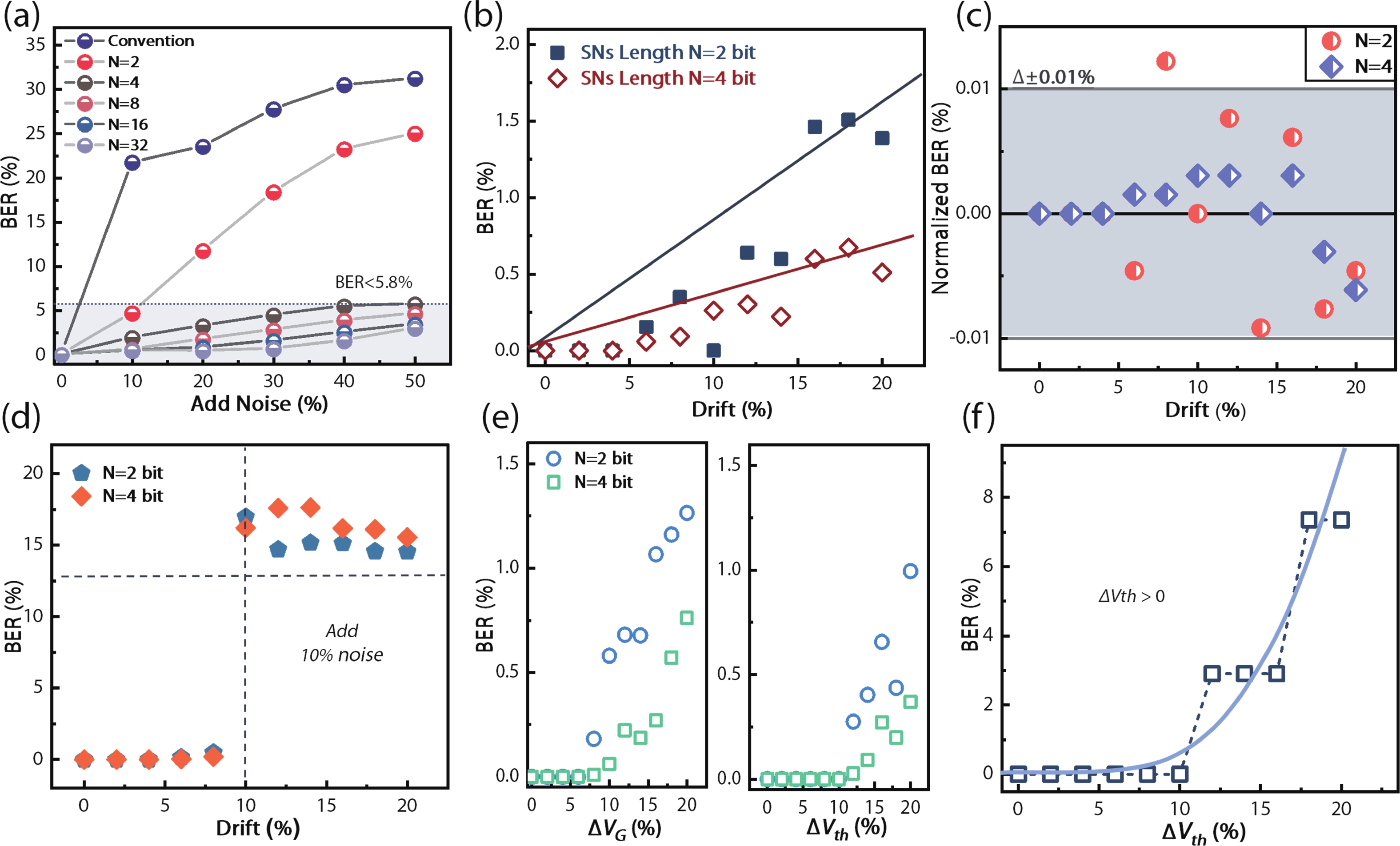

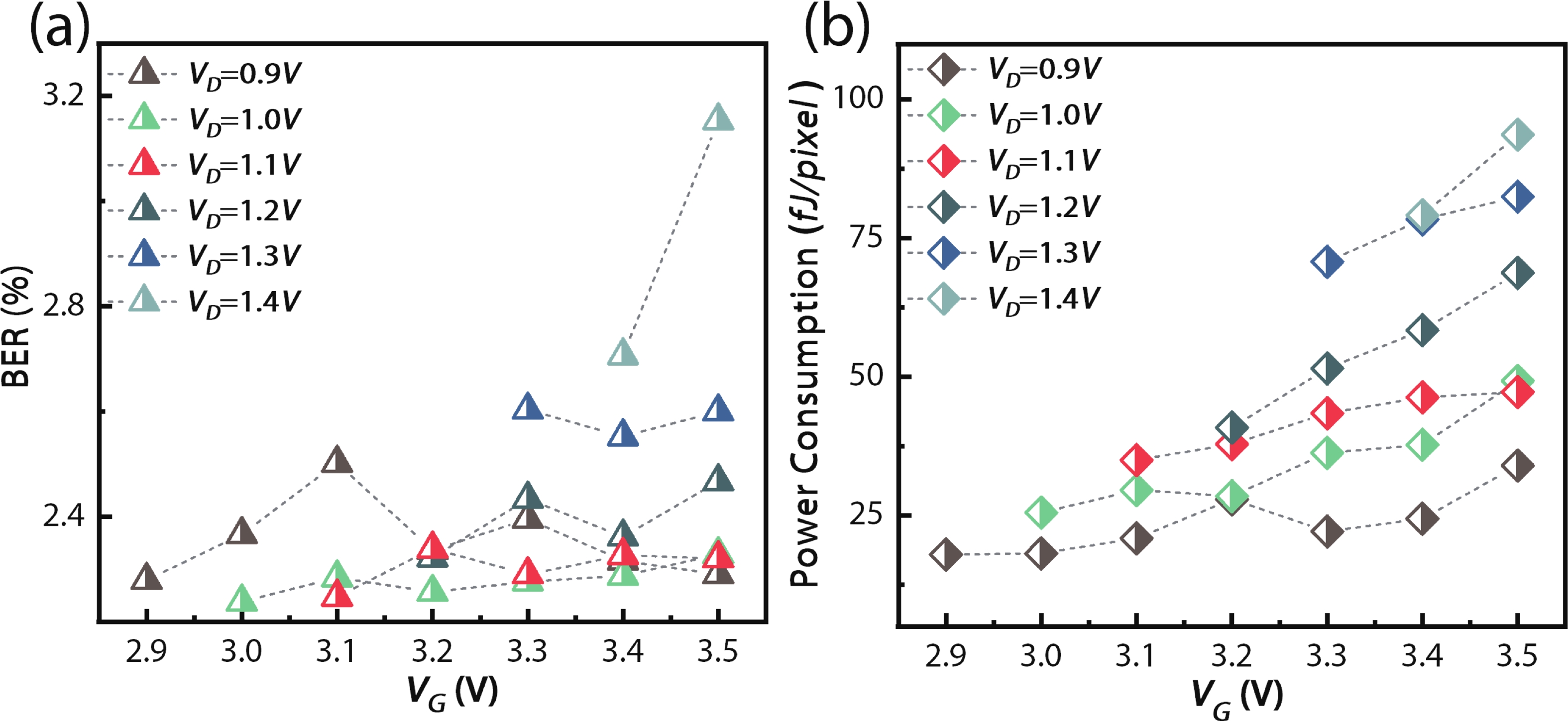

The “memory wall” of traditional von Neumann computing systems severely restricts the efficiency of data-intensive task execution, while in-memory computing (IMC) architecture is a promising approach to breaking the bottleneck. Although variations and instability in ultra-scaled memory cells seriously degrade the calculation accuracy in IMC architectures, stochastic computing (SC) can compensate for these shortcomings due to its low sensitivity to cell disturbances. Furthermore, massive parallel computing can be processed to improve the speed and efficiency of the system. In this paper, by designing logic functions in NOR flash arrays, SC in IMC for the image edge detection is realized, demonstrating ultra-low computational complexity and power consumption (25.5 fJ/pixel at 2-bit sequence length). More impressively, the noise immunity is 6 times higher than that of the traditional binary method, showing good tolerances to cell variation and reliability degradation when implementing massive parallel computation in the array. -

References

[1] Wang Y, Yang Y, Hao Y, et al. Embracing the era of neuromorphic computing. J Semicond, 2021, 42(1), 010301 doi: 10.1088/1674-4926/42/1/010301[2] Hao Y, Wu H, Yang Y, et al. Preface to the special issue on beyond moore: Resistive switching devices for emerging memory and neuromorphic computing. J Semicond, 2021, 42(1), 010101 doi: 10.1088/1674-4926/42/1/010101[3] Lue H T, Hsu P K, Wei M L, et al. Optimal design methods to transform 3D NAND flash into a high-density, high-bandwidth and low-power nonvolatile computing in memory (nvCIM) accelerator for deep-learning neural networks (DNN). 2019 IEEE International Electron Devices Meeting (IEDM), 2019, 38.1.1 doi: 10.1109/IEDM19573.2019.8993652[4] Li P, Lilja D J. Using stochastic computing to implement digital image processing algorithms. 2011 IEEE 29th International Conference on Computer Design (ICCD), 2011, 154 doi: 10.1109/ICCD.2011.6081391[5] Zhang Y, Wang R, Jiang X, et al. Design guidelines of stochastic computing based on FinFET: A technology-circuit perspective. 2017 IEEE International Electron Devices Meeting (IEDM), 2017, 6.6.1 doi: 10.1109/IEDM.2017.8268342[6] Xiong H, He G. Hardware implementation of an improved stochastic computing based deep neural network using short sequence length. IEEE Trans Circuits Syst II, 2020, 67(11), 2667 doi: 10.1109/TCSII.2020.2969691[7] Otsu N. A threshold selection method from gray-level histograms. IEEE Trans Syst, Man, Cyber, 1979, 9(1), 62 doi: 10.1109/TSMC.1979.4310076[8] Mendiratta N, Tripathi S L. A review on performance comparison of advanced MOSFET structures below 45 nm technology node. J Semicond, 2020, 41(6), 061401 doi: 10.1088/1674-4926/41/6/061401[9] Gonzalez, Rafael C, Digital image processing. Pearson education India. 3rd ed. , 2009, 242[10] Feng Y, Chen B, Liu J, et al. Design-technology co-optimizations (DTCO) for general-purpose computing in-memory based on 55nm NOR flash technology. 2021 IEEE International Electron Devices Meeting (IEDM), 2021, 12.1.1 doi: 10.1109/IEDM19574.2021.9720625[11] Kingra S K, Parmar V, Chang C C, et al. SLIM: simultaneous logic-in-memory computing exploiting bilayer analog OxRAM devices. Sci Rep, 2020, 10(1), 1 doi: 10.1038/s41598-019-56847-4[12] Lee J, Park B G, Kim Y. Implementation of boolean logic functions in charge trap flash for in-memory computing. IEEE Electron Device Lett, 2019, 40(9), 1358 doi: 10.1109/LED.2019.2928335[13] Milo V, Malavena G, Monzio Compagnoni C, et al. Memristive and CMOS devices for neuromorphic computing. Materials, 2020, 13(1), 166 doi: 10.3390/ma13010166[14] Yao P, Wu H, Gao B, et al. Fully hardware-implemented memristor convolutional neural network. Nature, 2020, 577(7792), 641 doi: 10.1038/s41586-020-1942-4 -

Proportional views

DownLoad:

DownLoad:

Zhaohui Sun:got her B.S. from Shandong University in 2018. Now she is an M.S. student at Shandong University under the supervision of Prof. Jiezhi Chen. Her research focuses on in-memory computing and NOR Flash device reliability

Zhaohui Sun:got her B.S. from Shandong University in 2018. Now she is an M.S. student at Shandong University under the supervision of Prof. Jiezhi Chen. Her research focuses on in-memory computing and NOR Flash device reliability Jiezhi Chen:received the Ph.D. degree from the Department of Informatics and Electronics, the University of Tokyo, in 2009. He is currently a Professor at the School of Information Science and Engineering, Shandong University, China. His research interests include flash memory, emerging non-volatile memories, nanoscale transistors, and computing-in-memory architectures, with the main focus on reliability physics and optimization strategies

Jiezhi Chen:received the Ph.D. degree from the Department of Informatics and Electronics, the University of Tokyo, in 2009. He is currently a Professor at the School of Information Science and Engineering, Shandong University, China. His research interests include flash memory, emerging non-volatile memories, nanoscale transistors, and computing-in-memory architectures, with the main focus on reliability physics and optimization strategies