| Citation: |

Peng Yuan, Yuting Chen, Liguo Chai, Zhengying Jiao, Qingjie Luan, Yongqing Shen, Ying Zhang, Jibin Leng, Xueli Ma, Jinjuan Xiang, Guilei Wang, Chao Zhao. On the relationship between imprint and reliability in Hf0.5Zr0.5O2 based ferroelectric random access memory[J]. Journal of Semiconductors, 2024, 45(4): 042301. doi: 10.1088/1674-4926/45/4/042301

****

P Yuan, Y T Chen, L G Chai, Z Y Jiao, Q J Luan, Y Q Shen, Y Zhang, J B Leng, X L Ma, J J Xiang, G L Wang, C Zhao. On the relationship between imprint and reliability in Hf0.5Zr0.5O2 based ferroelectric random access memory[J]. J. Semicond, 2024, 45(4): 042301. doi: 10.1088/1674-4926/45/4/042301

|

On the relationship between imprint and reliability in Hf0.5Zr0.5O2 based ferroelectric random access memory

DOI: 10.1088/1674-4926/45/4/042301

More Information

-

Abstract

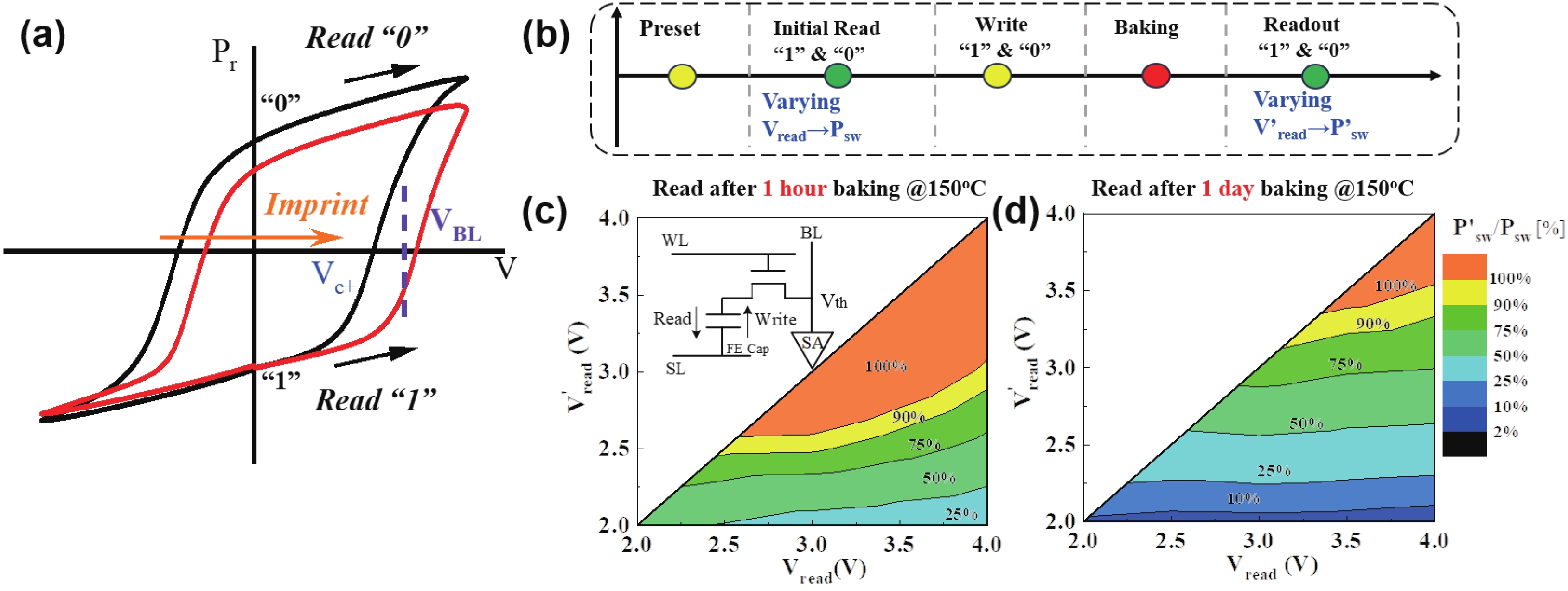

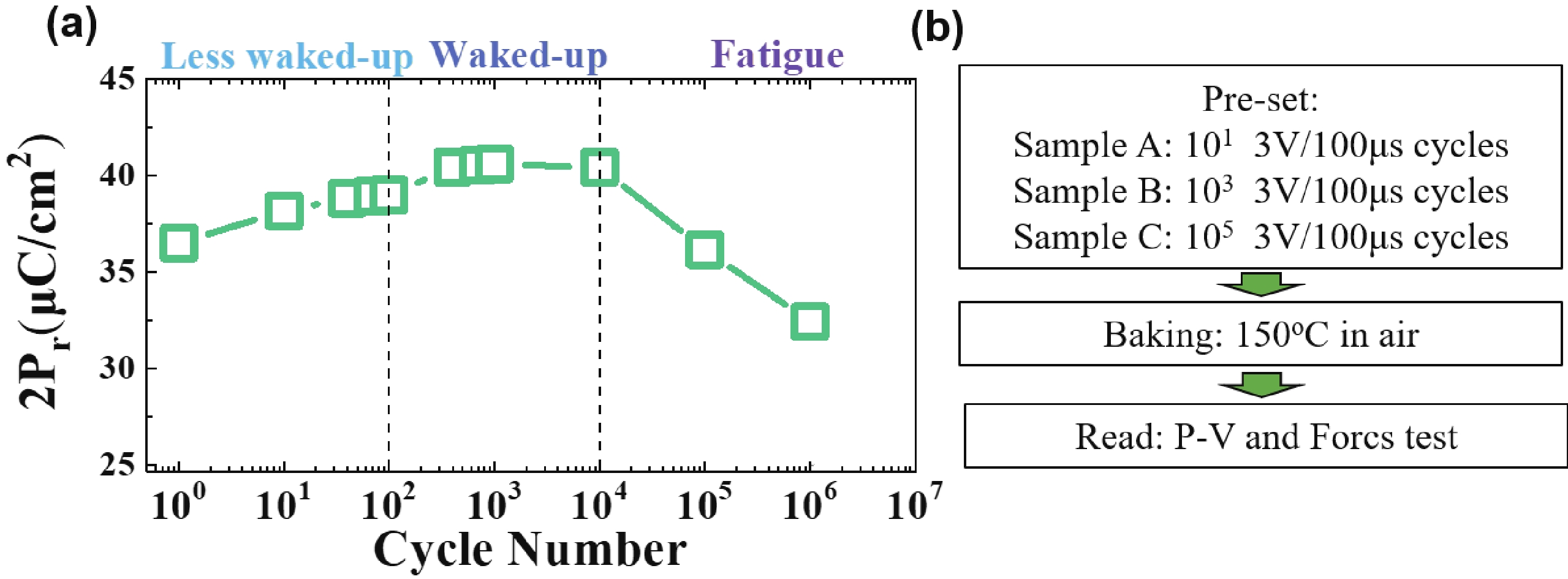

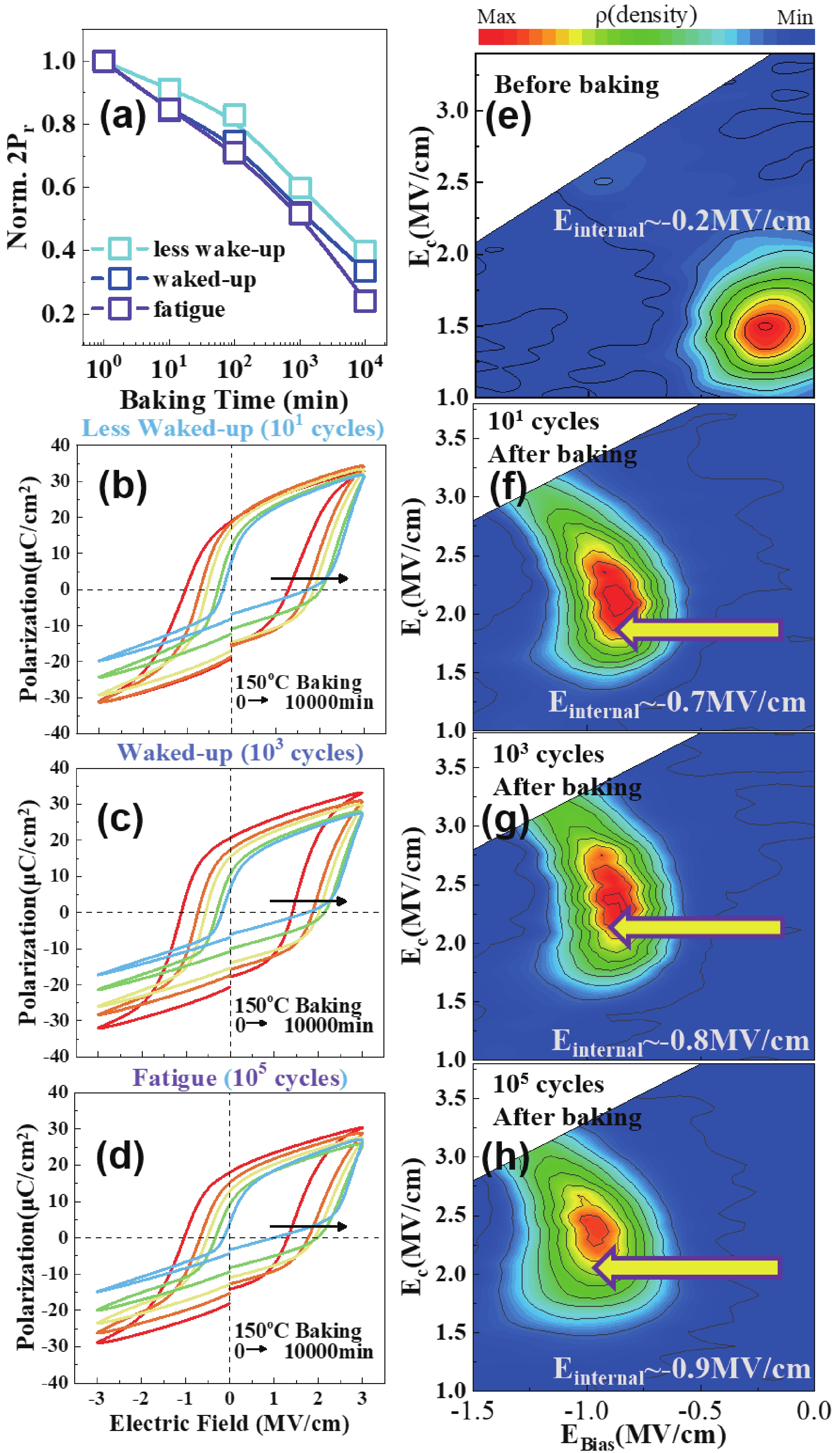

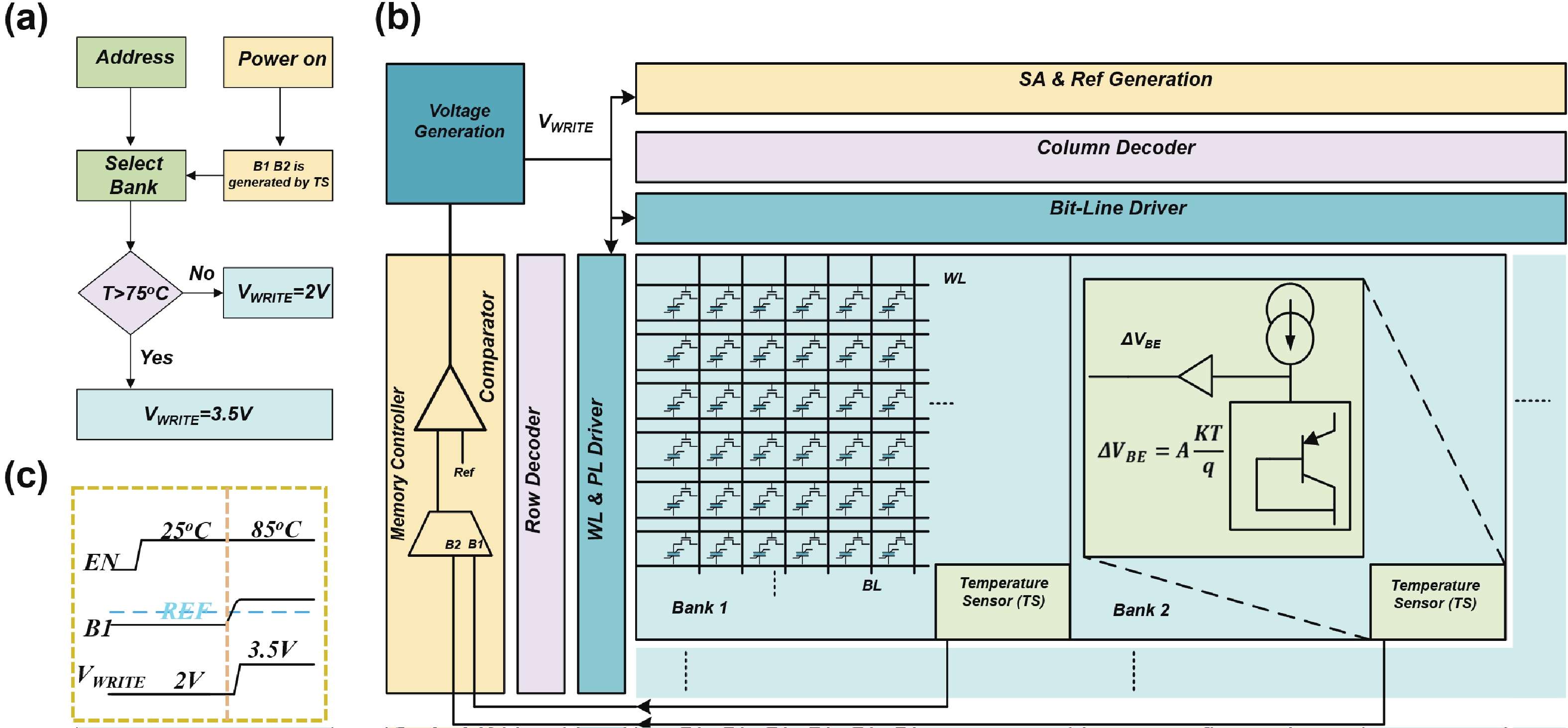

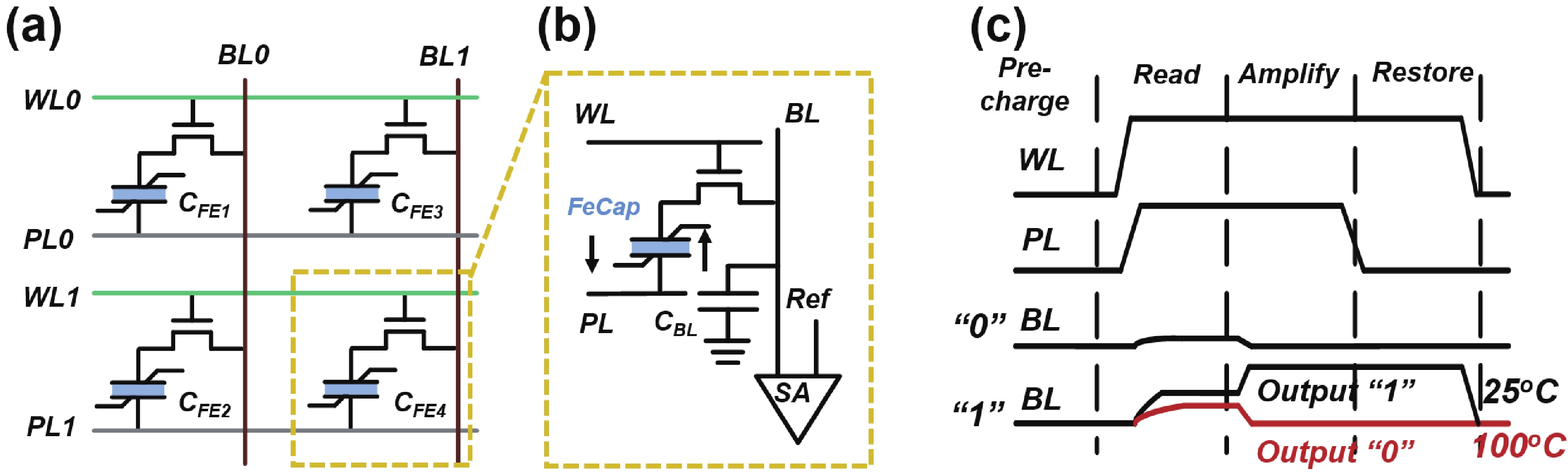

The detrimental effect of imprint, which can cause misreading problem, has hindered the application of ferroelectric HfO2. In this work, we present results of a comprehensive reliability evaluation of Hf0.5Zr0.5O2-based ferroelectric random access memory. The influence of imprint on the retention and endurance is demonstrated. Furthermore, a solution in circuity is proposed to effectively solve the misreading problem caused by imprint.-

Keywords:

- FeRAM,

- HZO,

- imprint,

- reliability

-

References

[1] Park M H, Lee Y H, Kim H J, et al. Ferroelectricity and antiferroelectricity of doped thin HfO2-based films. Adv Mater, 2015, 27, 1811 doi: 10.1002/adma.201404531[2] Schroeder U, Park M H, Mikolajick T, et al. The fundamentals and applications of ferroelectric HfO2. Nat Rev Mater, 2022, 7, 653 doi: 10.1038/s41578-022-00431-2[3] Fan Z, Chen J S, Wang J. Ferroelectric HfO2-based materials for next-generation ferroelectric memories. J Adv Dielect, 2016, 6, 1630003 doi: 10.1142/S2010135X16300036[4] Böscke T S, Müller J, Bräuhaus D, et al. Ferroelectricity in hafnium oxide thin films. Appl Phys Lett, 2011, 99, 102903. doi: 10.1063/1.3634052[5] Park M H, Lee Y H, Mikolajick T, et al. Review and perspective on ferroelectric HfO2-based thin films for memory applications. MRS Commun, 2018, 8, 795 doi: 10.1557/mrc.2018.175[6] Ali T, Polakowski P, Kühnel K, et al. A multilevel FeFET memory device based on laminated HSO and HZO ferroelectric layers for high-density storage. 2019 IEEE International Electron Devices Meeting (IEDM), 2019, 28.7. 1 doi: 10.1109/IEDM19573.2019.8993642[7] Sharma A, Roy K. Design space exploration of hysteresis-free HfZrOx-based negative capacitance FETs. IEEE Electron Device Lett, 2017, 38, 1165 doi: 10.1109/LED.2017.2714659[8] Okuno J, Kunihiro T, Konishi K, et al. 1T1C FeRAM memory array based on ferroelectric HZO with capacitor under bitline. IEEE J Electron Devices Soc, 2021, 10, 29 doi: 10.1109/JEDS.2021.3129279[9] Francois T, Grenouillet L, Coignus J, et al. Demonstration of BEOL-compatible ferroelectric Hf0.5Zr0.5O2 scaled FeRAM co-integrated with 130nm CMOS for embedded NVM applications. 2019 IEEE International Electron Devices Meeting (IEDM), 2019, 15.7. 1 doi: 10.1109/IEDM19573.2019.8993485[10] Kuk S H, Han S M, Kim B H, et al. An investigation of HZO-based n/p-FeFET operation mechanism and improved device performance by the electron detrapping mode. IEEE Trans Electron Devices, 2022, 69, 2080 doi: 10.1109/TED.2022.3154687[11] Zhou Y, Chan H K, Lam C H, et al. Mechanisms of imprint effect on ferroelectric thin films. J Appl Phys, 2005, 98, 024111. doi: 10.1063/1.1984075[12] Yuan P, Mao G Q, Cheng Y, et al. Microscopic mechanism of imprint in hafnium oxide-based ferroelectrics. Nano Res, 2022, 15, 3667 doi: 10.1007/s12274-021-4047-y[13] Jiang P F, Luo Q, Xu X X, et al. Wake-up effect in HfO2-based ferroelectric films. Adv Elect Materials, 2021, 7, 2000728 doi: 10.1002/aelm.202000728[14] Zhou Y, Zhang Y K, Yang Q, et al. The effects of oxygen vacancies on ferroelectric phase transition of HfO2-based thin film from first-principle. Comput Mater Sci, 2019, 167, 143 doi: 10.1016/j.commatsci.2019.05.041[15] Cheng Y, Gao Z M, Ye K H, et al. Reversible transition between the polar and antipolar phases and its implications for wake-up and fatigue in HfO2-based ferroelectric thin film. Nat Commun, 2022, 13, 645 doi: 10.1038/s41467-022-28236-5[16] Grimley E D, Schenk T, Sang X H, et al. Structural changes underlying field-cycling phenomena in ferroelectric HfO2 thin films. Adv Elect Materials, 2016, 2, 1600173 doi: 10.1002/aelm.201600173[17] Sünbül A, Lehninger D, Lederer M, et al. A study on imprint behavior of ferroelectric hafnium oxide caused by high-temperature annealing. Phys Status Solidi A, 2023, 220, 2300067. doi: 10.1002/pssa.202300067[18] Bao K Y, Liao J J, Yan F, et al. Enhanced endurance and imprint properties in Hf0.5Zr0.5O2– δ ferroelectric capacitors by tailoring the oxygen vacancy. ACS Appl Electron Mater, 2023, 5, 4615 doi: 10.1021/acsaelm.3c00756[19] Yuan P, Wang B P, Yang Y, et al. Enhanced remnant polarization (30 μC/cm2) and retention of ferroelectric Hf0.5Zr0.5O2 by NH3 plasma treatment. IEEE Electron Device Lett, 2022, 43, 1045 doi: 10.1109/LED.2022.3178867[20] Nie B W, Huang Y Q, Wang Y, et al. Thermal induced Pr degradation under low-voltage operation in HfZrO ferroelectric film: Phenomenon and underlying mechanism. IEEE Electron Device Lett, 2023, 44, 1456 doi: 10.1109/LED.2023.3296797 -

Proportional views

Peng Yuan received his Ph.D. degree in Institute of Microelectronics, Chinese Academy of Sciences and University of Chinese Academy of Sciences. In 2022, he joined the Beijing Superstring Academy of Memory Technology as an assistant. His current research interests include high-k semiconductor materials and Emerging memory devices.

Peng Yuan received his Ph.D. degree in Institute of Microelectronics, Chinese Academy of Sciences and University of Chinese Academy of Sciences. In 2022, he joined the Beijing Superstring Academy of Memory Technology as an assistant. His current research interests include high-k semiconductor materials and Emerging memory devices. Xueli Ma received her Ph.D. degree in Microelectronics and Solid-State Electronics from University of Chinese Academy of Sciences. She worked in the Institute of Microelectronics (IME), Chinese Academy of Sciences as an assistant professor and associate professor for 8 years. and joined SAMT at 2022. Her research interests cover high-k/metal gate stack of advanced CMOS, high-mobility channel SiGe/Ge-based processing and device technology, and oxide semiconductor-based TFTs. Emerging.

Xueli Ma received her Ph.D. degree in Microelectronics and Solid-State Electronics from University of Chinese Academy of Sciences. She worked in the Institute of Microelectronics (IME), Chinese Academy of Sciences as an assistant professor and associate professor for 8 years. and joined SAMT at 2022. Her research interests cover high-k/metal gate stack of advanced CMOS, high-mobility channel SiGe/Ge-based processing and device technology, and oxide semiconductor-based TFTs. Emerging. Jinjuan Xiang received her Ph.D. degree in Microelectronics and Solid-State Electronics from University of Chinese Academy of Sciences. Her work focused on ALD process and material especially for Nano CMOS and DRAM application.

Jinjuan Xiang received her Ph.D. degree in Microelectronics and Solid-State Electronics from University of Chinese Academy of Sciences. Her work focused on ALD process and material especially for Nano CMOS and DRAM application. Guilei Wang received his Bachelor's degree in 2005 and his PhD in 2016 from the University of Chinese Academy of Sciences. He has been worked as a professor at the Integrated Circuit Advanced Process Center at the Chinese Academy of Sciences until 2021. In October 2021, he joined the Beijing Superstring Academy of Memory Technology as a full professor. His research interests are focused on new materials, devices, and process integration for the IC industry.

Guilei Wang received his Bachelor's degree in 2005 and his PhD in 2016 from the University of Chinese Academy of Sciences. He has been worked as a professor at the Integrated Circuit Advanced Process Center at the Chinese Academy of Sciences until 2021. In October 2021, he joined the Beijing Superstring Academy of Memory Technology as a full professor. His research interests are focused on new materials, devices, and process integration for the IC industry.

DownLoad:

DownLoad: