| Citation: |

Zhongjie Guo, Ningmei Yu, Longsheng Wu. Column readout circuit with improved offset mismatch and charge sharing for CMOS image sensor[J]. Journal of Semiconductors, 2019, 40(12): 122404. doi: 10.1088/1674-4926/40/12/122404

****

Z J Guo, N M Yu, L S Wu, Column readout circuit with improved offset mismatch and charge sharing for CMOS image sensor[J]. J. Semicond., 2019, 40(12): 122404. doi: 10.1088/1674-4926/40/12/122404.

|

Column readout circuit with improved offset mismatch and charge sharing for CMOS image sensor

DOI: 10.1088/1674-4926/40/12/122404

More Information

-

Abstract

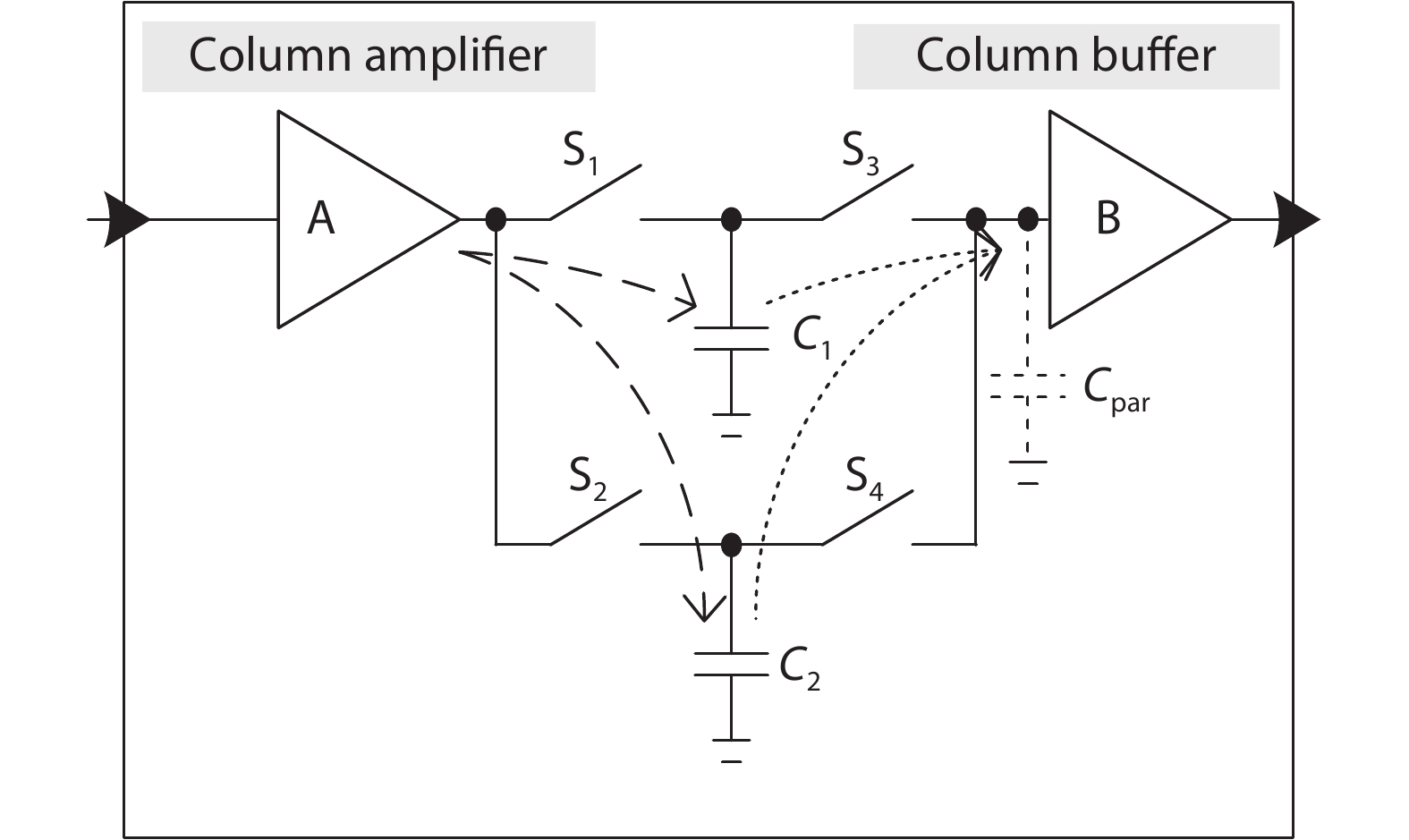

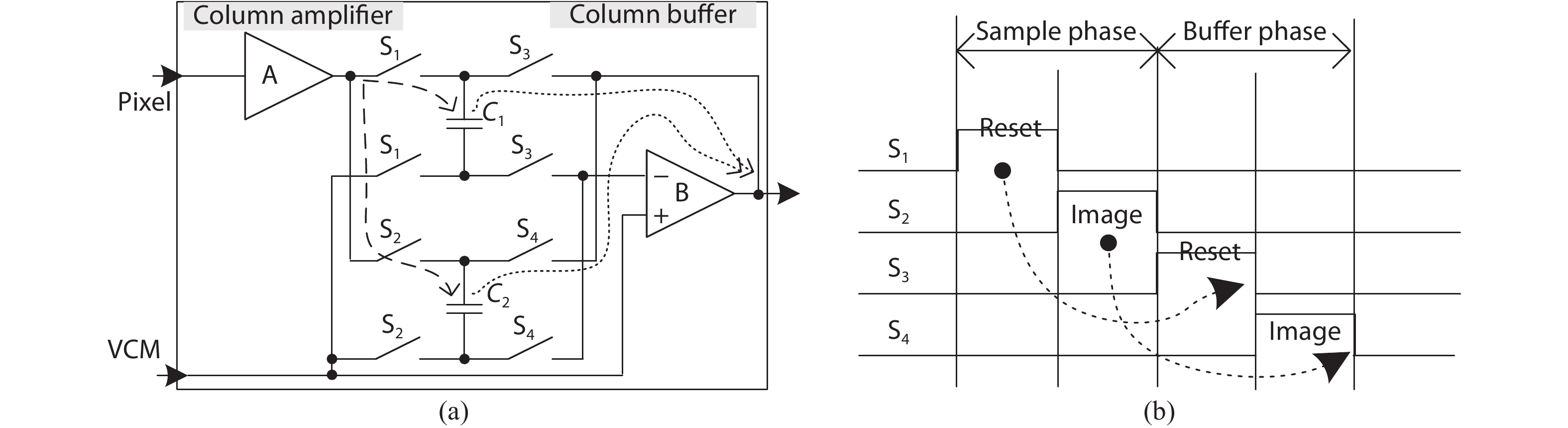

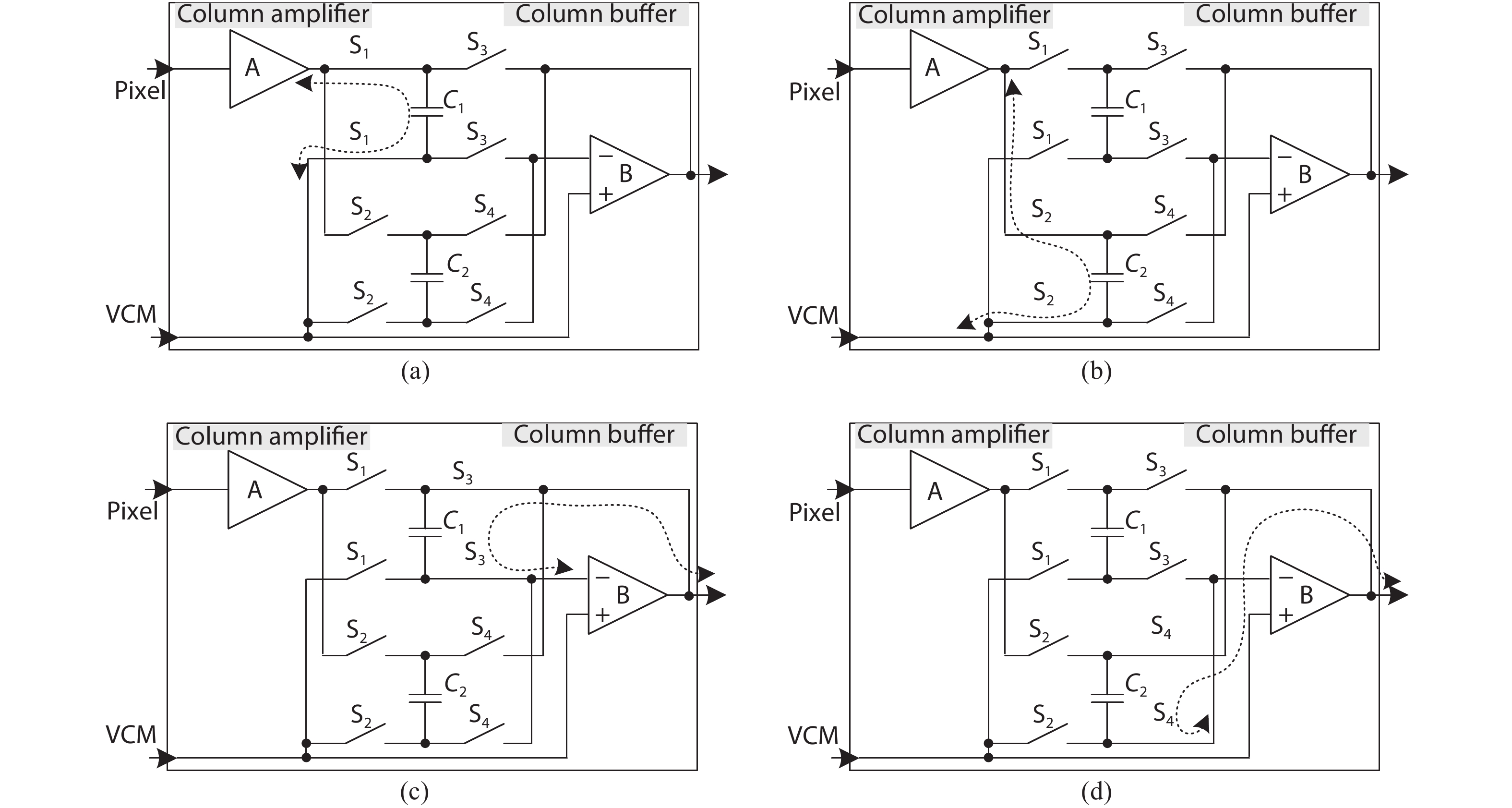

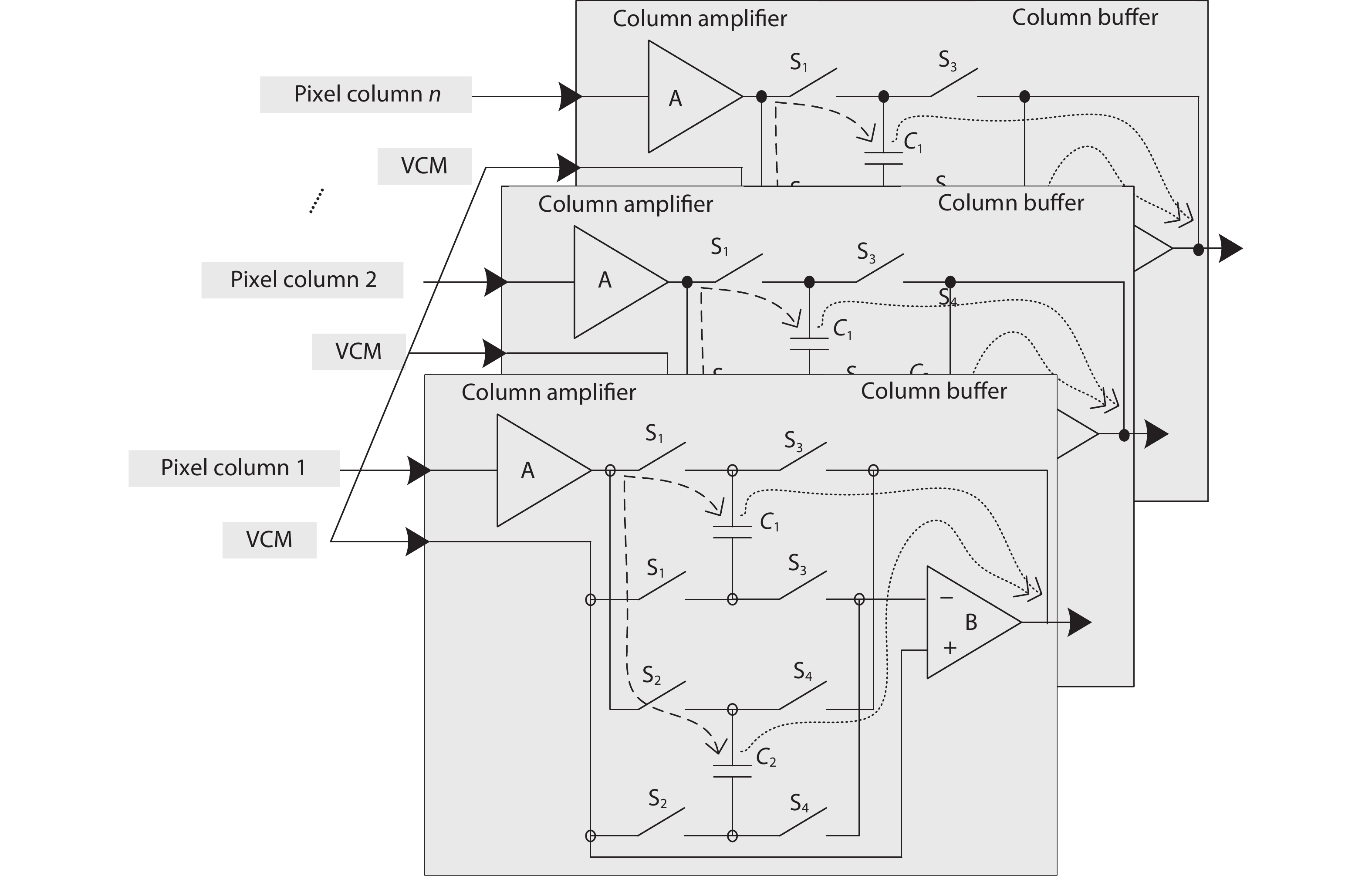

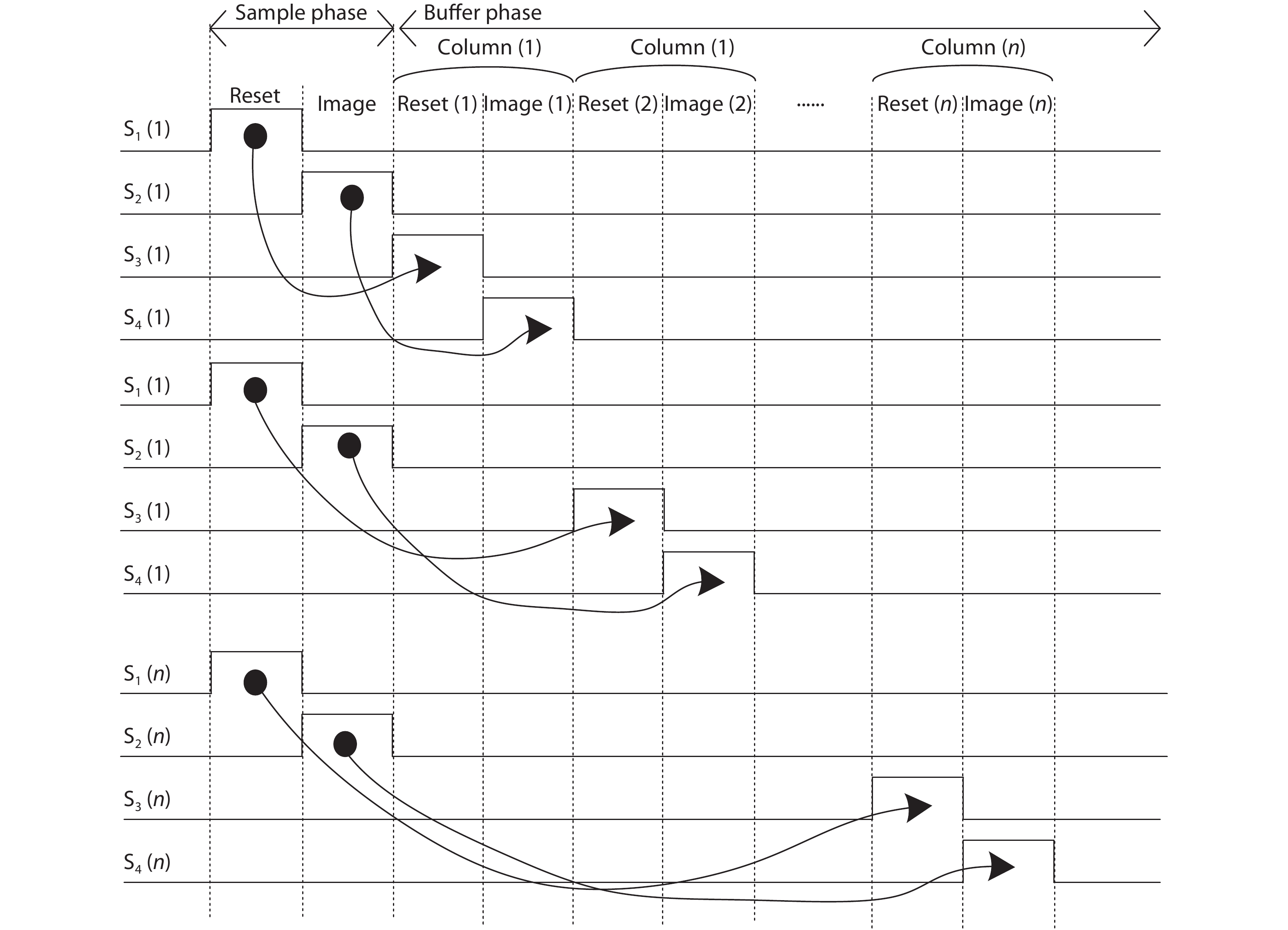

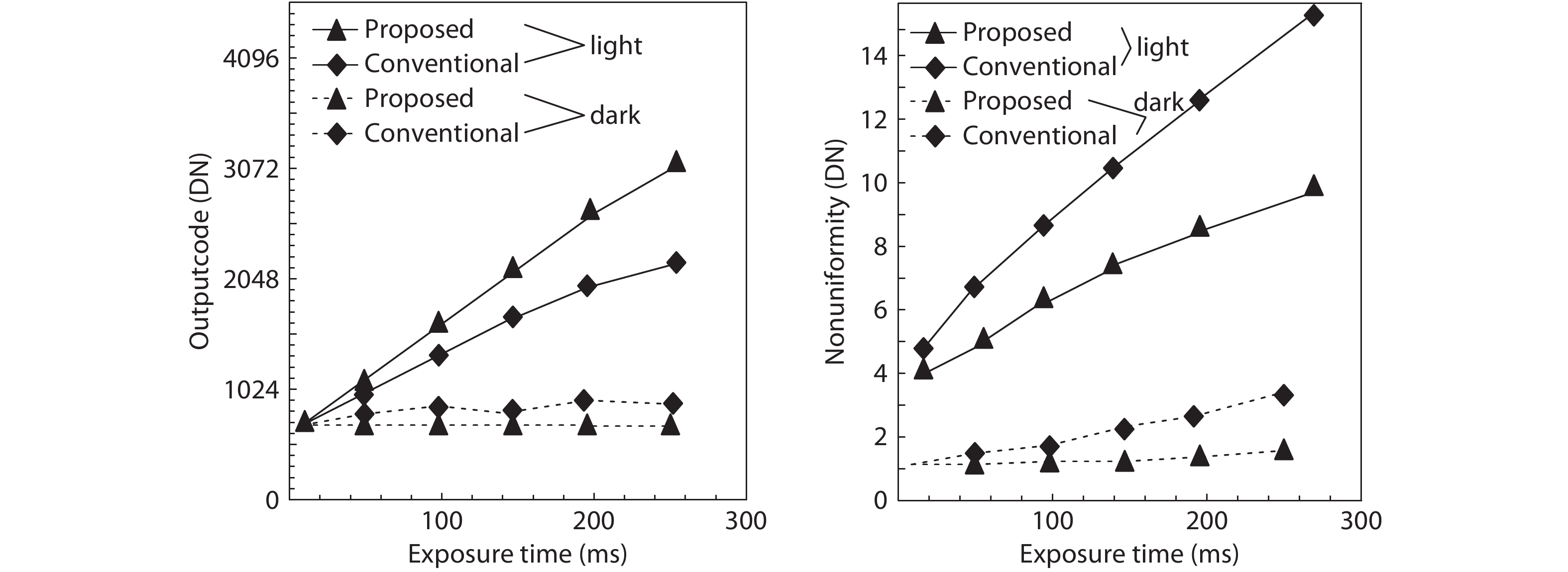

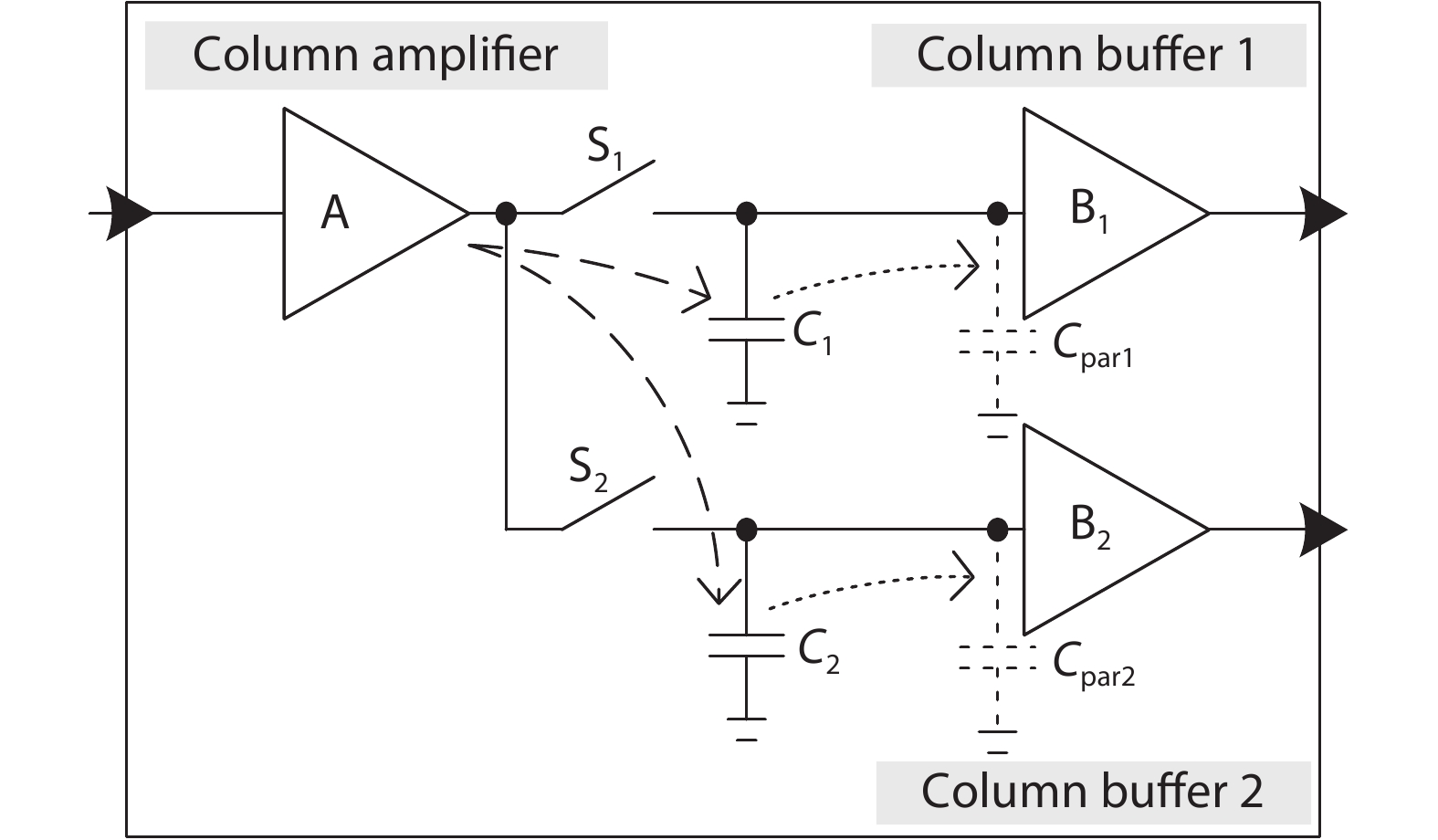

High linearity and low noise column readout chain are two key factors in CMOS image sensor. However, offset mismatch and charge sharing always exist in the conventional column wise readout implementation, even adopting the technology of correlated double sample. A simple column readout circuit with improved offset mismatch and charge sharing for CMOS image sensor is proposed in this paper. Based on the bottom plate sampling and fixed common level method, this novel design can avoid the offset nonuniformity between the two buffers. Also, the single buffer and switched capacitor technique can effectively suppress the charge sharing caused by the varied operating point. The proposed approach is experimentally verified in a 1024 × 1024 prototype chip designed and fabricated in 55 nm low power CMOS process. The measurement results show that the linear range is extended by 20%, the readout noise of bright and dark fields is reduced by 40% and 30% respectively, and the improved photo response nonuniformity is up to 1.16%. Finally, a raw sample image taken by the prototype sensor shows the excellent practical performance.-

Keywords:

- CMOS image sensor,

- column readout,

- buffer,

- offset mismatch,

- charge sharing

-

References

[1] Boukhayma A, Peizerat A, Enz C. Temporal readout noise analysis and reduction techniques for low-light CMOS image sensors. IEEE Trans Electron Devices, 2016, 63(1), 72 doi: 10.1109/TED.2015.2434799[2] Kawai N, Kawahito S. Noise analysis of high-gain, low-noise column readout circuits for CMOS image sensors. IEEE Trans Electron Devices, 2004, 51(2), 185 doi: 10.1109/TED.2003.822224[3] Yeh S F, Chou K Y, Tu H Y, et al. A 0.66erms- temporal-readout-noise 3-D-stacked CMOS image sensor with conditional correlated multiple sampling technique. IEEE J Solid-State Circuits, 2018, 53(2), 527 doi: 10.1109/JSSC.2017.2765927[4] Lim Y, Koh K, Kim K, et al. A 1.1e- temporal noise 1/3.2-inch 8 Mpixel CMOS image sensor using pseudo-multiple sampling. IEEE Int Solid-State Circuits Conf Dig Tech Papers (ISSCC), 2010, 396[5] Seo M W, Suh S, Lida T, et al. An 80 μV rms-temporal-noise 82 dB-dynamic-range CMOS image sensor with a 13-to-19 b variable-resolution column-parallel folding-integration/cyclic ADC. IEEE Int Solid-State Circuits Conf Dig Tech Papers (ISSCC), 2011, 400[6] Chen N, Zhong S Y, Zou M, et al. A low-noise CMOS image sensor with digital correlated multiple sampling. IEEE Trans Circuits Syst I, 2018, 65(1), 84 doi: 10.1109/TCSI.2017.2724855[7] Liu Q Y, Edward A, Kinyua M, et al. A low-power digitizer for back-illuminated 3-D-stacked CMOS image sensor readout with passing window and double auto-zeroing techniques. IEEE J Solid-State Circuits, 2017, 52(6), 1591 doi: 10.1109/JSSC.2017.2661843[8] Kawahito K. Signal processing architectures for low-noise high-resolution CMOS image sensors. IEEE Custom Intergrated Circuits Conference (CICC), 2007[9] Okura S, Nishikido O, Sadanaga Y, et al. A 3.7 M-pixel 1300-fps CMOS image sensor with 5.0 G-pixel/s high-speed readout circuit. IEEE J Solid-State Circuits, 2015, 50(4), 1016 doi: 10.1109/JSSC.2014.2387201[10] Watabe T, Kitamura K, Sawamoto T, et al. A 33M pixel 120fps CMOS image sensor using 12b column-parallel pipelined cyclic ADCs. IEEE Int Solid-State Circuits Conf (ISSCC) Dig Tech Papers, 2012, 388 -

Proportional views

DownLoad:

DownLoad: