| Citation: |

Jun Yin, Haoran Li, Xiaoqi Lin, Rui P. Martins, Pui-In Mak. Progress and trends of low-jitter fractional-N PLL[J]. Journal of Semiconductors, 2025, 46(7): 070203. doi: 10.1088/1674-4926/25040035

****

J Yin, H R Li, X Q Lin, R P Martins, and P I Mak, Progress and trends of low-jitter fractional-N PLL[J]. J. Semicond., 2025, 46(7), 070203 doi: 10.1088/1674-4926/25040035

|

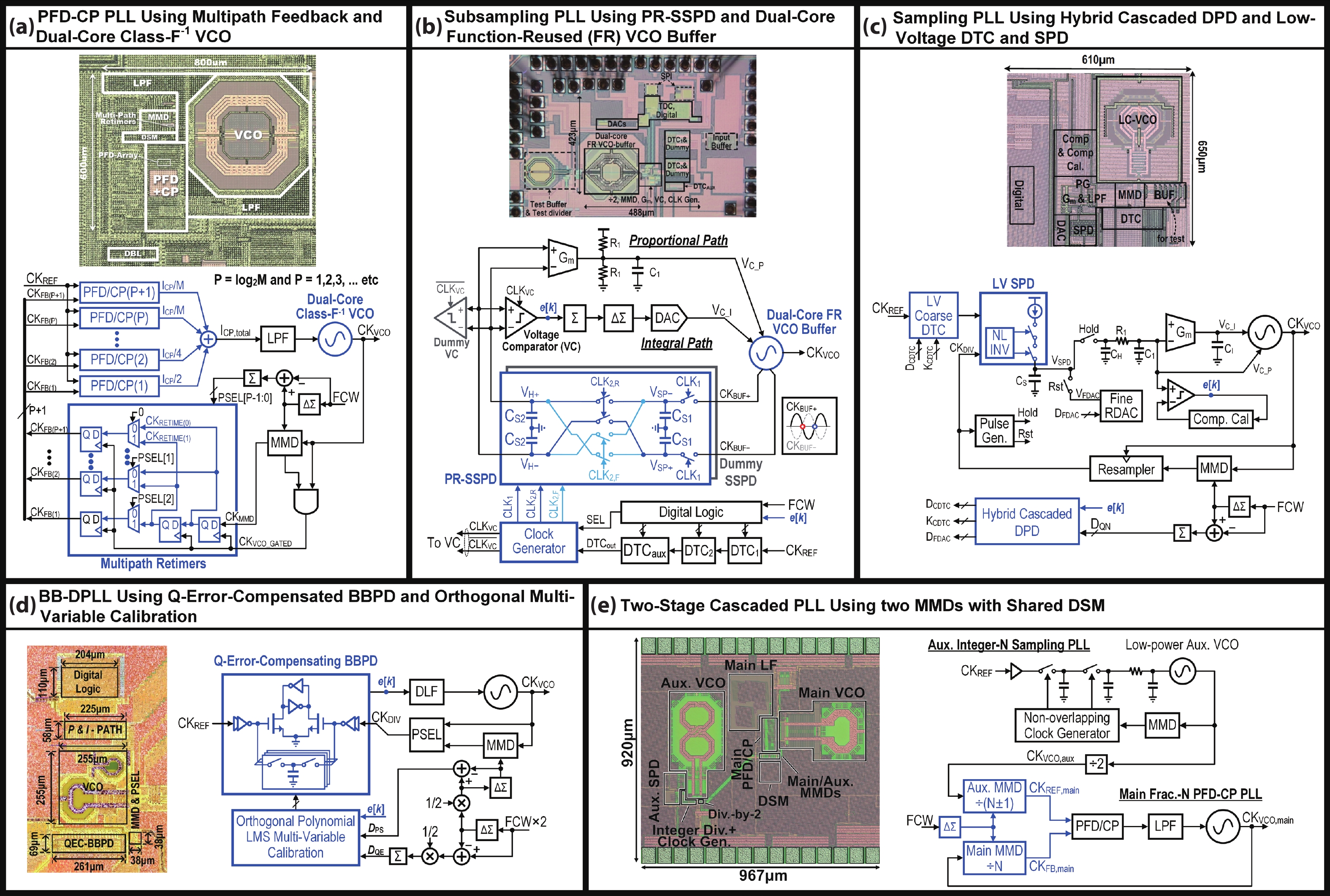

Progress and trends of low-jitter fractional-N PLL

DOI: 10.1088/1674-4926/25040035

CSTR: 32376.14.1674-4926.25040035

More Information-

References

[1] Wu W H. Low-jitter frequency generation techniques for 5G communication: A tutorial. IEEE Solid State Circuits Mag, 2021, 13(4), 44 doi: 10.1109/MSSC.2021.3111430[2] Lin T H, Ti C L, Liu Y H. Dynamic current-matching charge pump and gated-offset linearization technique for delta-sigma fractional-N PLLs. IEEE Trans Circuits Syst I Regul Pap, 2009, 56(5), 877 doi: 10.1109/TCSI.2009.2016180[3] Hsueh Y L, Cho L C, Shen C H, et al. A 0.29mm2 frequency synthesizer in 40nm CMOS with 0.19psrms jitter and <–100dBc reference spur for 802.11ac. 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2014, 472 doi: 10.1109/ISSCC.2014.6757518[4] Kennedy M P, Mazzaro V, Tulisi S, et al. A 45.5fs-integrated-random-jitter and -75dBc-integer-boundary-spur BiCMOS fractional-N PLL with suppression of fractional, horn, and wandering spurs. 2024 IEEE International Solid-State Circuits Conference (ISSCC), 2024, 194 doi: 10.1109/ISSCC49657.2024.10454462[5] Hung C C, Shen C H, Lin C L, et al. A fractional-N PLL with 34fsrms jitter and −255.5dB FoM based on a multipath feedback technique. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 328 doi: 10.1109/ISSCC49661.2025.10904550[6] Lim C C, Ramiah H, Yin J, et al. An inverse-class-F CMOS oscillator with intrinsic-high-Q first harmonic and second harmonic resonances. IEEE J Solid State Circuits, 2018, 53(12), 3528 doi: 10.1109/JSSC.2018.2875099[7] Xu T L, Zhong S K, Yin J, et al. A 6-to-7.5-GHz 54-fsrms jitter type-II reference-sampling PLL featuring a gain-boosting phase detector for in-band phase-noise reduction. IEEE Trans Circuits Syst I Regul Pap, 2022, 69(12), 4774 doi: 10.1109/TCSI.2022.3201939[8] Gao X, Klumperink E A M, Bohsali M, et al. A low noise sub-sampling PLL in which divider noise is eliminated and PD/CP noise is not multiplied by N². IEEE J Solid State Circuits, 2009, 44(12), 3253 doi: 10.1109/JSSC.2009.2032723[9] Gao X, Burg O, Wang H S, et al. A 2.7-to-4.3GHz, 0.16psrms-jitter, −246.8dB-FOM, digital fractional-N sampling PLL in 28nm CMOS. 2016 IEEE International Solid-State Circuits Conference (ISSCC), 2016, 174 doi: 10.1109/ISSCC.2016.7417963[10] Wu W H, Yao C W, Godbole K, et al. A 28-nm 75-fsrms analog fractional-N sampling PLL with a highly linear DTC incorporating background DTC gain calibration and reference clock duty cycle correction. IEEE J Solid State Circuits, 2019, 54(5), 1254 doi: 10.1109/JSSC.2019.2899726[11] Gao X. Sampling-based PLLs: a brief overview and tutorial. IEEE Solid-State Circuits Mag, 2025, 17(1), 46 doi: 10.1109/MSSC.2024.3501215[12] Kim J, Jo Y, Park H, et al. A 12.8–15.0-GHz low-jitter fractional-N subsampling PLL using a voltage-domain quantization-error cancellation. IEEE J Solid-State Circuits, 2024, 59(2), 424 doi: 10.1109/JSSC.2023.3297618[13] Tasca D, Zanuso M, Marzin G, et al. A 2.9–4.0-GHz fractional-N digital PLL with Bang-Bang phase detector and 560-fsrms integrated jitter at 4.5-mW power. IEEE J Solid-State Circuits, 2011, 46(12), 2745 doi: 10.1109/JSSC.2011.2162917[14] Levantino S, Marzin G, Samori C. An adaptive pre-distortion technique to mitigate the DTC nonlinearity in digital PLLs. IEEE J Solid-State Circuits, 2014, 49(8), 1762 doi: 10.1109/JSSC.2014.2314436[15] Wu W H, Yao C W, Guo C K, et al. A 14-nm ultra-low jitter fractional-N PLL using a DTC range reduction technique and a reconfigurable dual-core VCO. IEEE J Solid-State Circuits, 2021, 56(12), 3756 doi: 10.1109/JSSC.2021.3111134[16] Jin G F, Feng F, Chen W, et al. A fractional-N sampling PLL with a merged constant-slope DTC and sampling PD. IEEE J Solid-State Circuits, 2024, 59(8), 2407 doi: 10.1109/JSSC.2024.3358564[17] Ru J Z, Palattella C, Geraedts P, et al. A high-linearity digital-to-time converter technique: Constant-slope charging. IEEE J Solid-State Circuits, 2015, 50(6), 1412 doi: 10.1109/JSSC.2015.2414421[18] Li H R, Li J G, Jiang X Y, et al. A 27GHz fractional-N sub-sampling PLL achieving 57.9 fsrms jitter, −249.7dB FoM, and 1.98μs locking time using polarity-reversible SSPD. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 1 doi: 10.1109/ISSCC49661.2025.10904556[19] Shen X, Zhang Z, Li Y, et al. A 0.65V-VDD 10.4-to-11.8GHz fractional-N sampling PLL achieving 73.8 fsrms jitter, −271.5dB FoMN, and –61 dBc in-band fractional spur in 40nm CMOS. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 338 doi: 10.1109/ISSCC49661.2025.10904612[20] Rossoni M, Dartizio S M, Tesolin F, et al. A low-jitter fractional-N digital PLL adopting a reverse-concavity variable-slope DTC. IEEE J Solid-State Circuits, 2025, 60(6), 2122 doi: 10.1109/JSSC.2024.3469556[21] Chae M, Jang S, Hwanq C, et al. A 65 fsrms-jitter and -272dB-FoMjitter, N 10.1GHz fractional-N digital PLL with a quantization-error-compensating BBPD and an orthogonal-polynomial LMS calibration. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 554 doi: 10.1109/ISSCC49661.2025.10904741[22] Dartizio S M, Buccoleri F, Tesolin F, et al. A fractional-N Bang-Bang PLL based on type-II gear shifting and adaptive frequency switching achieving 68.6 fs-rms-total-integrated-jitter and 1.56 μs locking time. IEEE J Solid-State Circuits, 2022, 57(12), 3538 doi: 10.1109/JSSC.2022.3206955[23] Li H R, Xu T L, Meng X, et al. A 23.2-to-26GHz low-jitter fast-locking sub-sampling PLL based on a function-reused VCO-buffer and a type-I FLL with rapid phase alignment. IEEE J Solid-State Circuits, 2024, 59(12), 3952 doi: 10.1109/JSSC.2024.3458463[24] Liu H Z, Deng W, Jia H K, et al. An ultra-low-jitter fast-hopping fractional-N PLL with LC DTC and hybrid-proportional paths. IEEE J Solid-State Circuits, 2025, 60(3), 785 doi: 10.1109/JSSC.2024.3514870[25] Liu H Z, Deng W, Jia H K, et al. A 0.18-µs-locking-time fractional-N PLL with stochastic gradient descent tuning curve fitting, initial phase error zeroing, and random DSM achieving 44.4-fs jitter at near-integer channel. 2025 IEEE Custom Integrated Circuits Conference (CICC), 2025, 1 doi: 10.1109/CICC63670.2025.10982962[26] Zhang H M, Zhu Y Y, Osada M, et al. A 96fsrms-jitter, –70.6dBc fractional-spur cascaded PLL employing two MMDs with shared DSM for quantization noise cancellation. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 1 doi: 10.1109/ISSCC49661.2025.10904516[27] Yang D H, Murphy D, Darabi H, et al. A harmonic-mixing PLL architecture for millimeter-wave application. IEEE J Solid-State Circuits, 2022, 57(12), 3552 doi: 10.1109/JSSC.2022.3209614 -

Proportional views

Jun Yin received the B.Sc. and the M.Sc. degrees in Microelectronics from Peking University, Beijing, China, in 2004 and 2007, respectively, and the Ph.D. degree in Electronic and Computer Engineering (ECE) from Hong Kong University of Science and Technology (HKUST), Hong Kong, China, in 2013. He is currently an Associate Professor at the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau (UM), Macao, China. His research interests include integrated circuits (ICs) for high-speed communications and low-power IoT applications.

Jun Yin received the B.Sc. and the M.Sc. degrees in Microelectronics from Peking University, Beijing, China, in 2004 and 2007, respectively, and the Ph.D. degree in Electronic and Computer Engineering (ECE) from Hong Kong University of Science and Technology (HKUST), Hong Kong, China, in 2013. He is currently an Associate Professor at the State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau (UM), Macao, China. His research interests include integrated circuits (ICs) for high-speed communications and low-power IoT applications.

DownLoad:

DownLoad: