| Citation: |

Bingrui Li, Zongnan Wang, Xiyuan Tang. High-precision ADC design techniques in ISSCC 2025[J]. Journal of Semiconductors, 2025, 46(7): 070204. doi: 10.1088/1674-4926/25050012

****

B R Li, Z N Wang, and X Y Tang, High-precision ADC design techniques in ISSCC 2025[J]. J. Semicond., 2025, 46(7), 070204 doi: 10.1088/1674-4926/25050012

|

High-precision ADC design techniques in ISSCC 2025

DOI: 10.1088/1674-4926/25050012

CSTR: 32376.14.1674-4926.25050012

More Information-

References

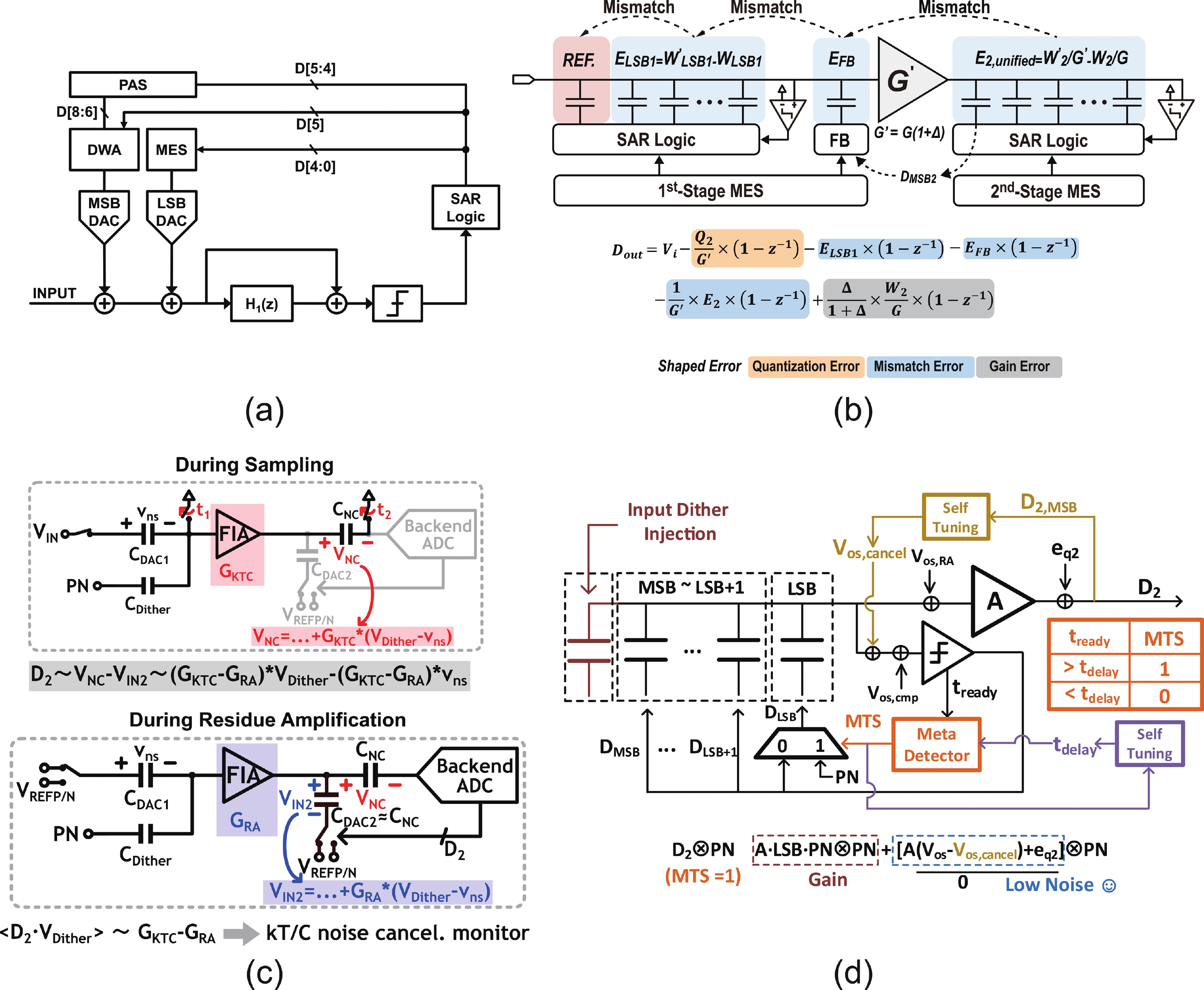

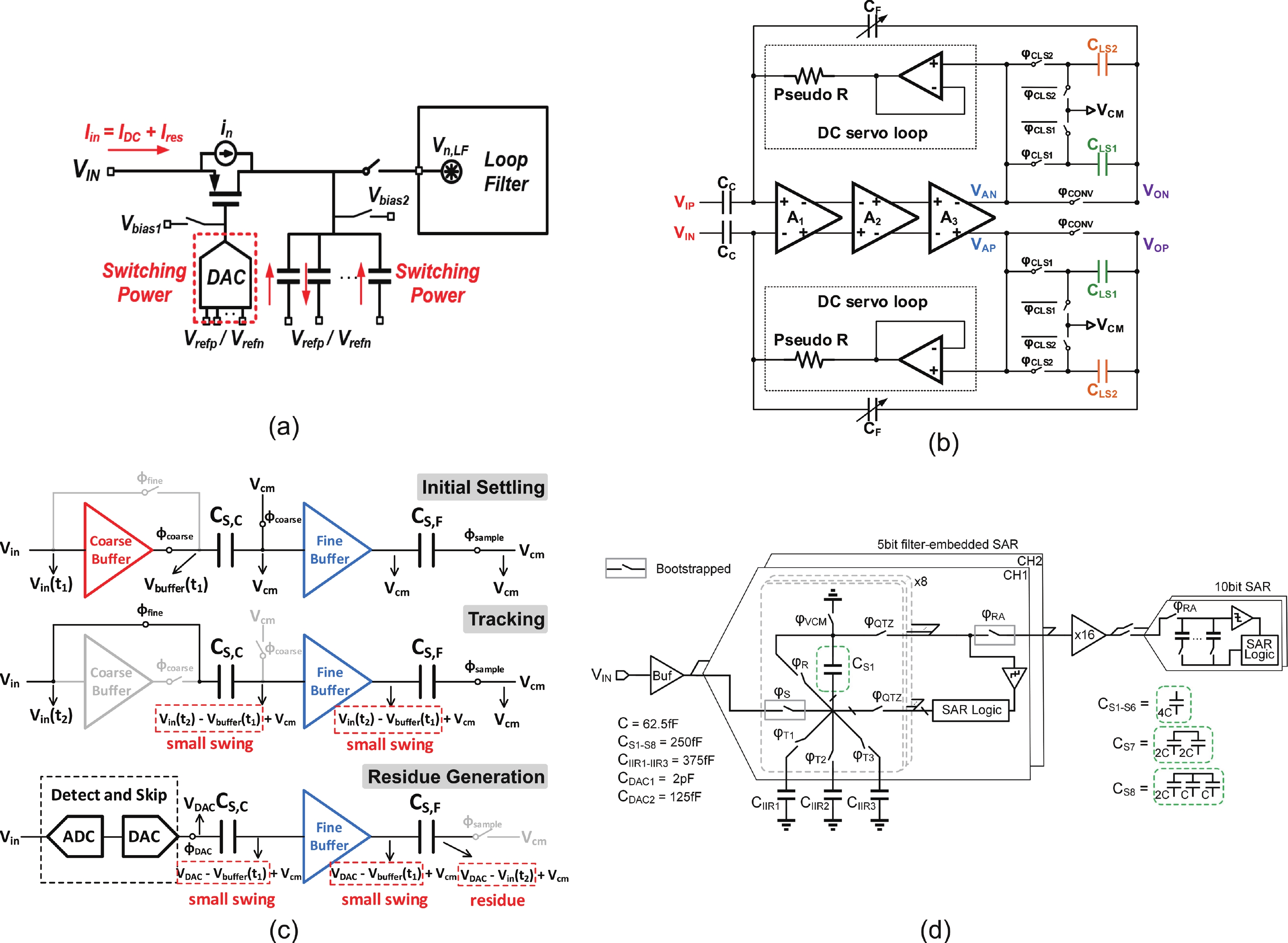

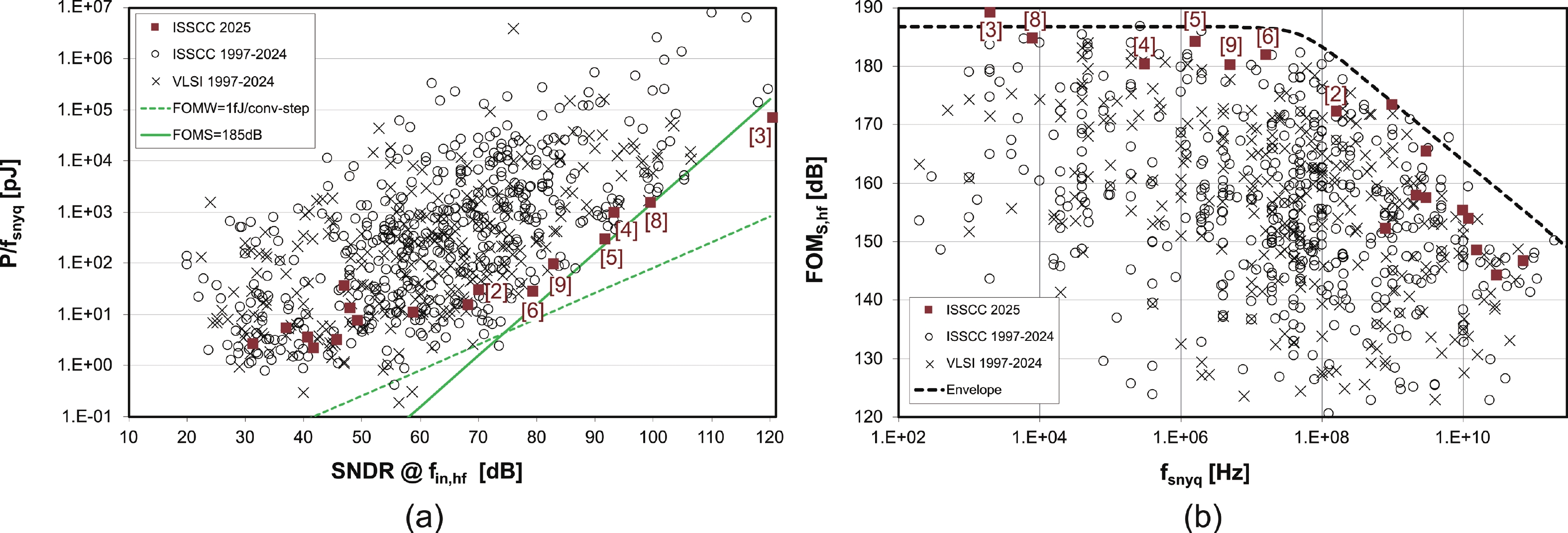

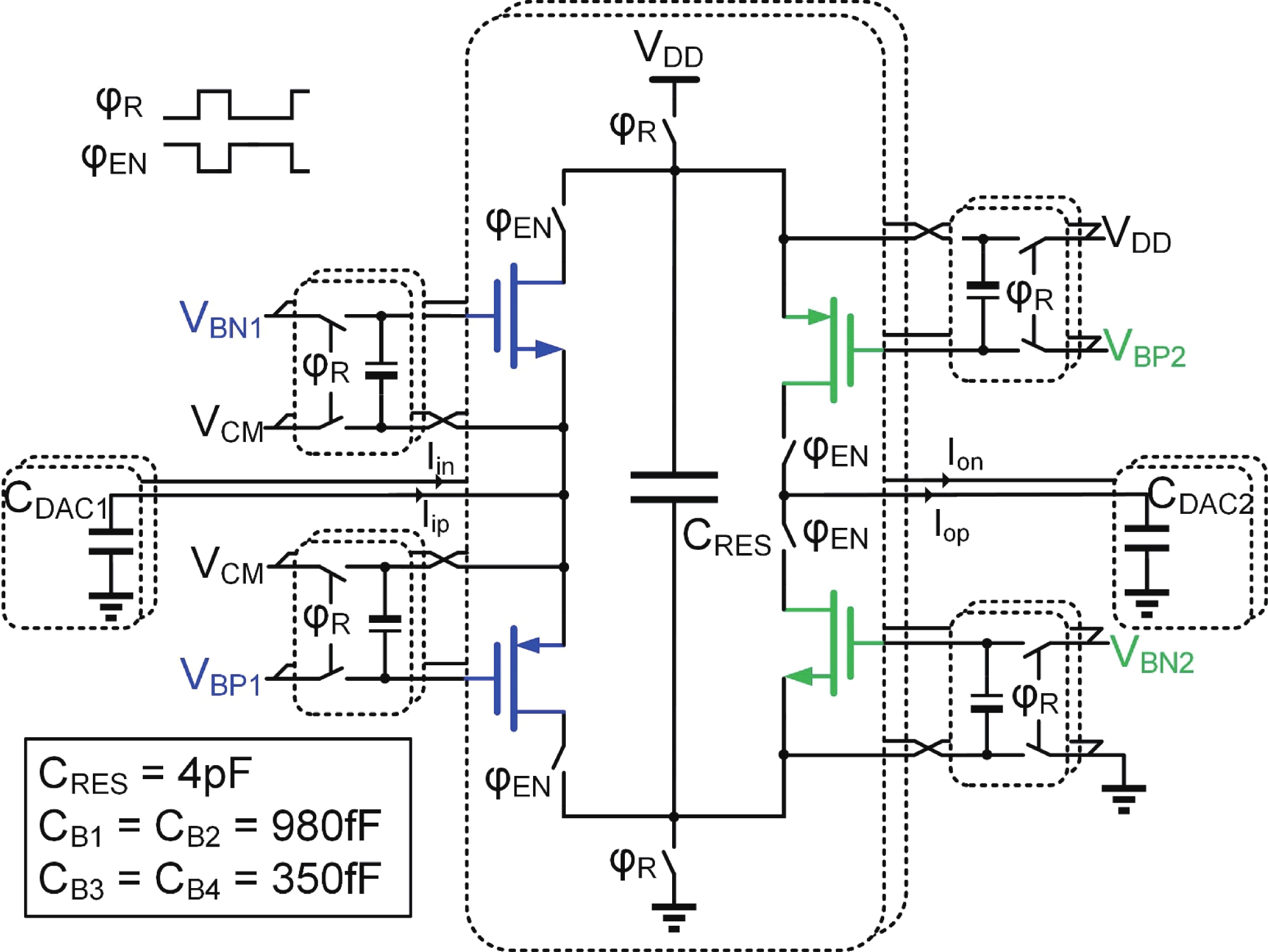

[1] Dolev N, Kramer M, Murmann B. A 12-bit, 200-MS/s, 11.5-mW pipeline ADC using a pulsed bucket brigade front-end. 2013 Symposium on VLSI Circuits, 2013, C98[2] Huang S Y, Zhang Z S, He X Y, et al. A 70dB SNDR 80MHz BW filter-embedded pipeline-SAR ADC achieving 172dB FoMs with progressive conversion and floating-charge-transfer amplifier. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 318 doi: 10.1109/ISSCC49661.2025.10904746[3] Zhao H, Zhang X H, Deng Q J, et al. A fully dynamic noise-shaping SAR ADC achieving 120dB SNDR and 189dB FoMs in 1kHz BW. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 306 doi: 10.1109/ISSCC49661.2025.10904778[4] Gao J H, Luan Y H, Ye S Y, et al. A 93.3dB SNDR, 180.4dB FoMs calibration-free noise-shaping pipelined-SAR ADC with cross-stage gain-mismatch-error-shaping technique and negative-R-assisted residue integrator. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 310 doi: 10.1109/ISSCC49661.2025.10904557[5] Wang Z N, Li B R, Tang J J, et al. A 184.8dB-FoMs 1.6MS/s incremental noise-shaping pipeline ADC with single-amplification-based kT/C noise cancellation technique. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 1 doi: 10.1109/ISSCC49661.2025.10904507[6] Chen Z Y, Ye S Y, Gao J H, et al. An easy-drive 16MS/s pipelined-SAR ADC using split coarse-fine input-buffer-sampling scheme and fast robust background inter-stage gain calibration. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 1 doi: 10.1109/ISSCC49661.2025.10904526[7] Zhou Y, Xu B W, Chiu Y. A 12 bit 160 MS/s two-step SAR ADC with background bit-weight calibration using a time-domain proximity detector. IEEE J Solid State Circuits, 2015, 50(4), 920 doi: 10.1109/JSSC.2014.2384025[8] Luan Y H, Xu X H, Gao J H, et al. A 12.2μW 99.6dB-SNDR 184.8dB-FOMs DT zoom PPD ΔΣM with gain-embedded bootstrapped sampler. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 308 doi: 10.1109/ISSCC49661.2025.10904732[9] Ye S Y, Cui J J, Gao J H, et al. A rail-to-rail 3rd-order noise-shaping SAR ADC achieving 105.4dB SFDR with integrated input buffer using continuous-time correlated level shifting. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025, 314 doi: 10.1109/ISSCC49661.2025.10904773[10] Gregoire B R, Moon U K. An over-60 dB true rail-to-rail performance using correlated level shifting and an opamp with only 30 dB loop gain. IEEE J Solid State Circuits, 2008, 43(12), 2620 doi: 10.1109/JSSC.2008.2006312[11] Lin D T, Li L, Farahani S, et al. A flexible 500MHz to 3.6GHz wireless receiver with configurable DT FIR and IIR filter embedded in a 7b 21MS/s SAR ADC. IEEE Custom Integrated Circuits Conference 2010, 2010, 1 doi: 10.1109/CICC.2010.5617620[12] Murmann B. ADC performance survey 1997-2024. [Online] Available: https://github.com/bmurmann/ADC-survey -

Proportional views

Bingrui Li received the B.S. degree from Yuanpei College at Peking University, Beijing, China, in 2024. He is currently pursuing the Ph.D. degree with the Institute for Artificial Intelligence and School of Integrated Circuits, Peking University, Beijing, China. His research interests include sensor interfaces, analog and mixed-signal integrated circuits.

Bingrui Li received the B.S. degree from Yuanpei College at Peking University, Beijing, China, in 2024. He is currently pursuing the Ph.D. degree with the Institute for Artificial Intelligence and School of Integrated Circuits, Peking University, Beijing, China. His research interests include sensor interfaces, analog and mixed-signal integrated circuits. Zongnan Wang received the B.S. degree from the school of microelectronic science and engineering, University of Electronic Science and Technology of China, Chengdu, China, in 2022. He is currently pursuing the Ph.D. degree with the Institute for Artificial Intelligence and School of Integrated Circuits, Peking University, Beijing, China. His research interests include analog and mixed-signal integrated circuits.

Zongnan Wang received the B.S. degree from the school of microelectronic science and engineering, University of Electronic Science and Technology of China, Chengdu, China, in 2022. He is currently pursuing the Ph.D. degree with the Institute for Artificial Intelligence and School of Integrated Circuits, Peking University, Beijing, China. His research interests include analog and mixed-signal integrated circuits. Xiyuan Tang received the B.Sc. degree (Hons.) from the School of Microelectronics, Shanghai Jiao Tong University, Shanghai, China, in 2012, and the M.S. and Ph.D. degree in electrical engineering from The University of Texas at Austin, Austin, TX, USA, in 2014 and 2019 respectively. He is currently an Assistant Professor at Peking University, Beijing, China. He was a Design Engineer with Silicon Laboratories, Austin, TX from 2014 to 2017, where he was involved in the RF receiver design. From 2019−2021, he was a postdoctoral researcher at the University of Texas at Austin, Austin, TX. His research interests include data converters, low-power mixed-signal circuits, and emerging computing. Dr. Tang serves on the Technical Program Committees (TPC) of ISSCC and ASSCC. He also serves as an associate editor for IEEE Solid-State Circuits Letters. He was a recipient of IEEE Solid-State Circuits Society Rising Stars in 2020, Best Paper Award at Silicon Labs Tech Symposium in 2016, National Scholarship in 2011, and Shanghai Scholarship in 2010.

Xiyuan Tang received the B.Sc. degree (Hons.) from the School of Microelectronics, Shanghai Jiao Tong University, Shanghai, China, in 2012, and the M.S. and Ph.D. degree in electrical engineering from The University of Texas at Austin, Austin, TX, USA, in 2014 and 2019 respectively. He is currently an Assistant Professor at Peking University, Beijing, China. He was a Design Engineer with Silicon Laboratories, Austin, TX from 2014 to 2017, where he was involved in the RF receiver design. From 2019−2021, he was a postdoctoral researcher at the University of Texas at Austin, Austin, TX. His research interests include data converters, low-power mixed-signal circuits, and emerging computing. Dr. Tang serves on the Technical Program Committees (TPC) of ISSCC and ASSCC. He also serves as an associate editor for IEEE Solid-State Circuits Letters. He was a recipient of IEEE Solid-State Circuits Society Rising Stars in 2020, Best Paper Award at Silicon Labs Tech Symposium in 2016, National Scholarship in 2011, and Shanghai Scholarship in 2010.

DownLoad:

DownLoad: