| Citation: |

Zhentao Ni, Dajing Bian, Haoxiang Jiang, Xiaoming Huang, Yue Xu. A deep-junction single-photon detector with field polysilicon gate structure for increased photon detection efficiency and reduced dark count noise[J]. Journal of Semiconductors, 2025, In Press. doi: 10.1088/1674-4926/25060004

****

Z T Ni, D J Bian, H X Jiang, X M Huang, and Y Xu, A deep-junction single-photon detector with field polysilicon gate structure for increased photon detection efficiency and reduced dark count noise[J]. J. Semicond., 2025, accepted doi: 10.1088/1674-4926/25060004

|

A deep-junction single-photon detector with field polysilicon gate structure for increased photon detection efficiency and reduced dark count noise

DOI: 10.1088/1674-4926/25060004

CSTR: 32376.14.1674-4926.25060004

More Information-

Abstract

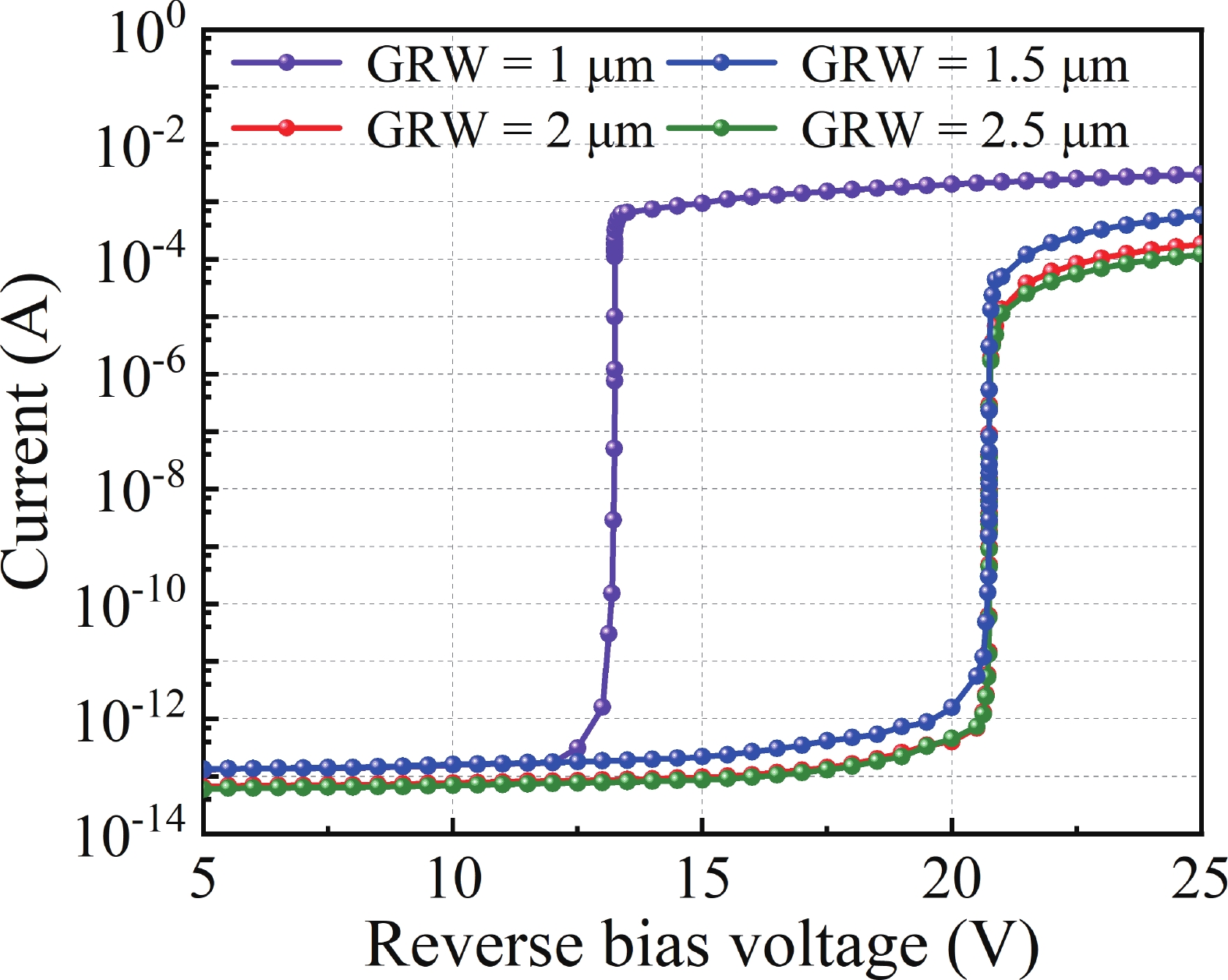

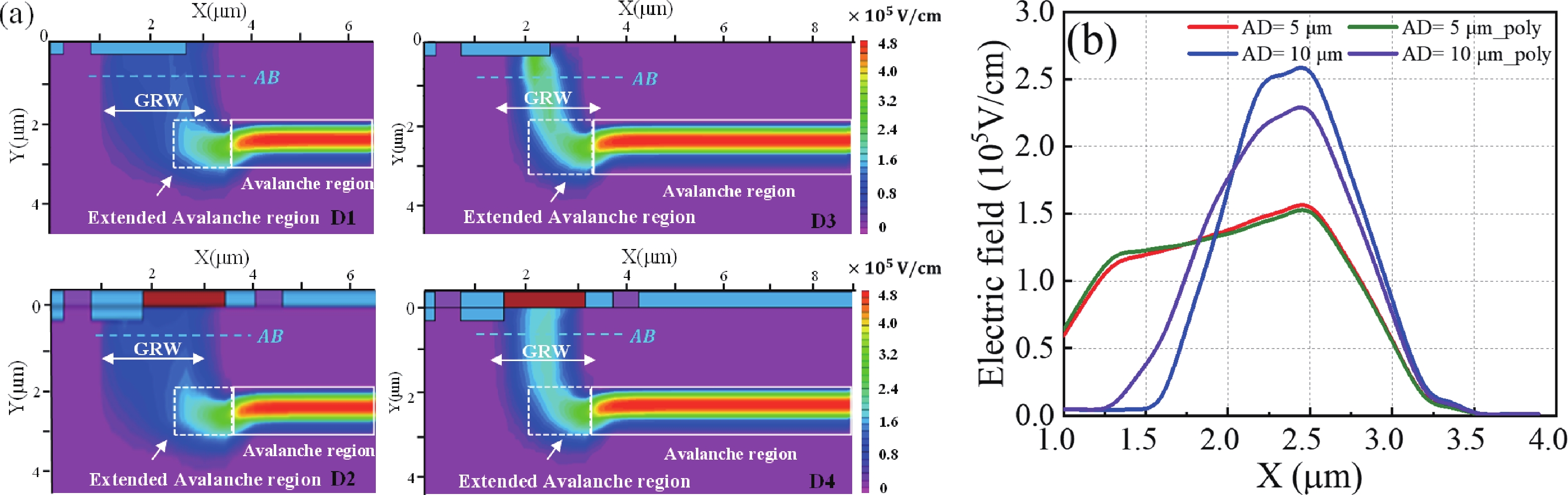

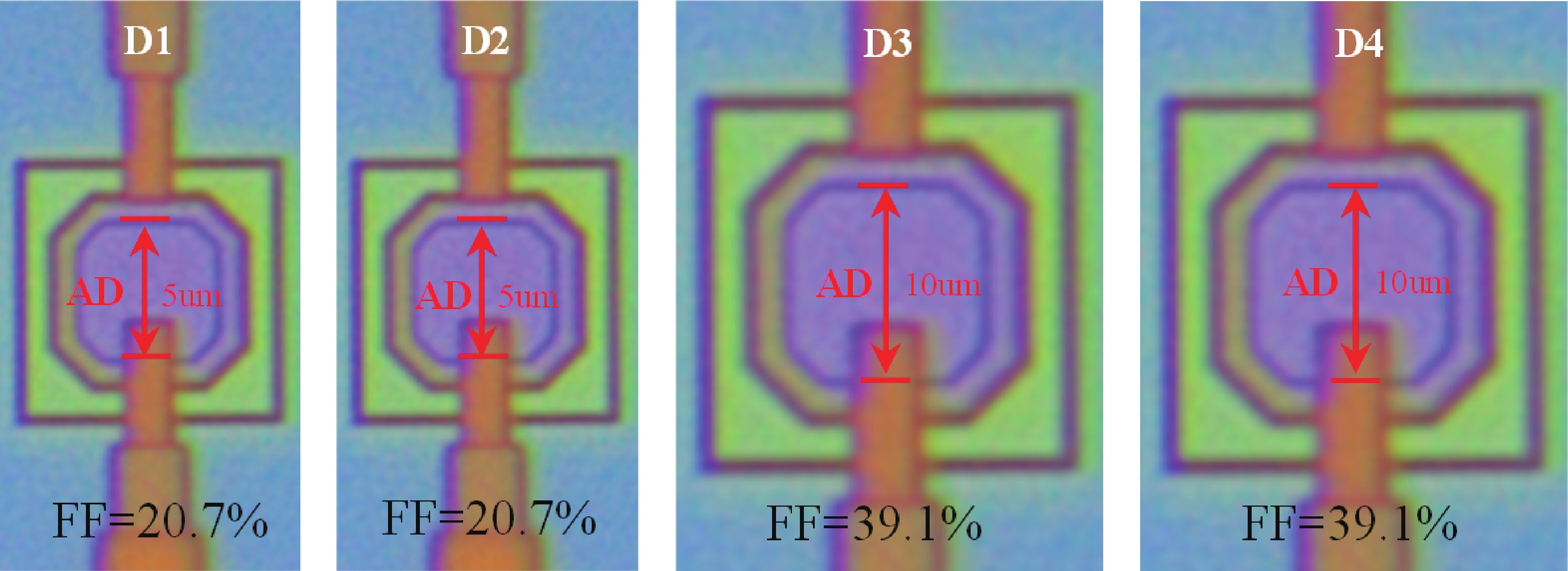

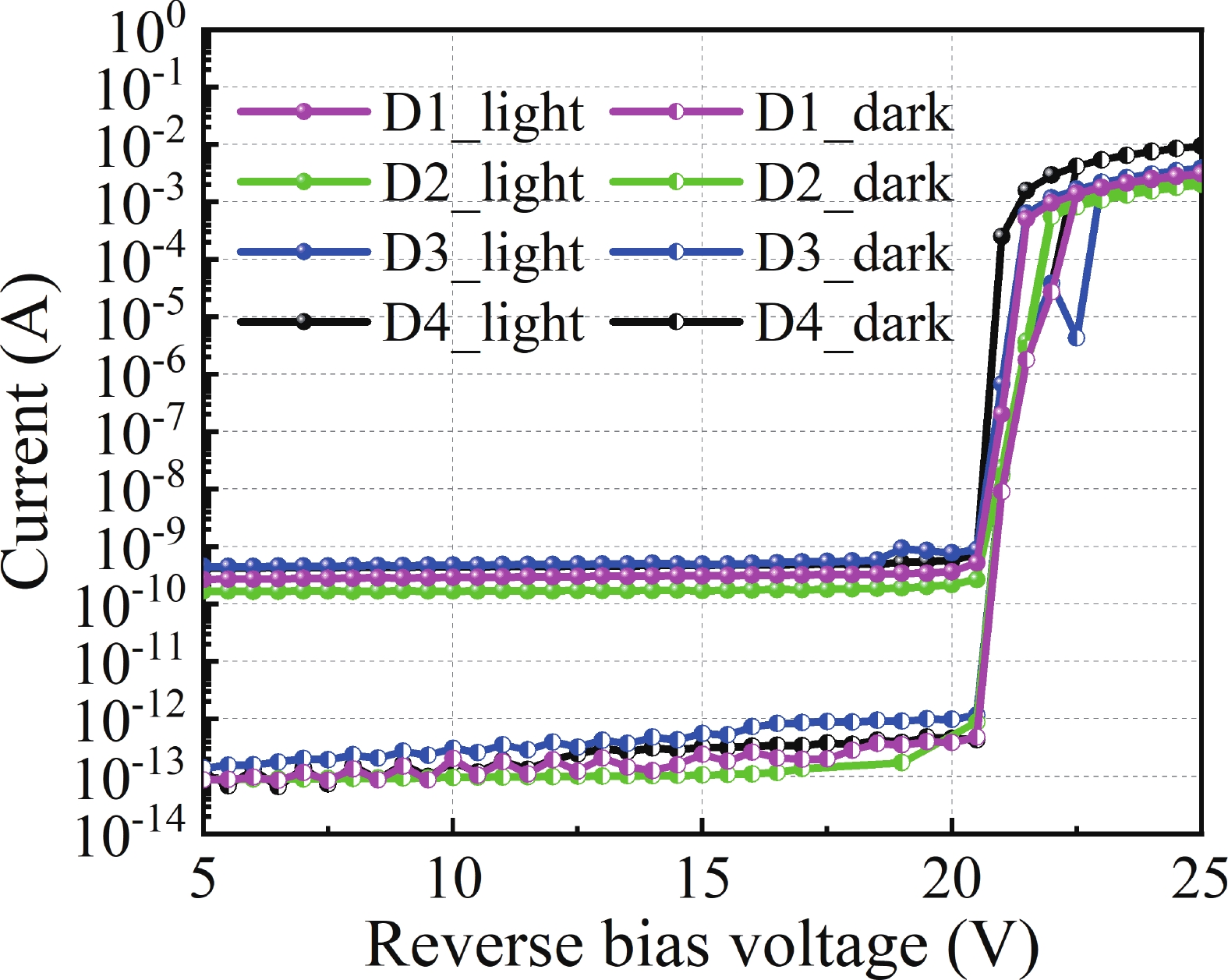

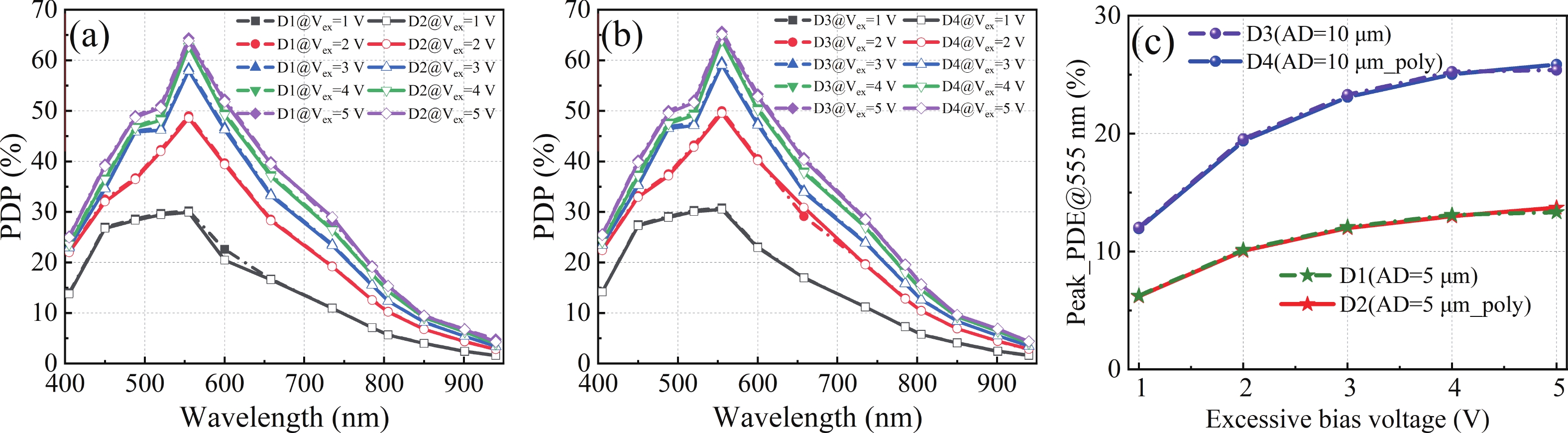

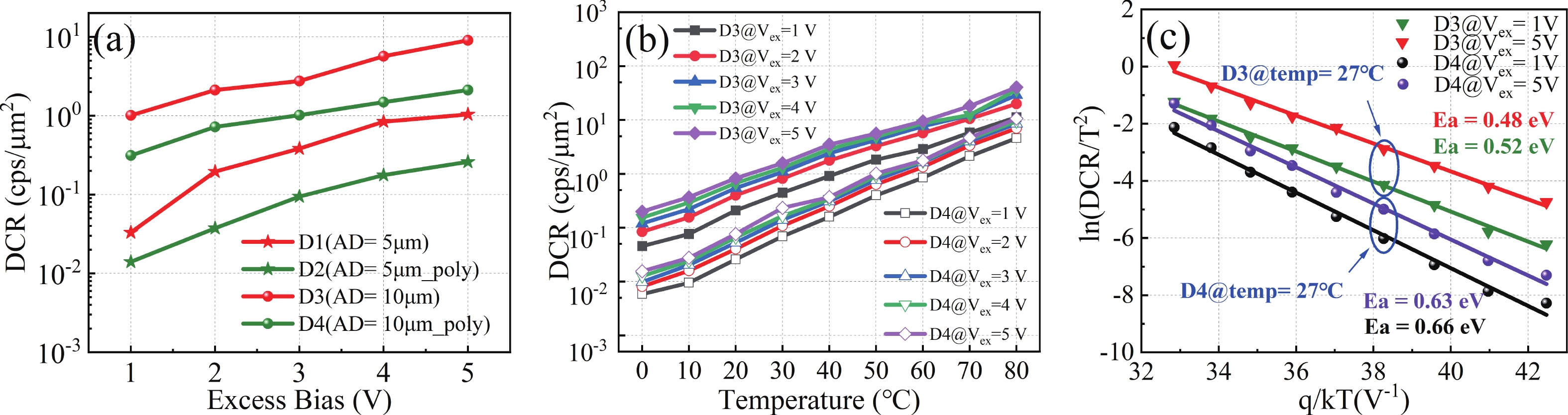

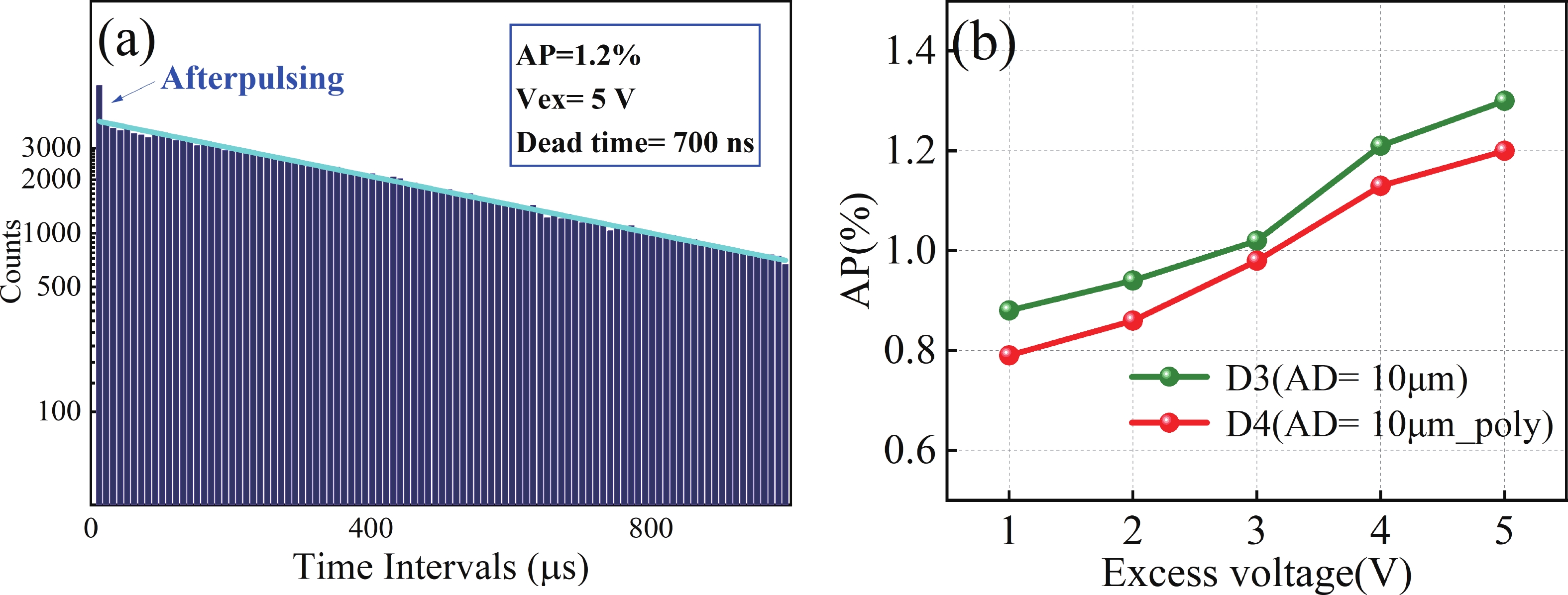

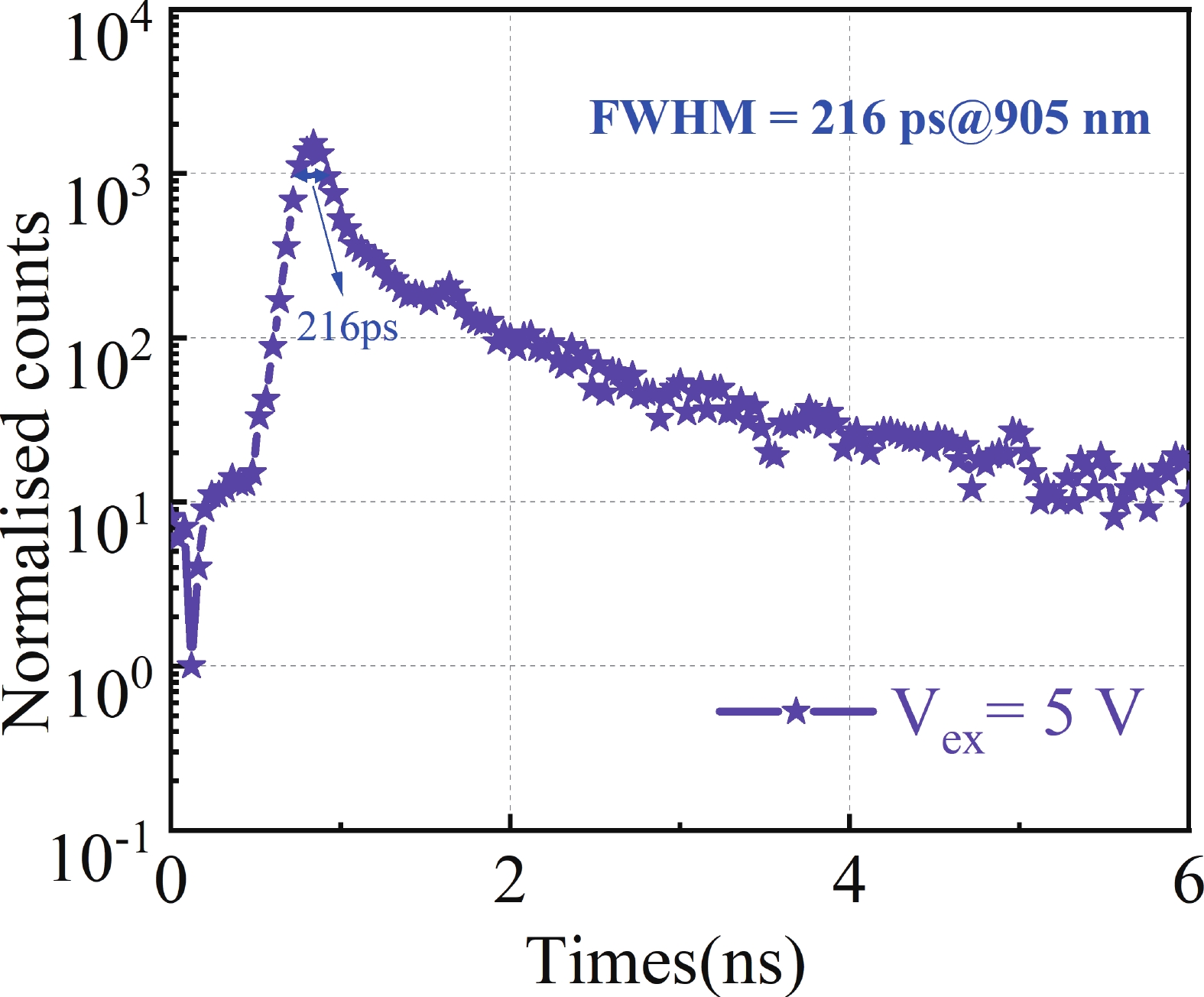

A high-sensitivity, low-noise single photon avalanche diode (SPAD) detector was presented based on a 180 nm BCD process. The proposed device utilizes a p-implant layer/high-voltage n-well (HVNW) junction to form a deep avalanche multiplication region for near-infrared (NIR) sensitivity enhancement. By optimizing the device size and electric field of the guard ring, the fill factor (FF) is significantly improved, further increasing photon detection efficiency (PDE). To solve the dark noise caused by the increasing active diameter, a field polysilicon gate structure connected to the p+ anode was investigated, effectively suppressing dark count noise by 76.6%. It is experimentally shown that when the active diameter increases from 5 to 10 μm, the FF is significantly improved from 20.7% to 39.1%, and thus the peak PDE also rises from 13.3% to 25.8%. At an excess bias voltage of 5 V, a NIR photon detection probability (PDP) of 6.8% at 905 nm, a dark count rate (DCR) of 2.12 cps/μm2, an afterpulsing probability (AP) of 1.2%, and a timing jitter of 216 ps are achieved, demonstrating excellent single photon detection performance. -

References

[1] Wayne M, Ulku A, Ardelean A, et al. A 500 × 500 dual-gate SPAD imager with 100% temporal aperture and 1 ns minimum gate length for FLIM and phasor imaging applications. IEEE Trans Electron Devices, 2022, 69(6), 2865 doi: 10.1109/TED.2022.3168249[2] Hutchings S W, Johnston N, Gyongy I, et al. A reconfigurable 3-D-stacked SPAD imager with in-pixel histogramming for flash LIDAR or high-speed time-of-flight imaging. IEEE J Solid State Circuits, 2019, 54(11), 2947 doi: 10.1109/JSSC.2019.2939083[3] Vornicu I, López-Martínez J M, Bandi F N, et al. Design of high-efficiency SPADs for LiDAR applications in 110nm CIS technology. IEEE Sens J, 2021, 21(4), 4776 doi: 10.1109/JSEN.2020.3032106[4] Katz A, Blank T, Fenigstein A, et al. Active-reset for the N P single-ended SPAD used in the NIR LiDAR receivers. IEEE Trans Electron Devices, 2019, 66(12), 5191 doi: 10.1109/TED.2019.2946015[5] Park E, Eom D, Kim J H, et al. Back-illuminated SPAD in 40 nm CIS technology achieving 56 ps timing jitter with 15 V breakdown voltage for short/mid-range LiDAR applications. 2023 International Electron Devices Meeting (IEDM), 2023, 1[6] Gebremicael K N, Rarity J G, Sibson P. Capacitive response signal cancellation for sine wave gated high-speed single photon avalanche photodiode detector. IEEE J Quantum Electron, 2021, 57(4), 4500305[7] Wen G H, Huang J, Zhang L, et al. A high-speed and high-sensitivity photon-counting communication system based on multichannel SPAD detection. IEEE Photonics J, 2021, 13(2), 7900310[8] Huang J, Li C K, Dai J S, et al. Real-time and high-speed underwater photon-counting communication based on SPAD and PPM symbol synchronization. IEEE Photonics J, 2021, 13(5), 7300209[9] Veerappan C, Charbon E. CMOS SPAD based on photo-carrier diffusion achieving PDP >40% from 440 to 580 nm at 4 V excess bias. IEEE Photonics Technol Lett, 2015, 27(23), 2445 doi: 10.1109/LPT.2015.2468067[10] Park E, Eom D, Yu M H, et al. Back-illuminated double-avalanche-region single-photon avalanche diode. IEEE J Sel Top Quantum Electron, 2024, 30(1), 3800809[11] Sun W B, Wang Y X, Liu M L, et al. A back-illuminated 4μm P+N-well single photon avalanche diode pixel array with 0.36Hz/μm2 dark count rate at 2.5 V excess bias voltage. IEEE Electron Device Lett, 2022, 43(9), 1519 doi: 10.1109/LED.2022.3196172[12] Van Sieleghem E, Karve G, De Munck K, et al. A backside-illuminated charge-focusing silicon SPAD with enhanced near-infrared sensitivity. IEEE Trans Electron Devices, 2022, 69(3), 1129 doi: 10.1109/TED.2022.3143487[13] Lindner S, Pellegrini S, Henrion Y, et al. A high-PDE, backside-illuminated SPAD in 65/40-nm 3D IC CMOS pixel with cascoded passive quenching and active recharge. IEEE Electron Device Lett, 2017, 38(11), 1547 doi: 10.1109/LED.2017.2755989[14] Jang J, Kim J, Oh S, et al. A 336 × 240 backside-illuminated 3D-stacked 7μm SPAD for LiDAR sensor with PDE 28% at 940nm and under 0.4% depth accuracy up to 10m. 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 2024, 1[15] Gyongy I, Calder N, Davies A, et al. A 256 × 256, 100-kfps, 61% fill-factor SPAD image sensor for time-resolved microscopy applications. IEEE Trans Electron Devices, 2018, 65(2), 547 doi: 10.1109/TED.2017.2779790[16] Wu J Y, Liu C H. Design and characterization of n/p-well CMOS SPAD with low dark count rate and high photon detection efficiency. IEEE Trans Electron Devices, 2023, 70(2), 582 doi: 10.1109/TED.2022.3231575[17] Lu X, Law M K, Jiang Y, et al. A 4-μm diameter SPAD using less-doped N-well guard ring in baseline 65-nm CMOS. IEEE Trans Electron Devices, 2020, 67(5), 2223 doi: 10.1109/TED.2020.2982701[18] Wang Y, Jin X L, Cao S G, et al. Design and measurement of ring-gate single photon avalanche diode with low dark count rate. IEEE Photonics J, 2020, 12(3), 6801711[19] Liu D L, Li M, Xu T, et al. Study of the influence of virtual guard ring width on the performance of SPAD detectors in 180 nm standard CMOS technology. J Semicond, 2023, 44(11), 114102 doi: 10.1088/1674-4926/44/11/114102[20] Jiang W, Scott R, Deen M J. Improved noise performance of CMOS poly gate single-photon avalanche diodes. IEEE Photonics J, 2022, 14(1), 6802208[21] Jinseok O, Chanho K, MinSun L, et al. Optimization and calibration of the single photon avalanche diode (SPAD) for integrated on-chip sensor interface in common CMOS process. 2023 IEEE Nuclear Science Symposium, Medical Imaging Conference and International Symposium on Room-Temperature Semiconductor Detectors (NSS MIC RTSD). Vancouver, BC, Canada, 2023, 1[22] Gramuglia F, Keshavarzian P, Kizilkan E, et al. Engineering breakdown probability profile for PDP and DCR optimization in a SPAD fabricated in a standard 55 nm BCD process. IEEE J Sel Top Quantum Electron, 2022, 28(2: Optical Detectors), 3802410[23] Liu Y, Fan R Q, Zhao Y H, et al. Junction-optimized SPAD with 50.6% peak PDP and 0.64 cps/μm2 DCR at 2 V excess bias voltage in 130 nm CMOS. IEEE Electron Device Lett, 2024, 45(3), 308 doi: 10.1109/LED.2024.3356123[24] Wu J Y, Liu C H. Designing a sub-20V breakdown voltage SPAD with standard CMOS technology and n/p-well structure. IEEE Photonics J, 2024, 16(2), 6800408 -

Proportional views

Zhentao Ni received his Bachelor's degree in Microelectronics Science and Engineering fr-om Guilin University of Electronic Technolo-gy, China, in 2023. He is currently a Master's student at Nanjing University of Posts and Telecommunications, China. His research foc-uses on LiDAR detection and Hall sensors.

Zhentao Ni received his Bachelor's degree in Microelectronics Science and Engineering fr-om Guilin University of Electronic Technolo-gy, China, in 2023. He is currently a Master's student at Nanjing University of Posts and Telecommunications, China. His research foc-uses on LiDAR detection and Hall sensors. Yue Xu received a PhD degree in microelectronics and solid-state electronics from Nanjing Univ-ersity, China, in 2012. He is currently a profess-or at the Nanjing University of Posts and Teleco-mmunications, Nanjing, China. His main research interests include the CMOS detector, analog-integ-rated circuit design, and device reliability.

Yue Xu received a PhD degree in microelectronics and solid-state electronics from Nanjing Univ-ersity, China, in 2012. He is currently a profess-or at the Nanjing University of Posts and Teleco-mmunications, Nanjing, China. His main research interests include the CMOS detector, analog-integ-rated circuit design, and device reliability.

DownLoad:

DownLoad: